好久发博客了,一晃一年过去了。

最近打算学习FPGA,手头有几块开发板在用,平时练练代码足够了,但是作为一只硬件狗不亲自设计一块属于自己的开发板实在说不过去。正巧博主这段时间在深入学习Cadence Allegro这款软件,顺便练练手,混个脸儿熟~这不是一举两得么!于是博主打算把设计一块开发板作为博客连载,记录开发板在设计之中的遇到的问题和没有考虑过的细节。

这是博客的第一篇:关于Altera FPGA的下载接口

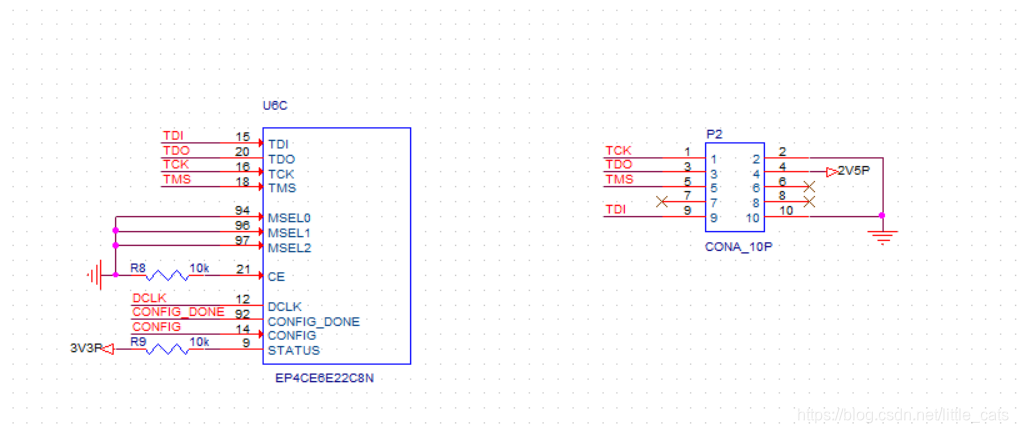

博主选用的FPGA是Altera公司(现被intel收购)的EP4CE6E22C8N,这是一款144pin的FPGA芯片,具有6K个LE,足够平时练练手了~

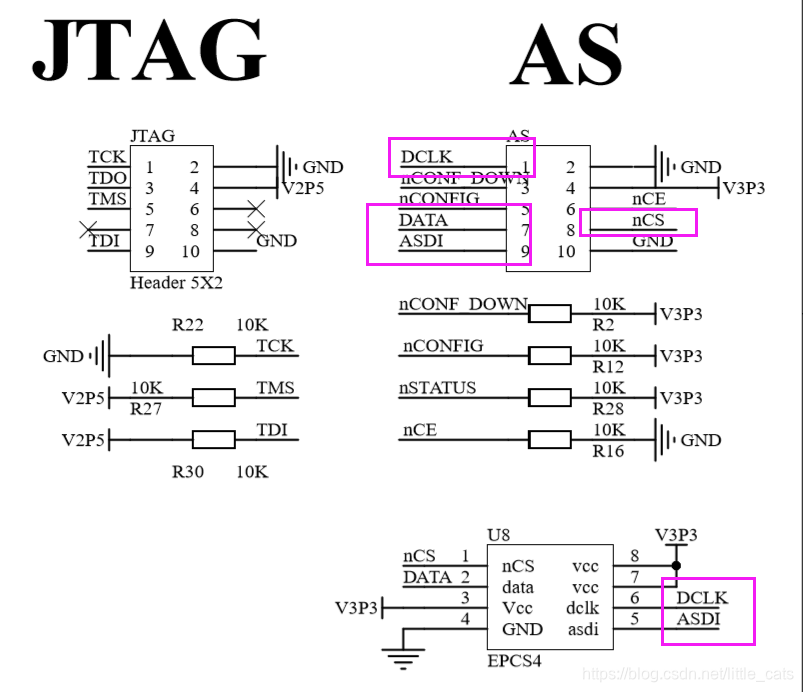

通常FPGA开发板会保留2个下载接口:JTAG接口和AS接口,对于这两个接口的区别也是显而易见的:

JTAG接口将综合好的代码直接烧录至FPGA芯片,烧写完毕即可运行,但是掉电代码就消失。

AS接口将代码直接烧录至与FPGA相连的配置芯片中,掉电则从配置芯片中重新读取运行。

当然JTAG也可以生成jic文件通过FPGA下载至配置芯片中。因此在原理图中,AS接口是与配置芯片有电气连接的

而旁边的JTAG接口则与EPCS4芯片没有直接联系。同时AS接口还与nCONFIG引脚相连,也就是说AS接口可以在烧录完毕以后拉低该引脚使FPGA初始化配置。

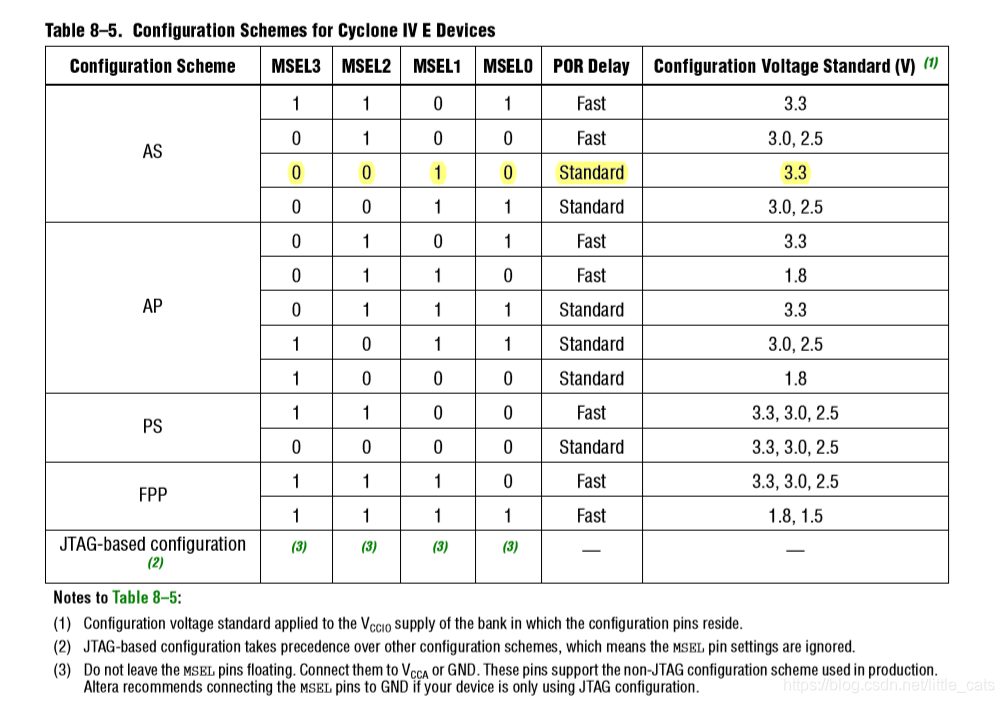

那么使用JTAG接口还是AS接口是由什么决定的呢?查阅手册博主找到了如下表格

也就是说,对于CYCLONE IV E系列FPGA来说,我们可以给MSEL[3…0]这四个管脚以不同电平来选择开启AS还是其他下载方式。对于博主用的EP4CE6E22C8N这个芯片来说没有MSEL3。

注意表格下方的注释3

如果仅使用JTAG,请勿悬空MSEL

也就是说无论MSEL配置如何,使用JTAG都是可以烧写FPGA的。于是博主放心大胆的把MSEL[2…0]都接地了…

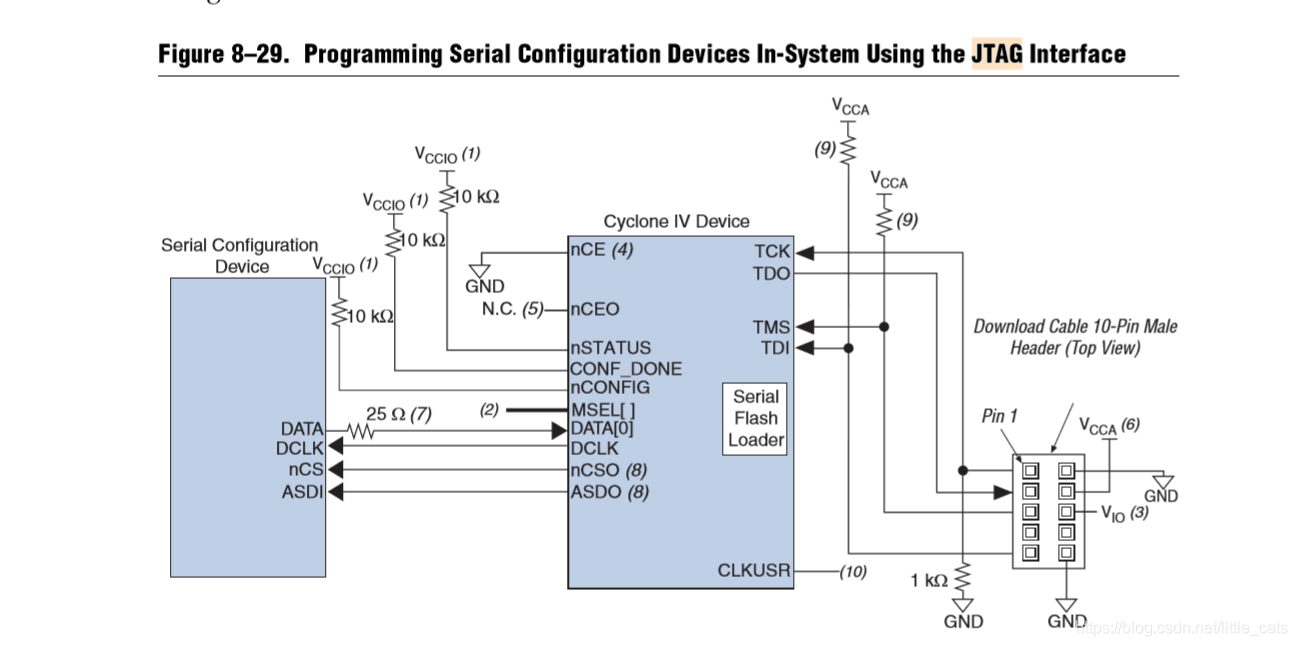

同时Altera的手册中还贴心地给出了JTAG接口的下载配置

注意右边TCK TMS TDI的上下拉电阻,按照手册推荐的方式去配置一般问题不大。

博主计划设计一款基于Altera EP4CE6E22C8N FPGA的开发板,探讨JTAG与AS接口的选择及配置,记录设计过程中的问题与细节。

博主计划设计一款基于Altera EP4CE6E22C8N FPGA的开发板,探讨JTAG与AS接口的选择及配置,记录设计过程中的问题与细节。

2218

2218

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?