或许是每个做硬件的厂商都有做软件的心,xilinx发布了他的下一个平台Vitis,也就是硬件和软件分开了(即Vivado和IDE分开了),除了启动方式和使用方法略有区别外,其他操作几乎与上一代Vivado一模一样。本文是试用这个新平台来尝尝鲜。

本来不想使用的,重装系统了,那就重新安装最新版吧,软件安装总共60多G,我的固态硬盘呐!!!!!!!!!心疼3s……

安装完成后出现了三个图标,前俩不多说,最后一个即是xilinx的独立的软件开发平台。

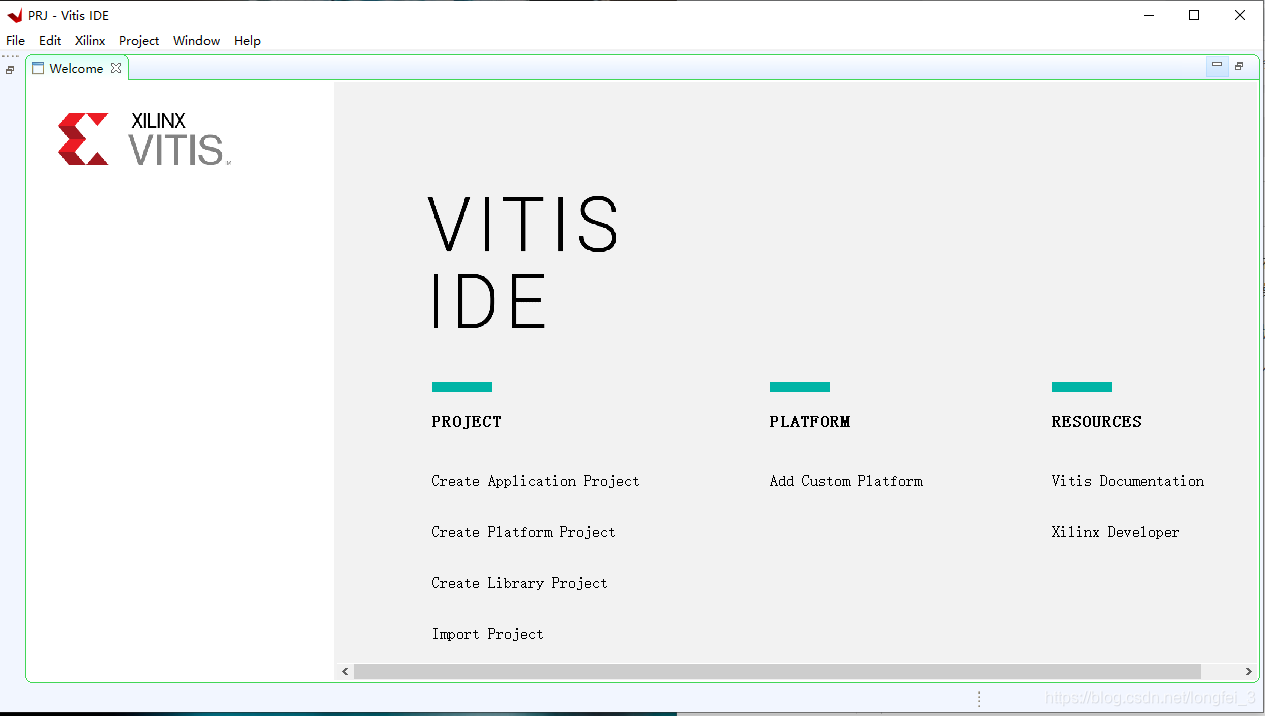

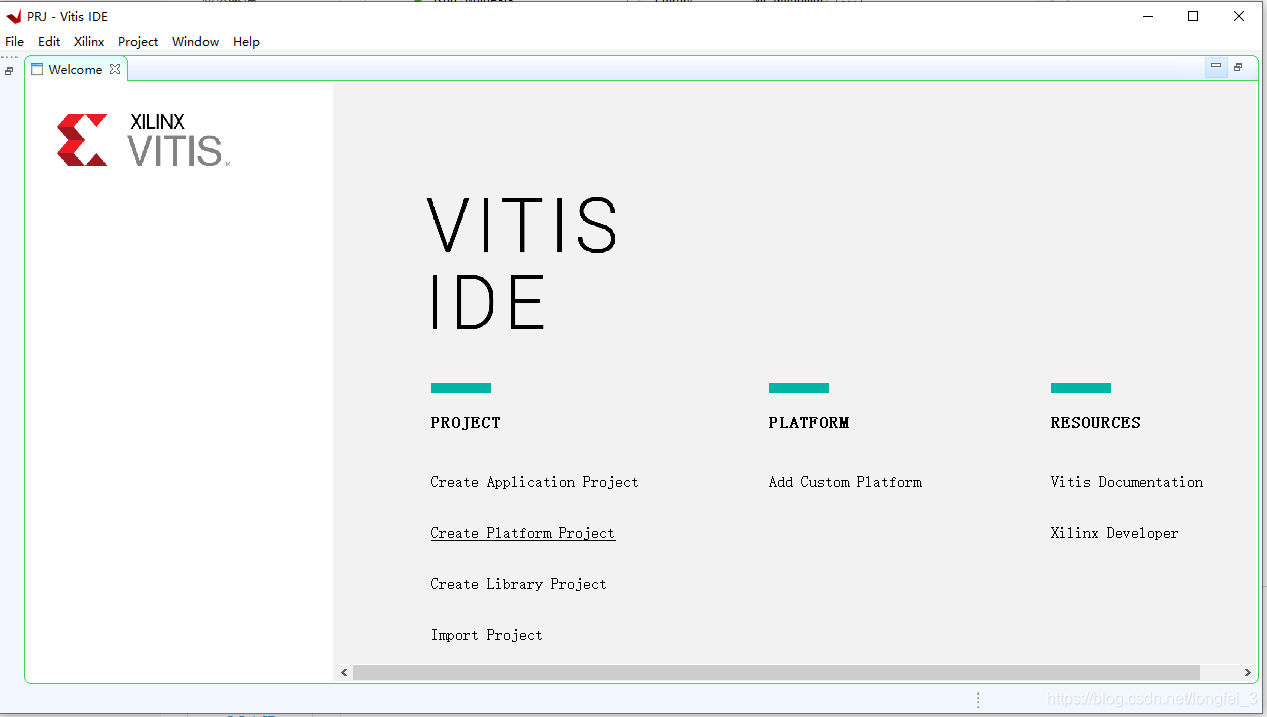

打开Vitis之后是这样的,相较于以前的IDE似乎没什么的差别

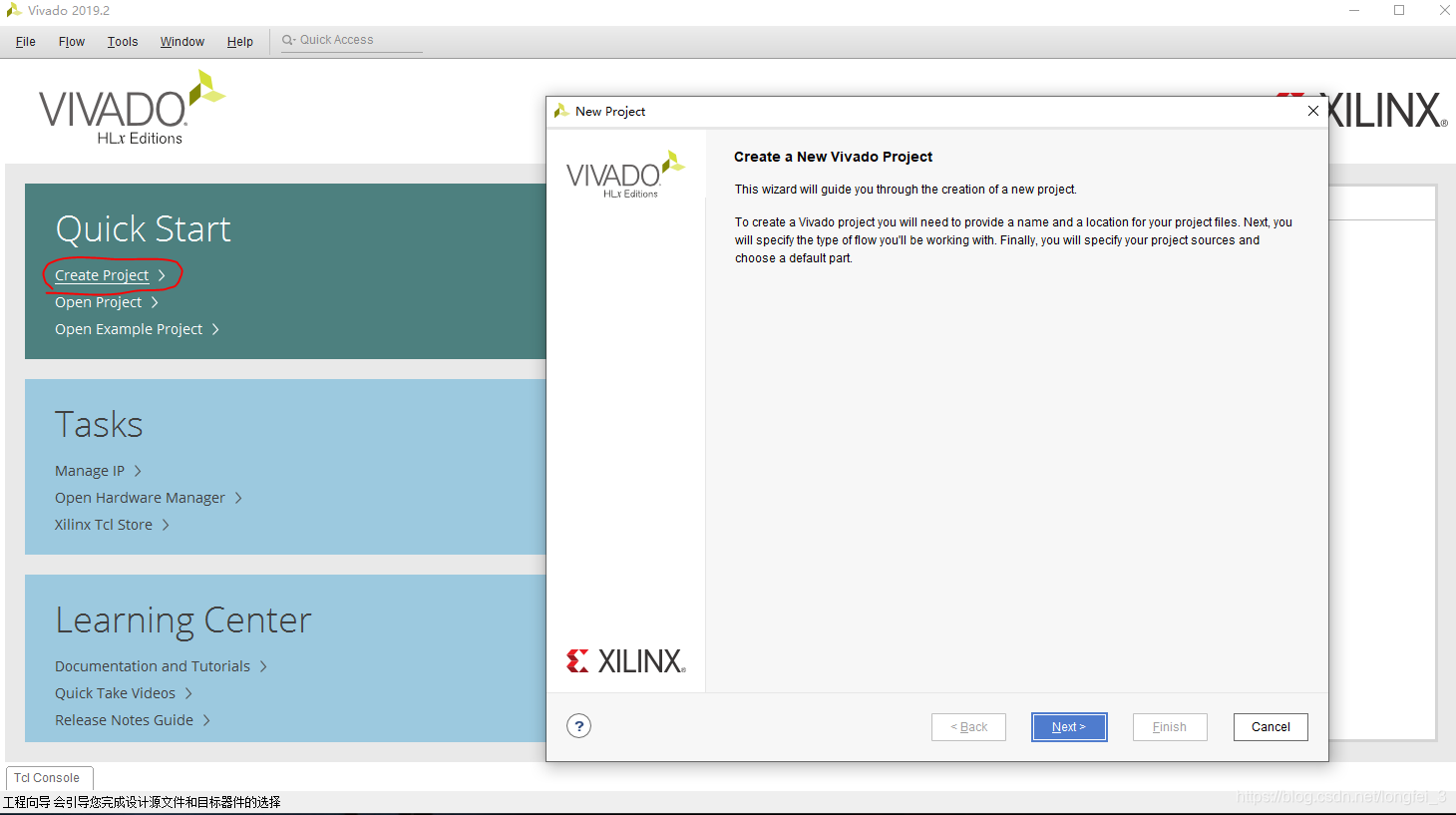

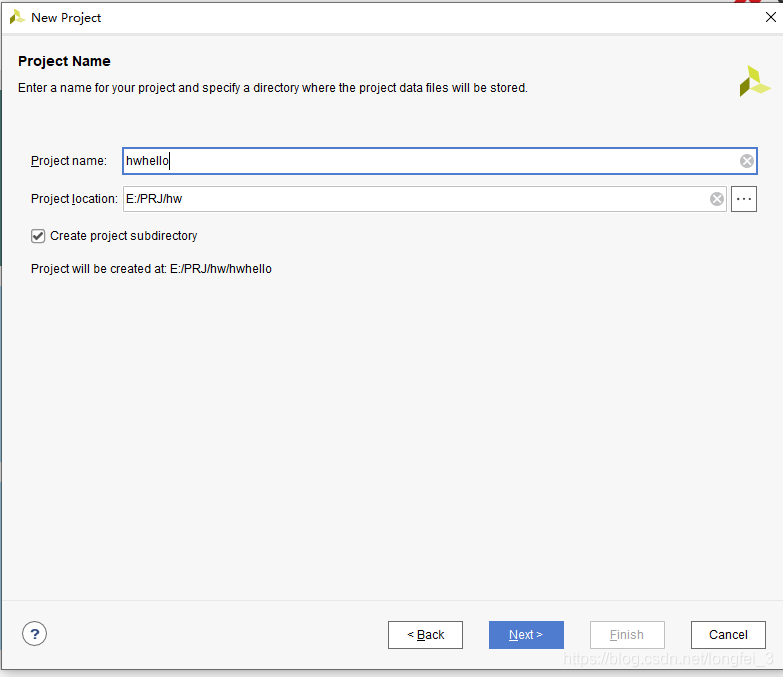

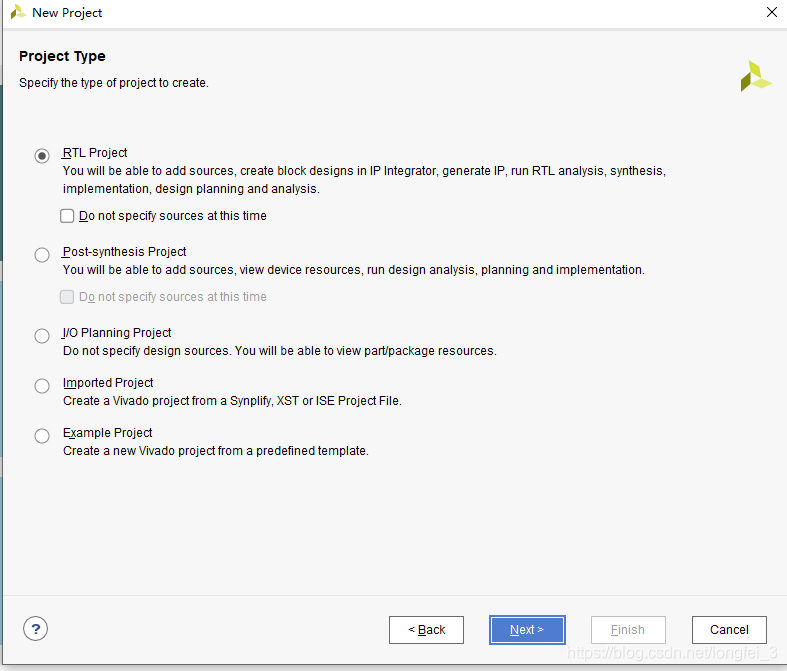

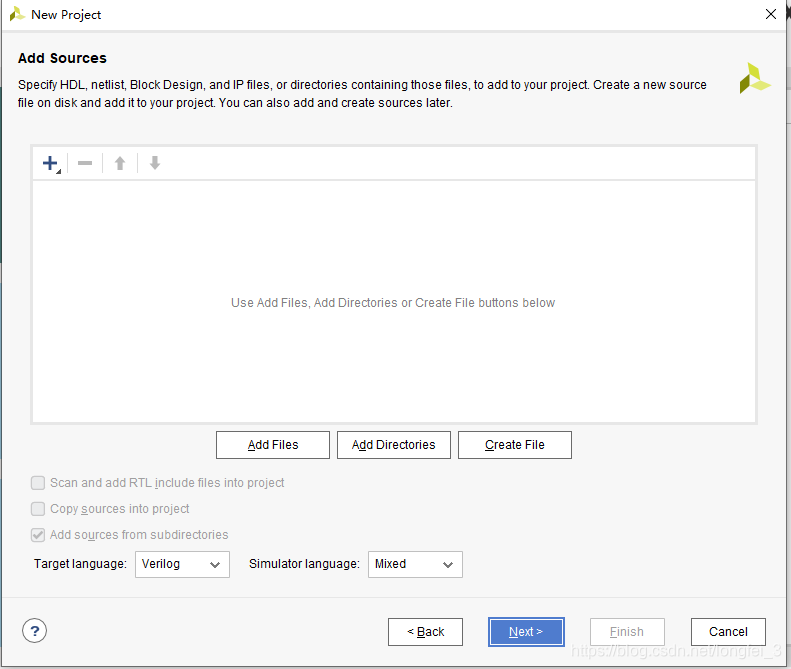

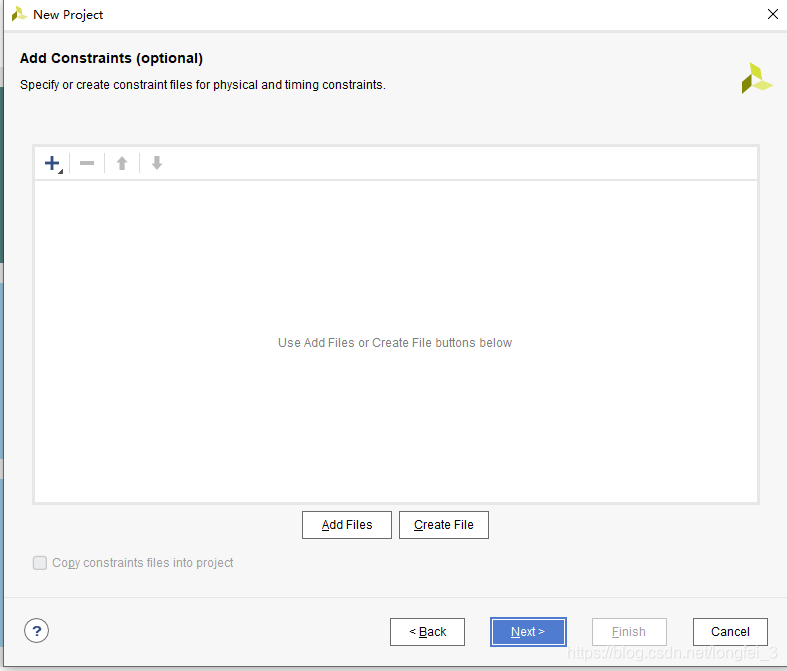

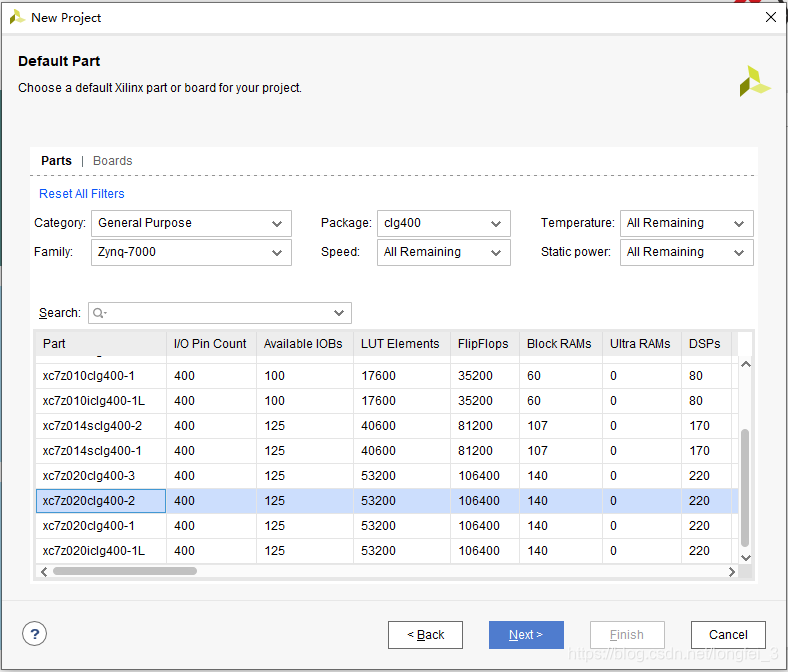

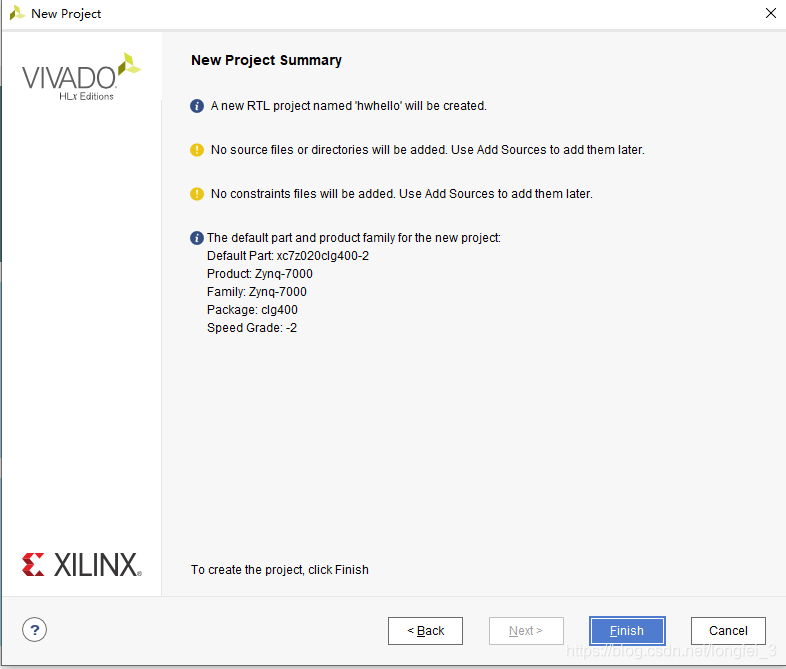

开始创建工程,这里以黑金的AX7020板子为例,打开Vivado2019.2一步步创建工程,反正就是“Next”,一直到“Finish”

空的工程创建完毕

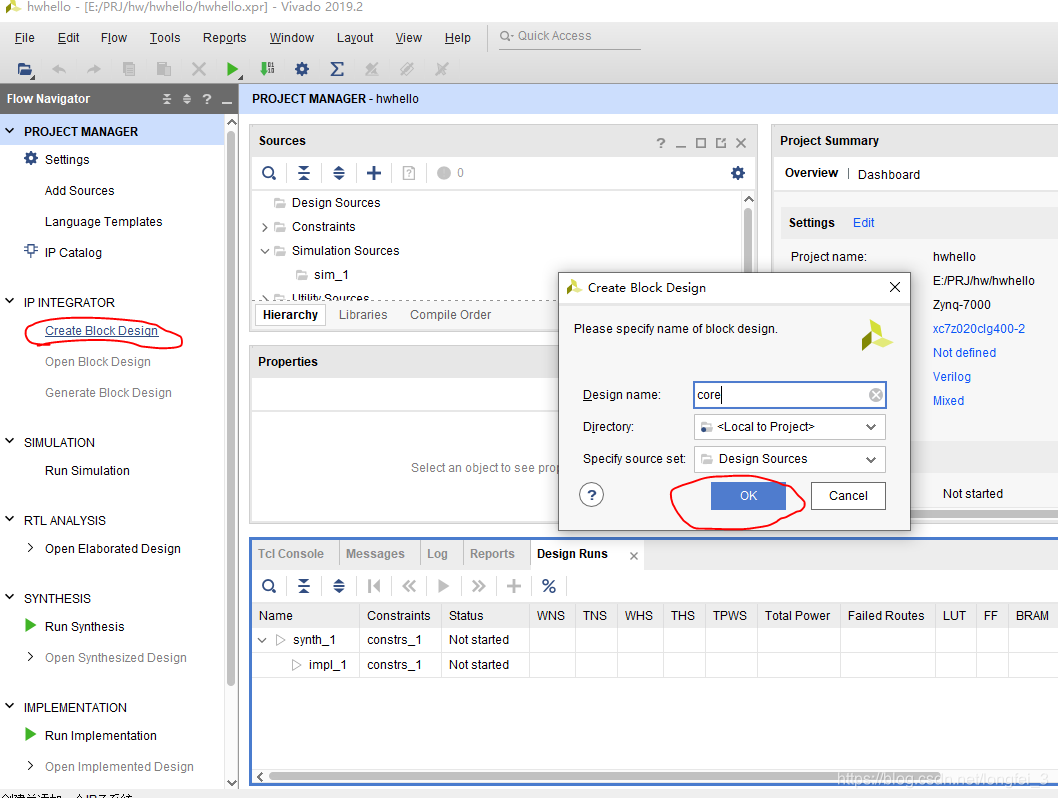

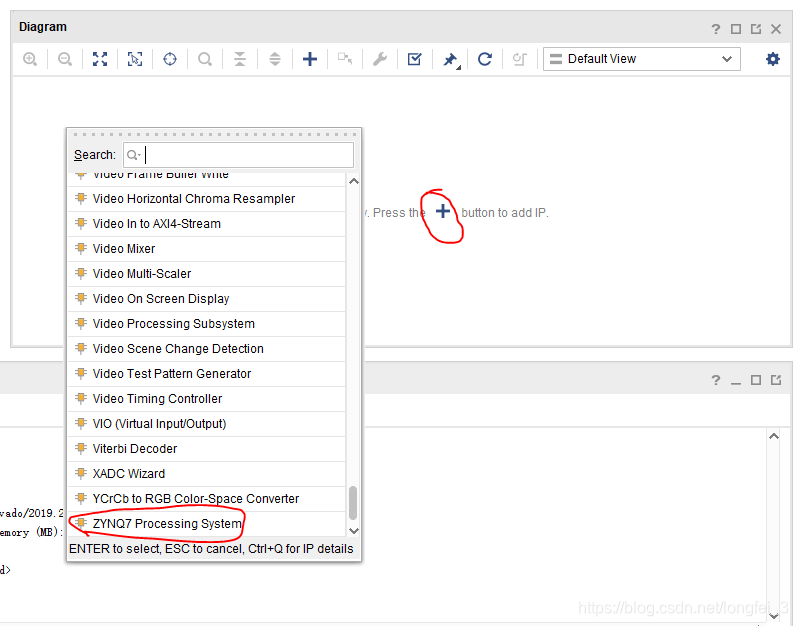

添加 Block Design

添加Arm核

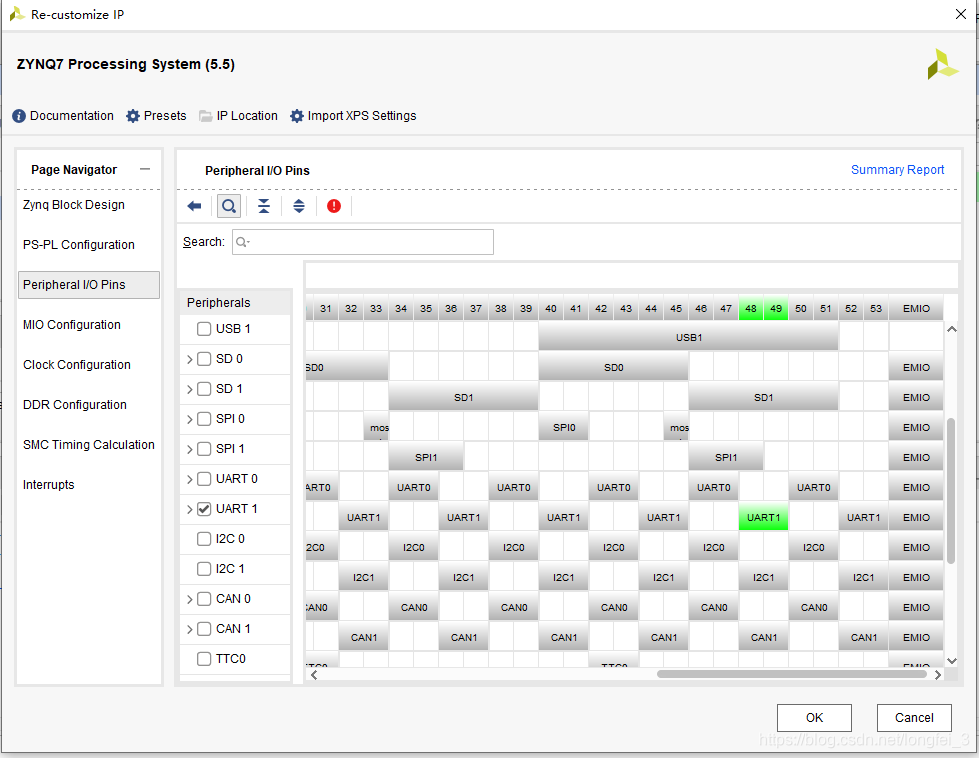

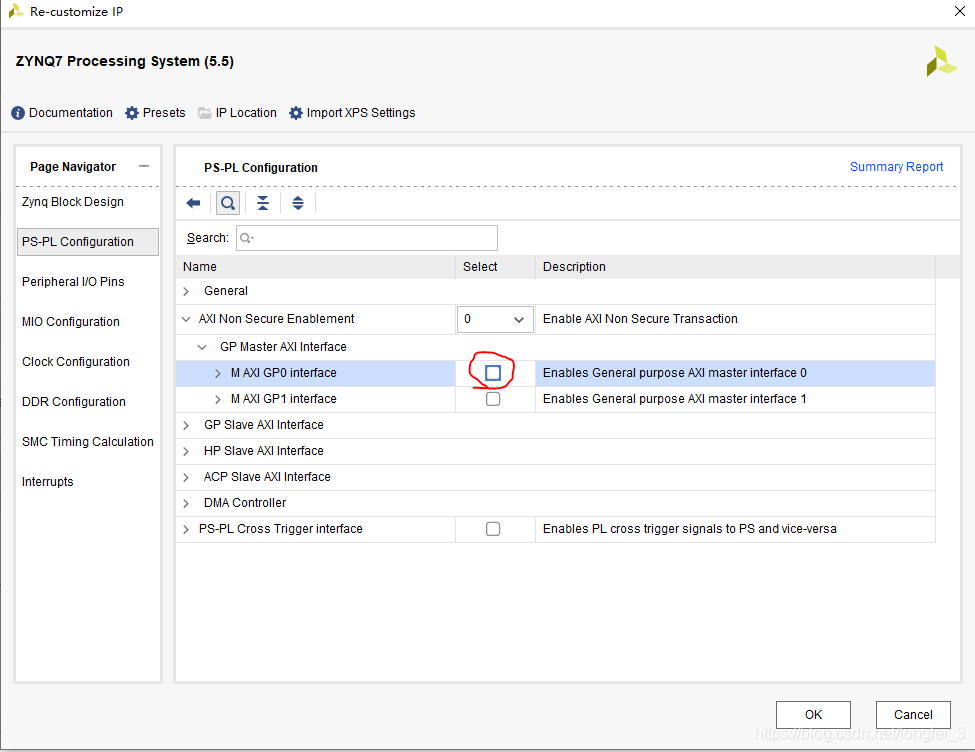

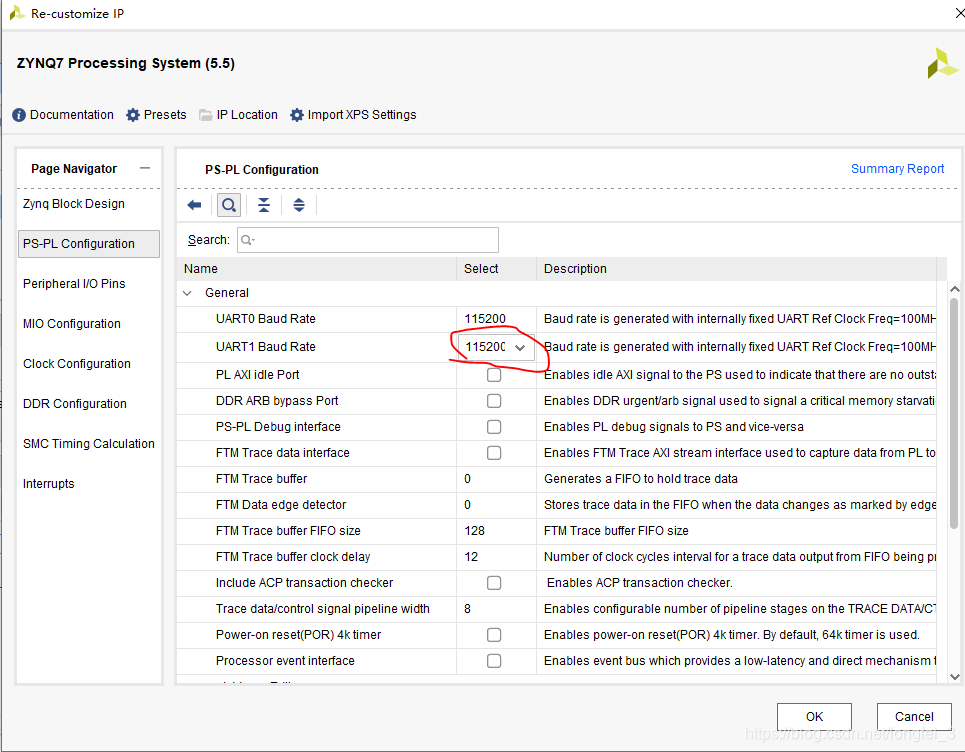

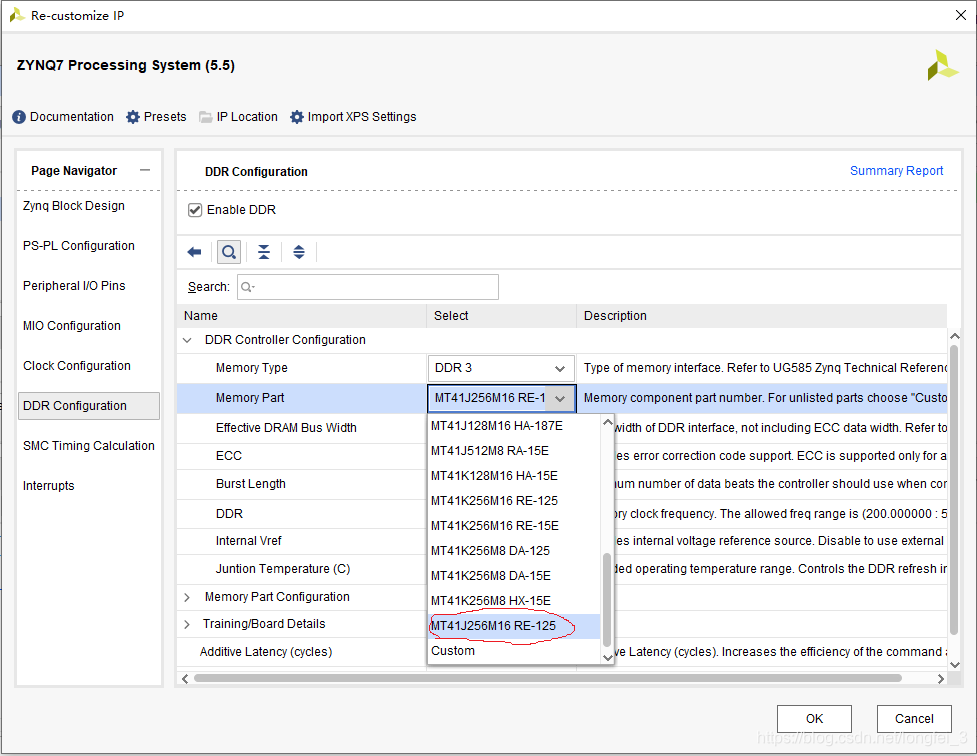

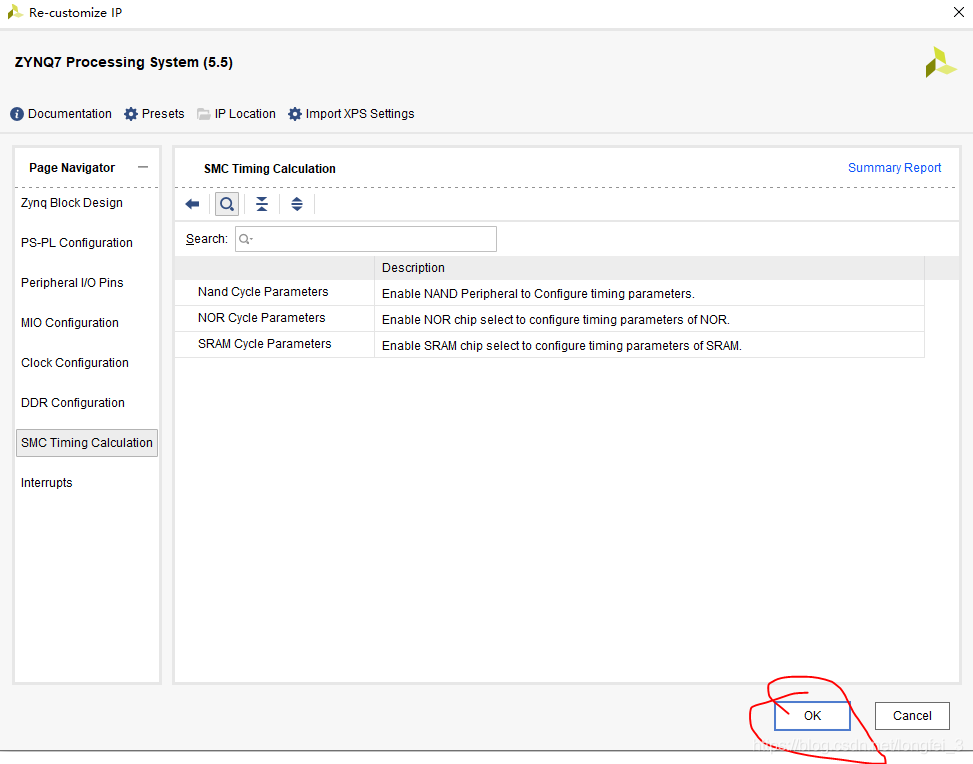

双击ARM核设置一下,这里设置跟板子一致UART1,波特率选择115200,没有用到PL,AXI也没使用。

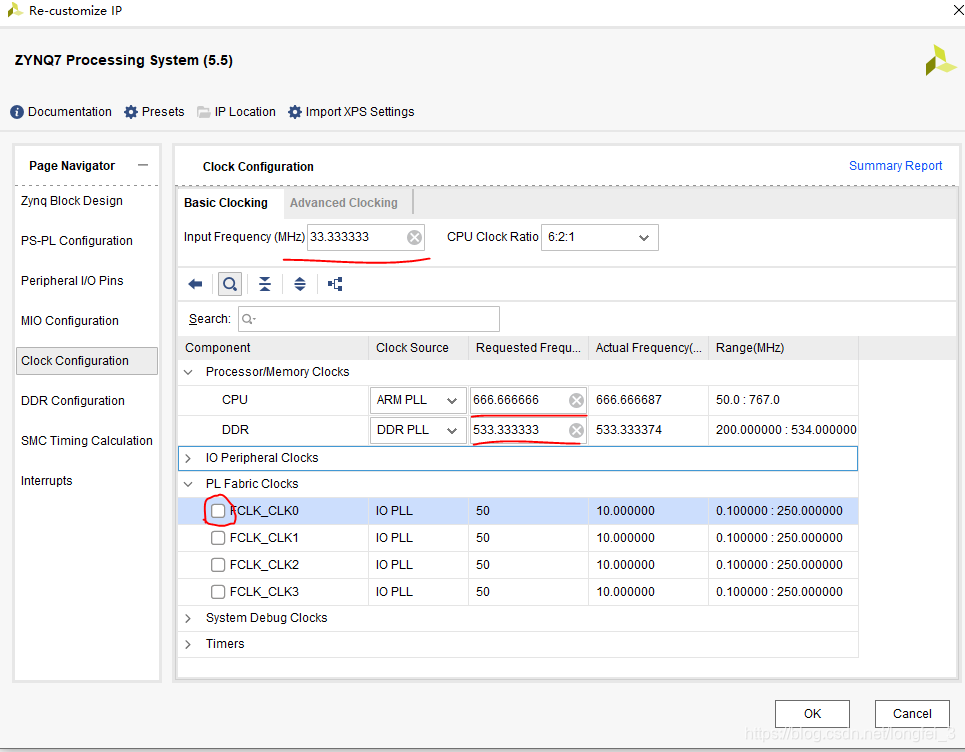

时钟默认即可,黑金的7020最高可以跑到767Mhz。

设置完成。

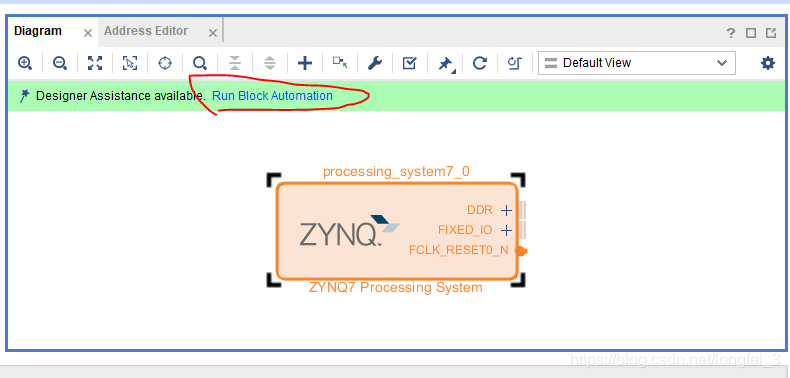

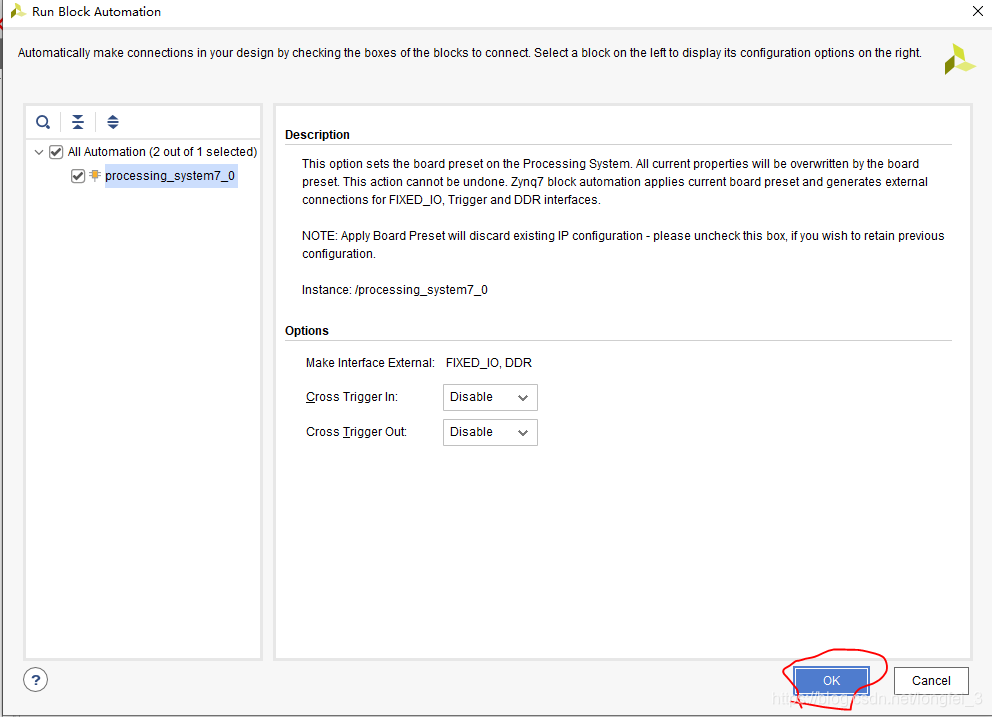

自动连一下

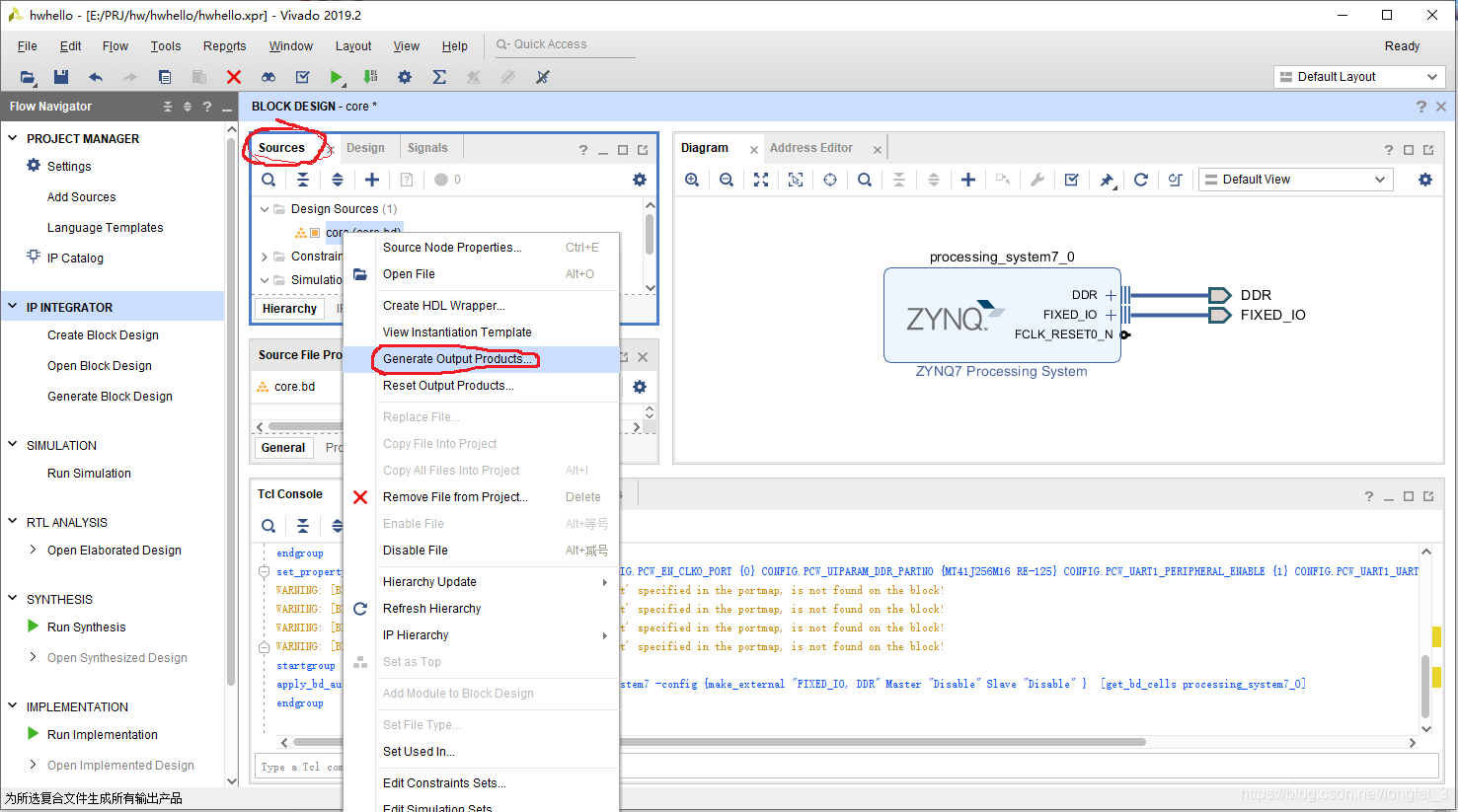

好了,生成文件

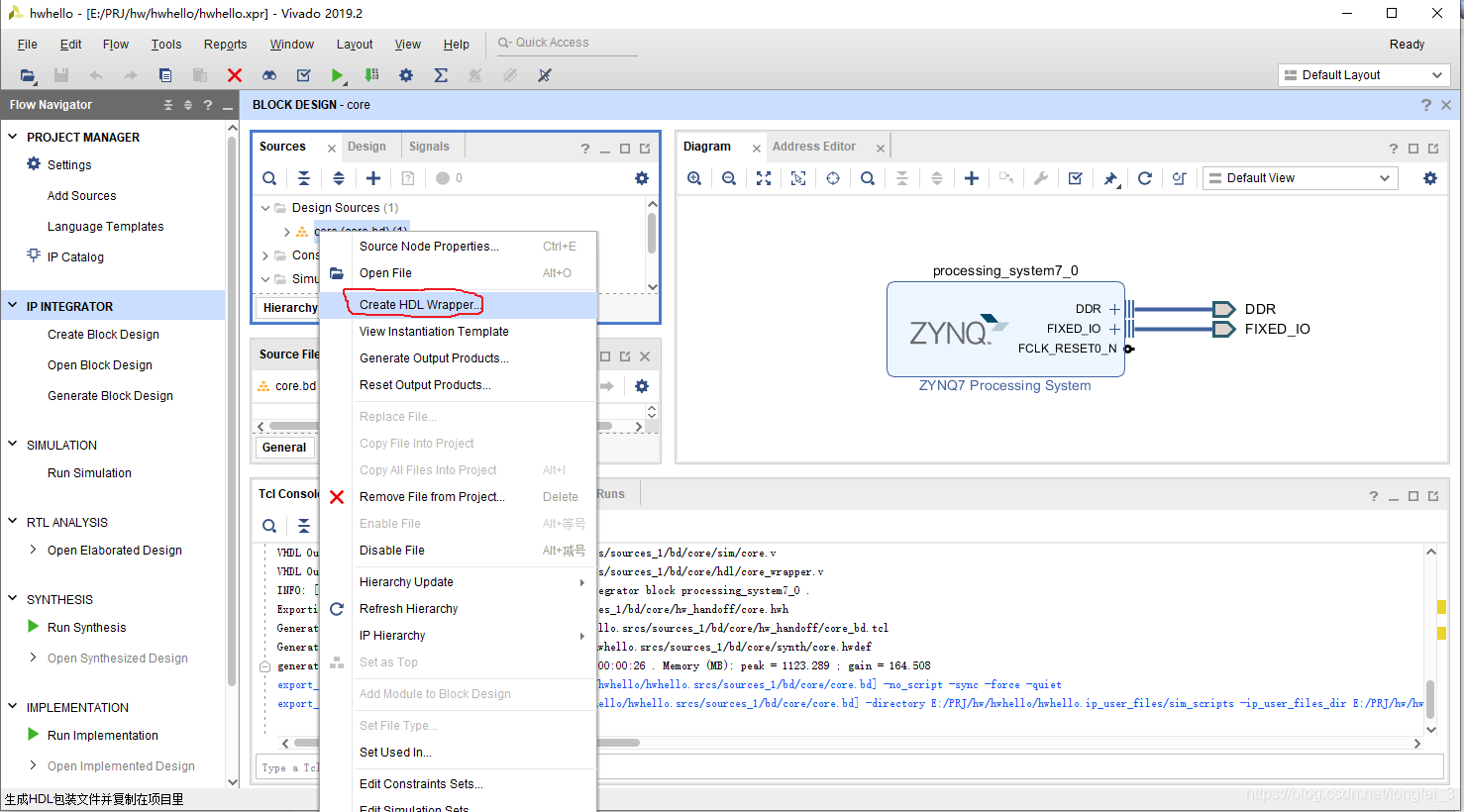

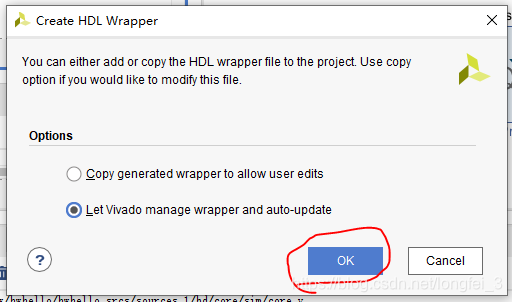

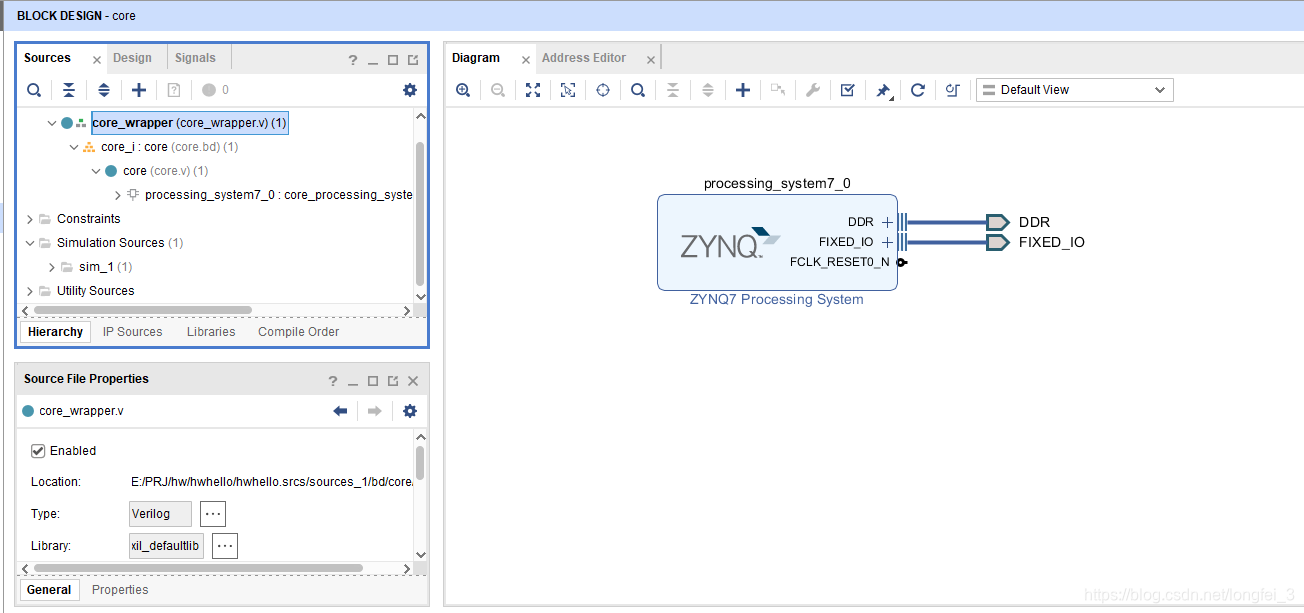

生成顶层文件

硬件部分完成了。

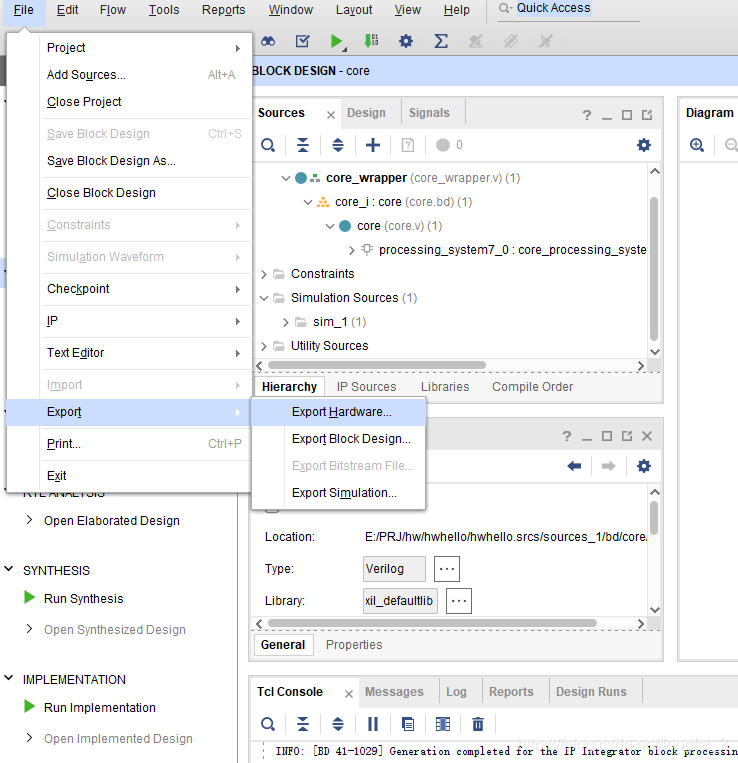

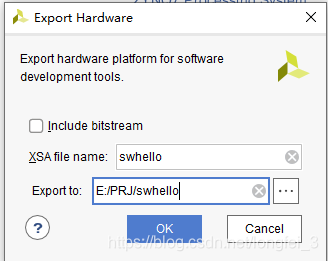

导出设计到软件,没有用到PL,所以不用综合生成bit文件了,这里直接导出

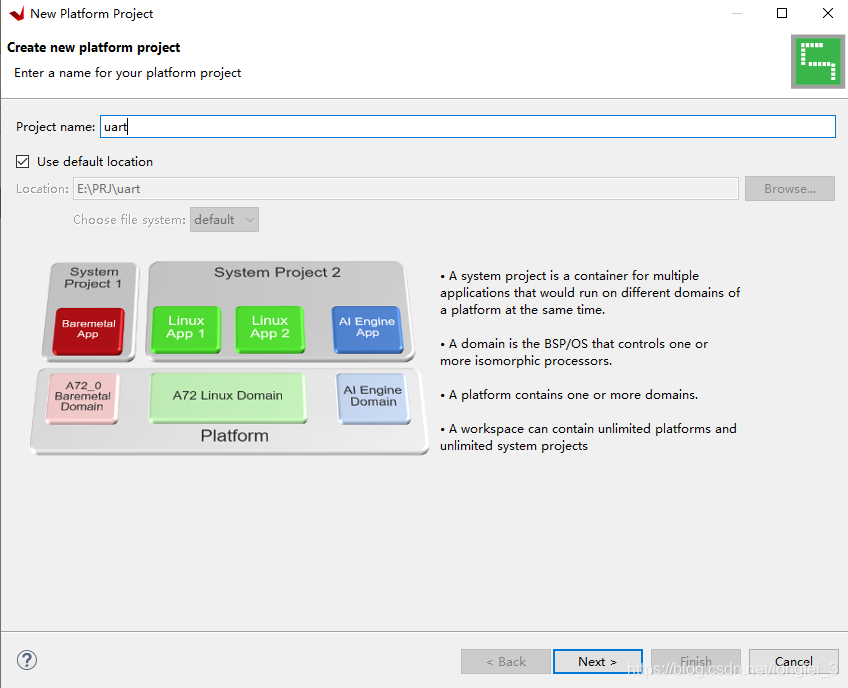

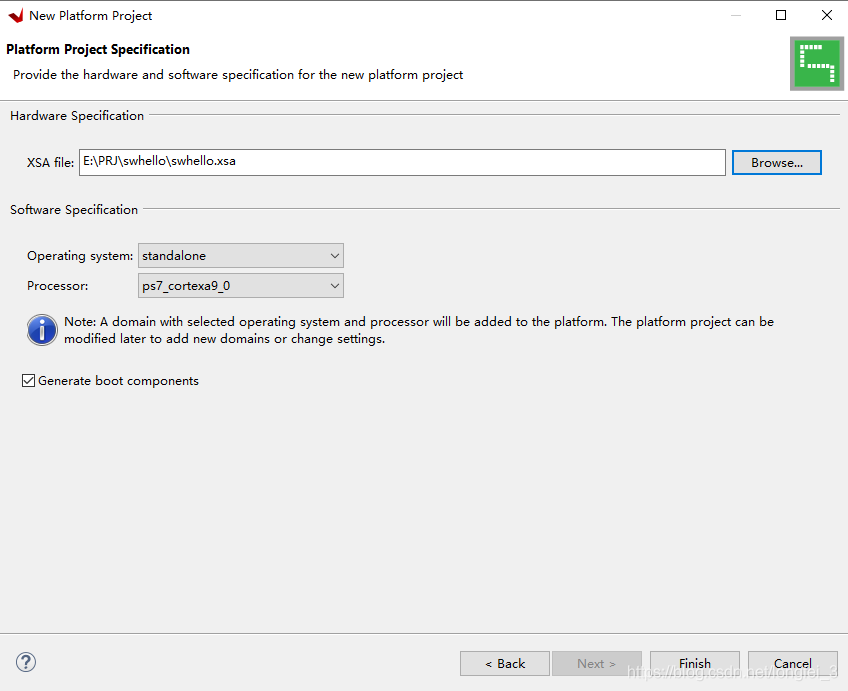

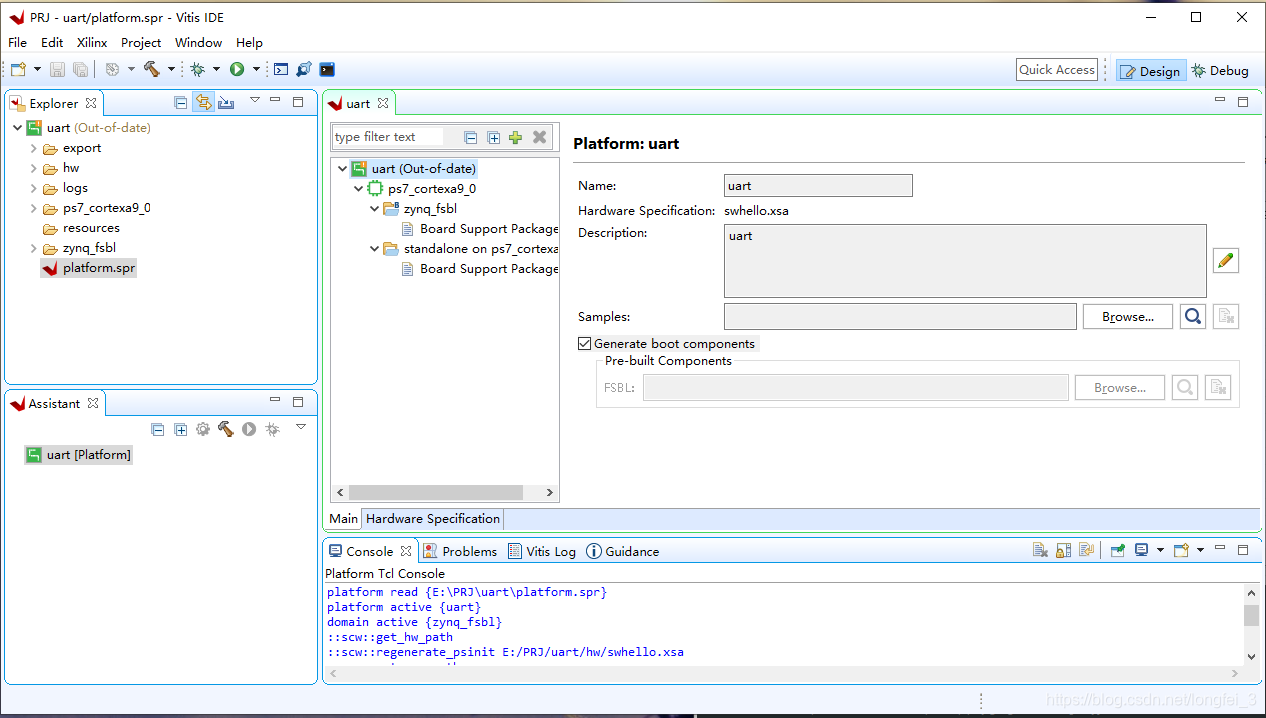

导出完成,这里开始软件操作,先创建一个 platform project导入刚才的设计

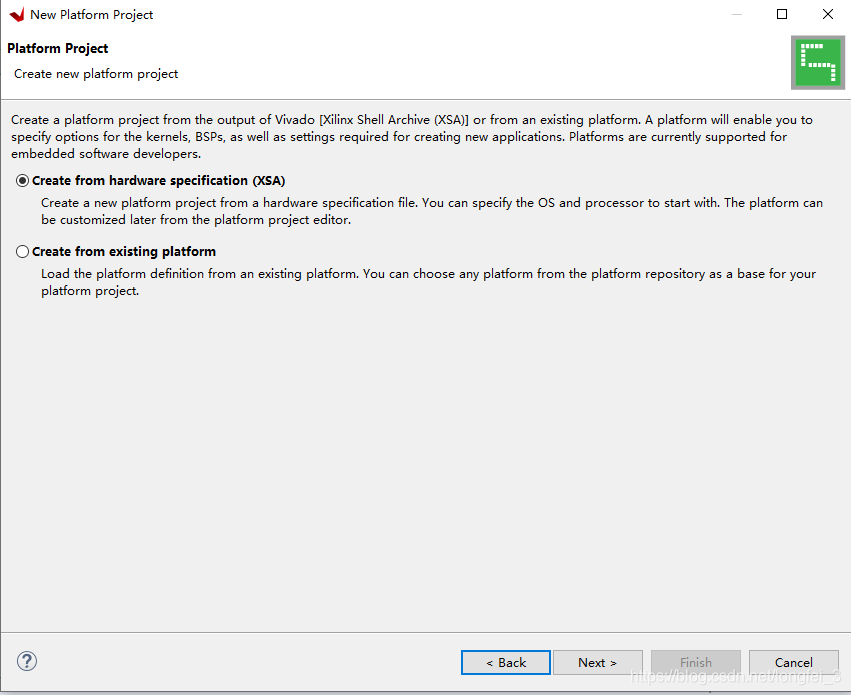

选择Vivado导出的设计,点击 finish完成

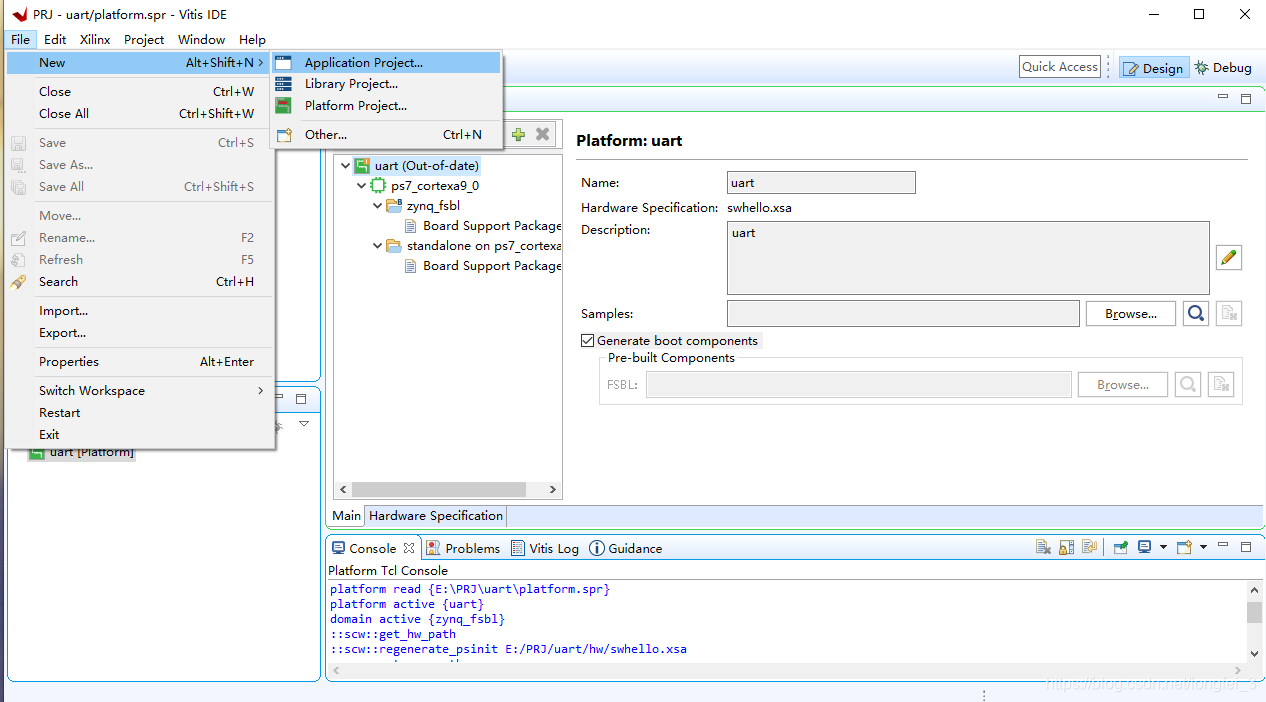

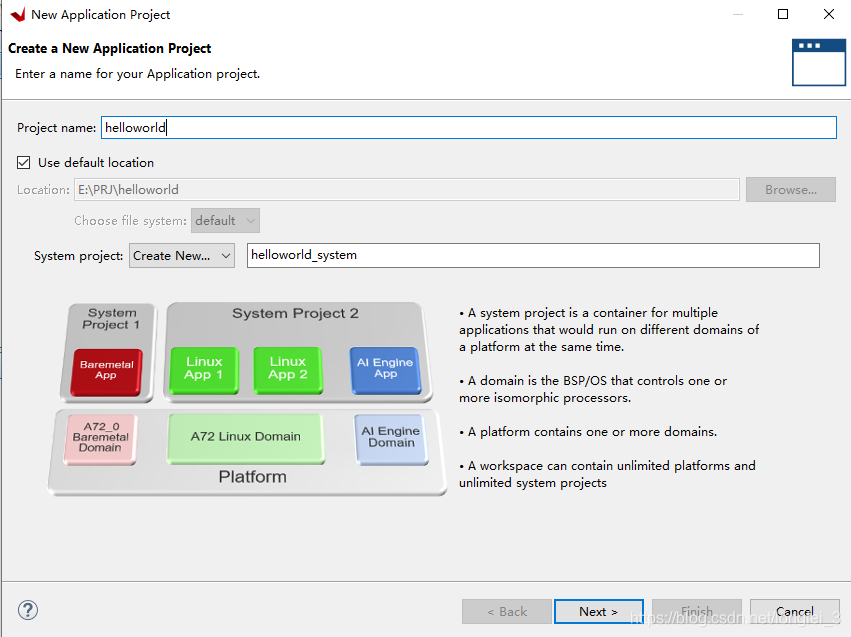

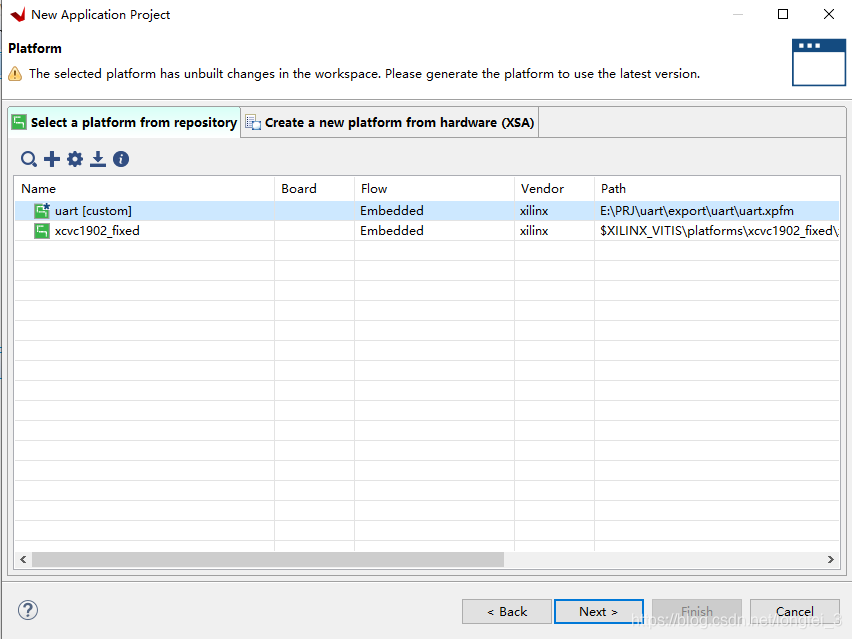

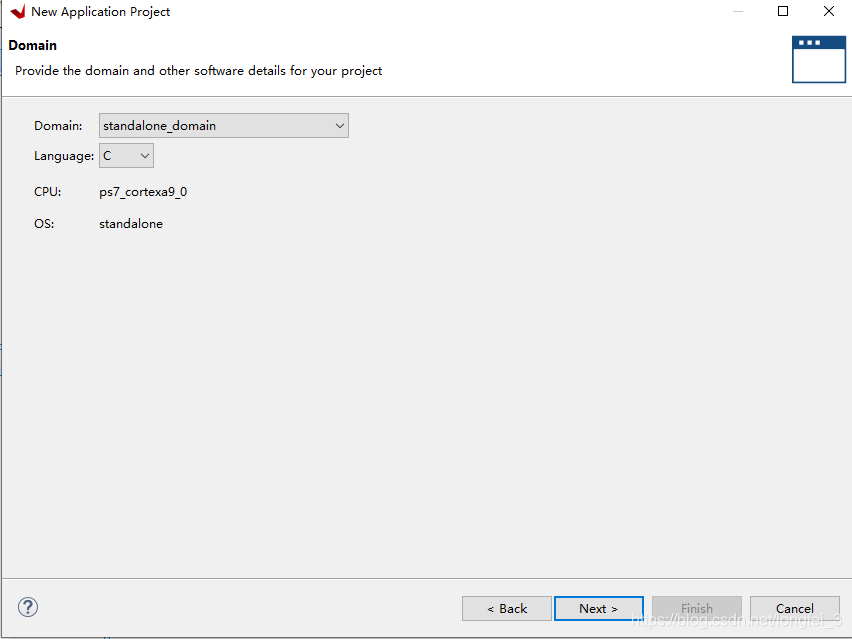

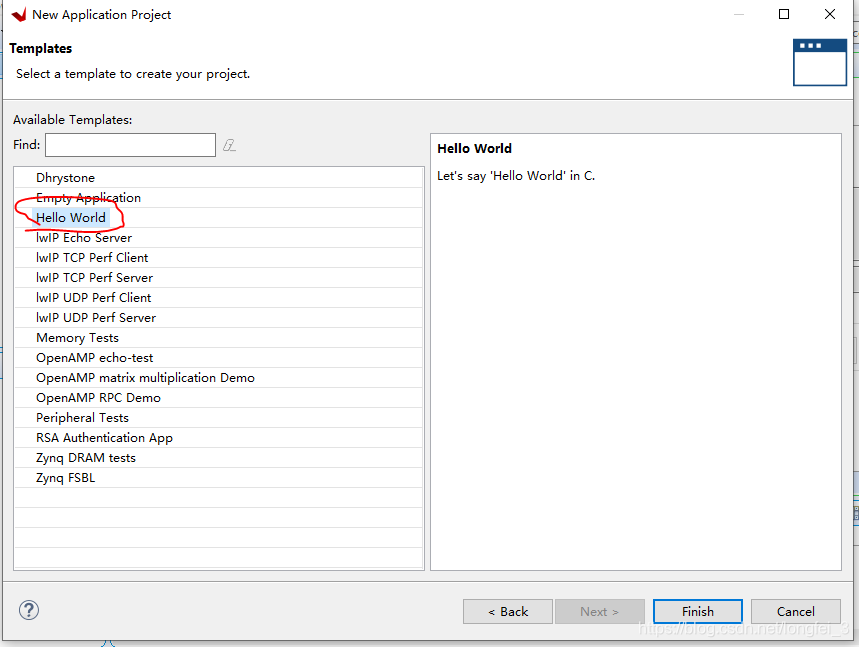

创建一个Application project

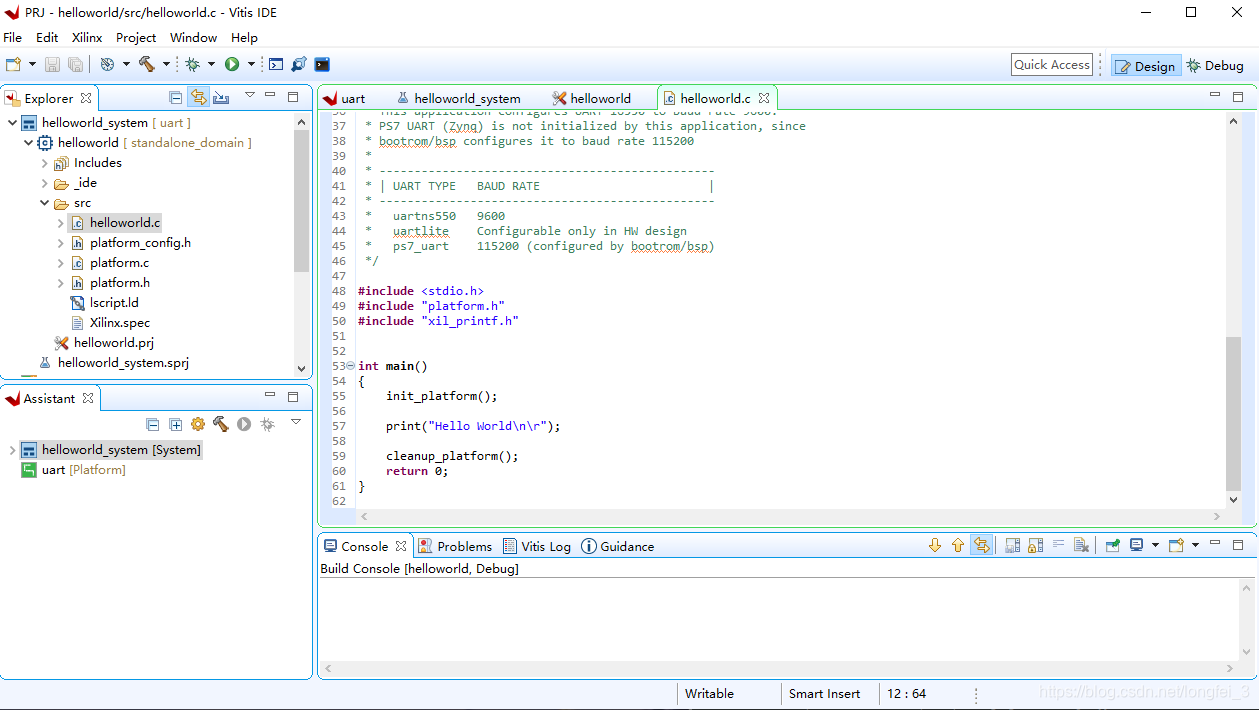

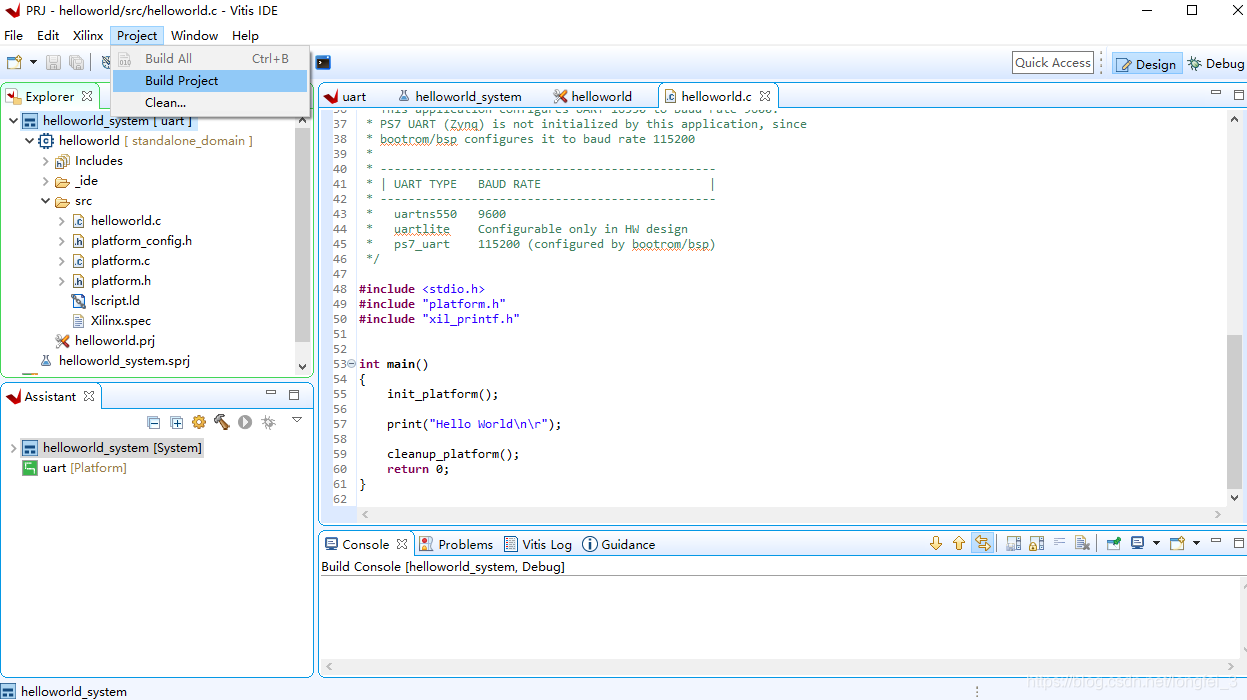

编译helloworld工程

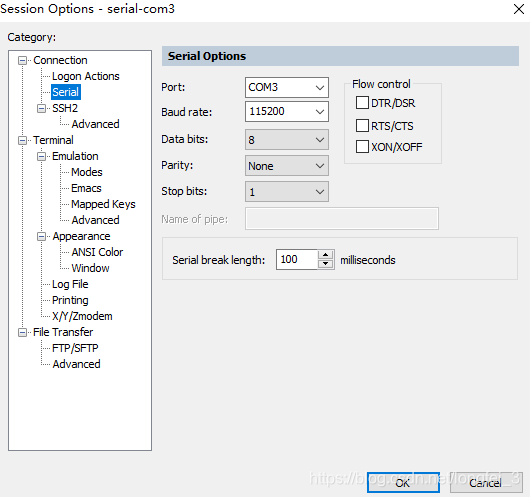

给板子接好,上电,连接串口软件,我的串口是com3设置如下

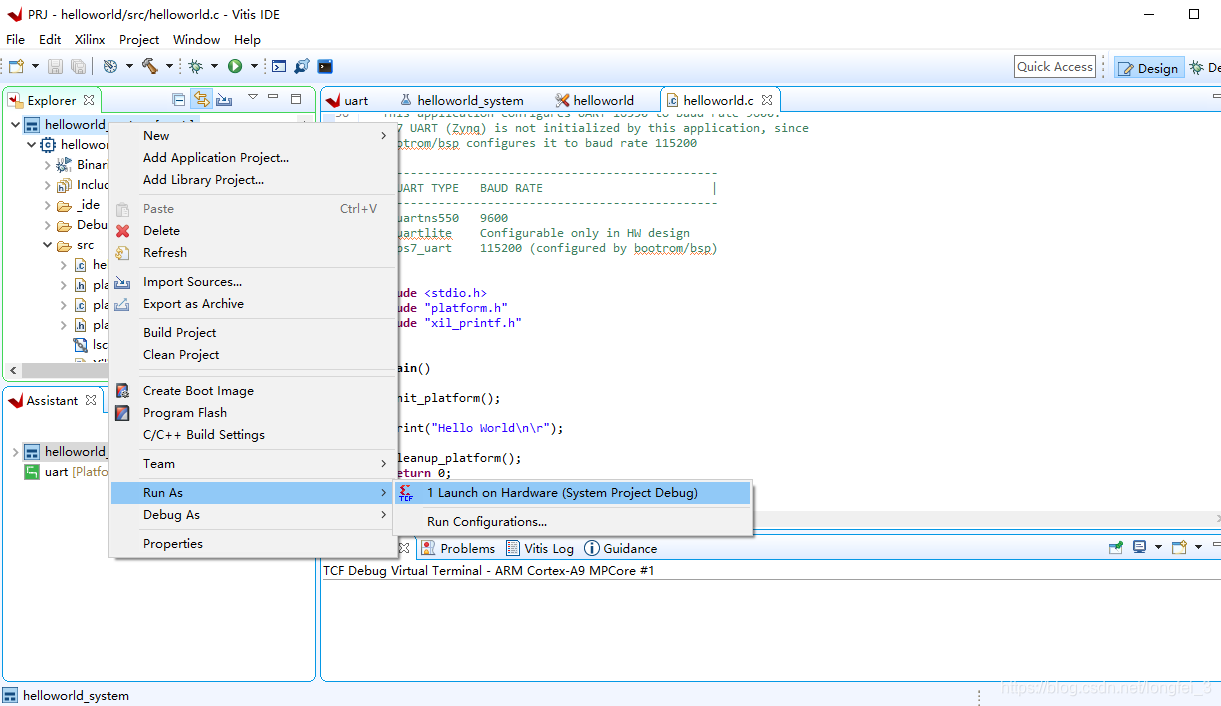

下载运行

已经输出了“hello world”

结束

整体来说跟之前没有区别,至于官方宣传Vitis的AI还没研究过,感觉这个平台编译似乎有点慢,也许是塞了很多用不到的功能,用起来要麻烦一点,还要自己导入。

1876

1876

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?