一、实验原理

二、代码设计

`timescale 1ns / 1ps

module state_debounce(

input sys_clk ,

input rst_n ,

input key ,

output reg flag

);

localparam IDLE = 2'b00 ;

localparam count_state= 2'b01 ;

localparam flag_come = 2'b10 ;

localparam keep = 2'b11 ;

reg [1:0] cur_state ;

reg [1:0] next_state ;

reg [20:0] cnt ;

parameter TIME_20ms = 20'd50_000_0 ;

always@(posedge sys_clk)

if(!rst_n)

cur_state <= IDLE ;

else

cur_state <= next_state ;

always@(*)

case(cur_state)

IDLE :begin

if( key == 0 )

next_state = count_state ;

else

next_state = cur_state ;

end

count_state:begin

if( key == 0 && cnt == TIME_20ms -1)

next_state = flag_come ;

else if( key == 1 )

next_state = IDLE ;

else

next_state = cur_state ; //没有自加到TIME_20ms -1

end

flag_come :begin

if( key == 0 )

next_state = keep ;

else

next_state = IDLE ;

end

keep :begin

if(key == 1)

next_state = IDLE ;

else

next_state = cur_state ;

end

default: ;

endcase

always@(posedge sys_clk)

if(!rst_n) begin

cnt <= 0 ;

flag <= 0 ;

end

else

case(cur_state)

IDLE :begin

cnt <= 0 ;

flag <= 0 ;

end

count_state:begin

cnt <= cnt + 1 ;

flag <= 0 ;

end

flag_come :begin

flag <= 1 ;

cnt <= 0 ;

end

keep :begin

cnt <= 0 ;

flag <= 0 ;

end

default:;

endcase

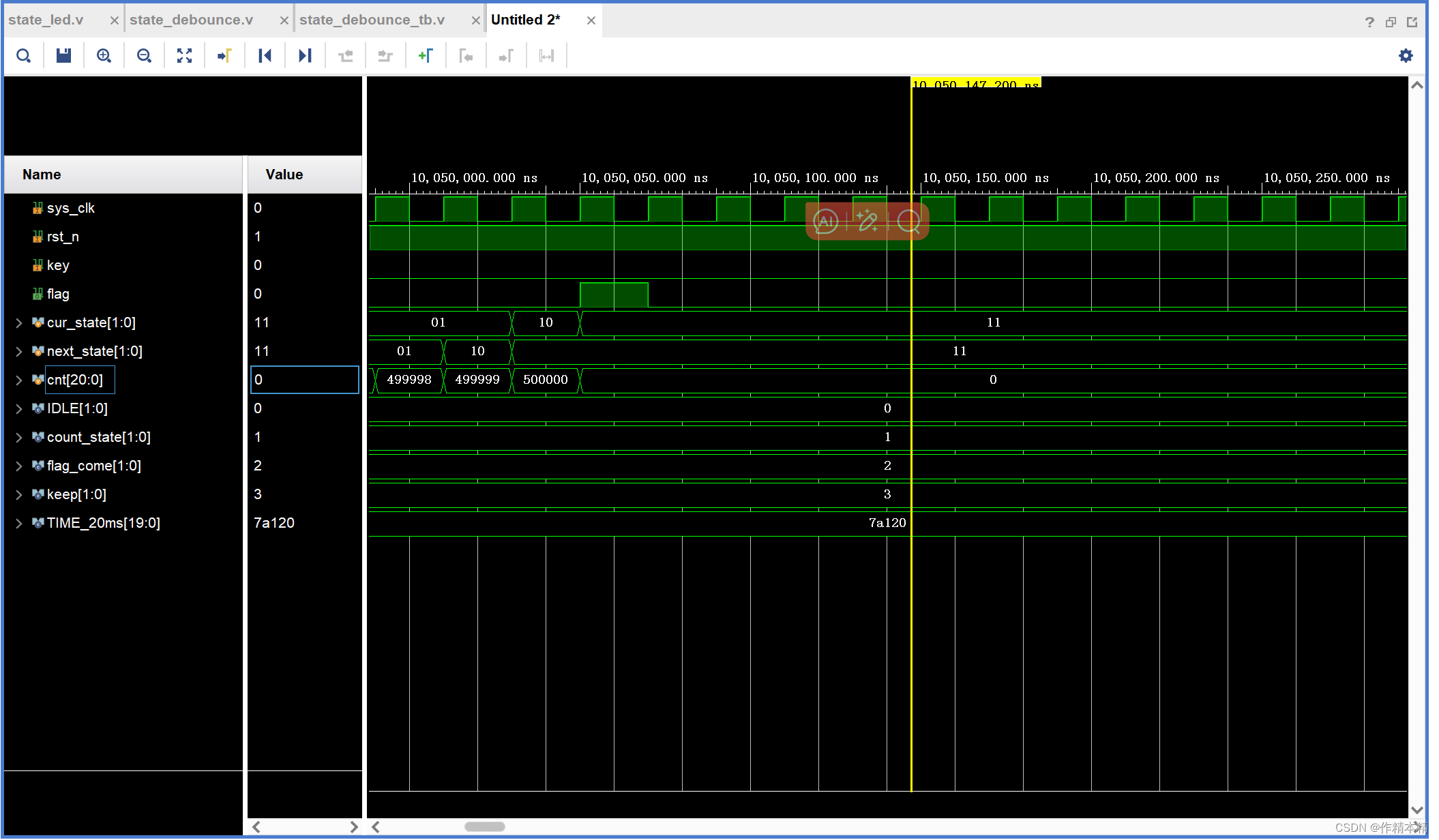

endmodule三、仿真结果

`timescale 1ns / 1ps

module state_debounce_tb( );

reg sys_clk ;

reg rst_n ;

reg key ;

wire flag ;

initial begin

sys_clk = 0 ;

rst_n = 0 ;

key = 1 ;

#20

rst_n = 1;

#50000

key=0 ;

#50000000

key=1 ;

end

always #10 sys_clk=~sys_clk;

state_debounce u1(

. sys_clk (sys_clk) ,

. rst_n (rst_n ) ,

. key (key ) ,

. flag (flag )

);

endmodule

550

550

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?