出于学习目的,将AD9164英文数据手册翻译为中文数据手册,分享给需要的小伙伴。

水平有限,烦请谅解。如翻译有误,请留言,笔者将尽快更正,谢谢~

AD9164中文数据手册 16bit 12GSPS RF DAC and DDS

特征

- DAC更新速率高达12 GSPS(最低)

- 6 GSPS的直接射频合成(最低)

- 基带模式下,DC-2.5 GHz

- 2×不归零(NRZ)模式下,DC-6 GHz

- 混合模式下,1.5 GHz至7.5 GHz

- 旁路插值:2×、3×、4×、6×、8×、12×、16×、24×

- 出色的动态性能

- 快速跳频

应用场景

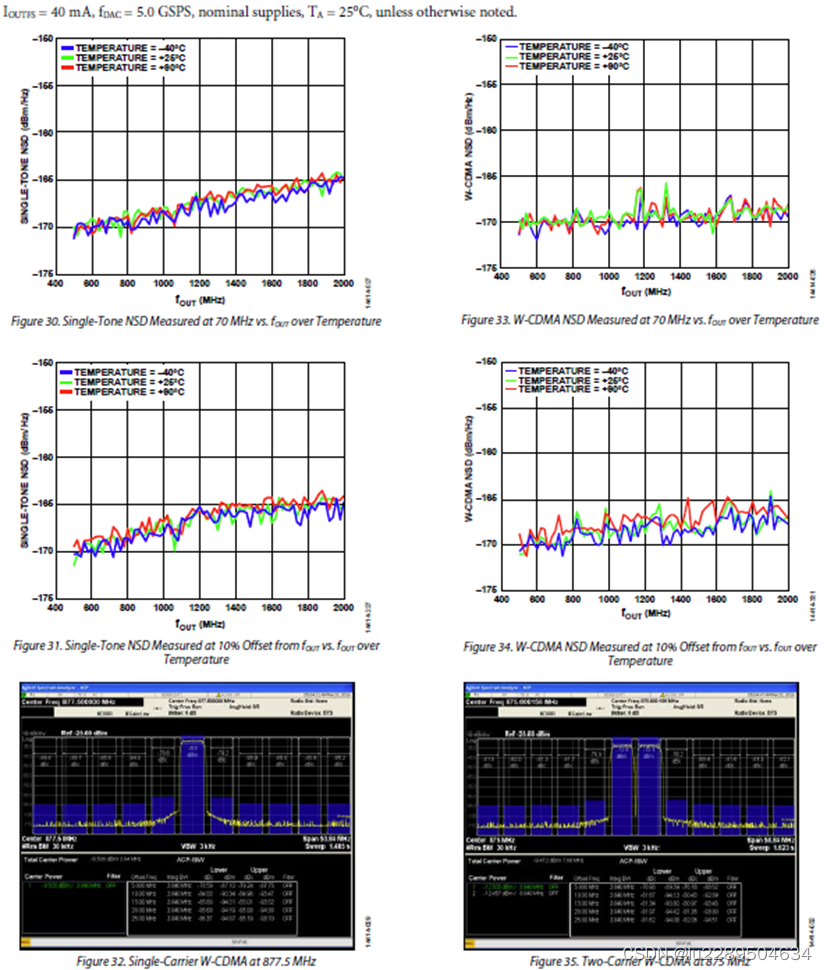

宽带通信系统、DOCSIS 3.1 CMTS/视频点播(VOD)/边缘正交调幅(EQAM)、无线通信基础设施、W-CDMA、LTE、LTE-A、点对点

概述

AD9164是一款高性能的16位数模转换器(DAC)和支持6 GSPS更新速率的直接数字合成器(DDS)。DAC内核基于与2×插值滤波器耦合的四开关架构,在某些模式下可实现高达12 GSPS的有效DAC更新速率。高动态范围和带宽使这些DAC非常适合最苛刻的高速射频(RF)DAC应用。DDS由一组32个,32位数字控制振荡器(NCO)组成,每个振荡器都有自己的相位累加器。

当与100MHz串行外设接口(SPI)和快速跳频模式相结合时,可以启用相位相干快速跳频(FFH),并提供多种模式以支持多种应用。在基带模式下,宽模拟带宽能力与高动态范围相结合,支持符合DOCSIS 3.1 电缆基础设施标准的最低一个载波至最大 1.791 GHz 的全频谱信号带宽。通过 2x插值滤波器 (FIR85),AD9164 可配置为较低的数据速率和转换器时钟,以降低整个系统的功耗并简化滤波要求。在混合模式下,AD9164 可在第二和第三奈奎斯特区重建高达7.5 GHz的射频载波,同时仍能保持出色的动态范围。输出电流的编程范围为 8 mA 至 38.76 mA。AD9164数据接口由多达8个JESD204B串行器/解串器(SERDES)通道组成,这些通道在通道速度和通道数量方面是可编程的,以实现应用灵活性。

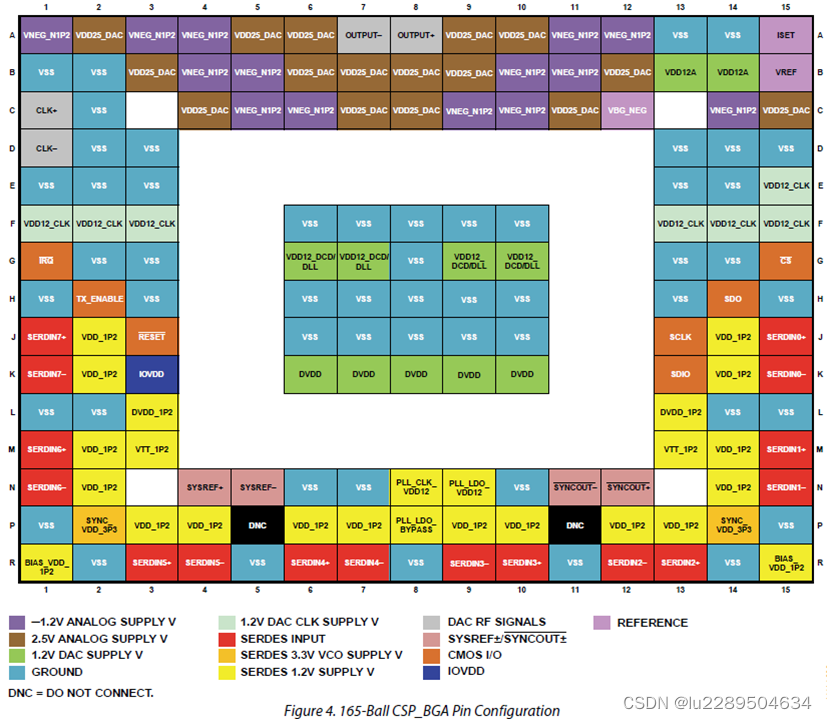

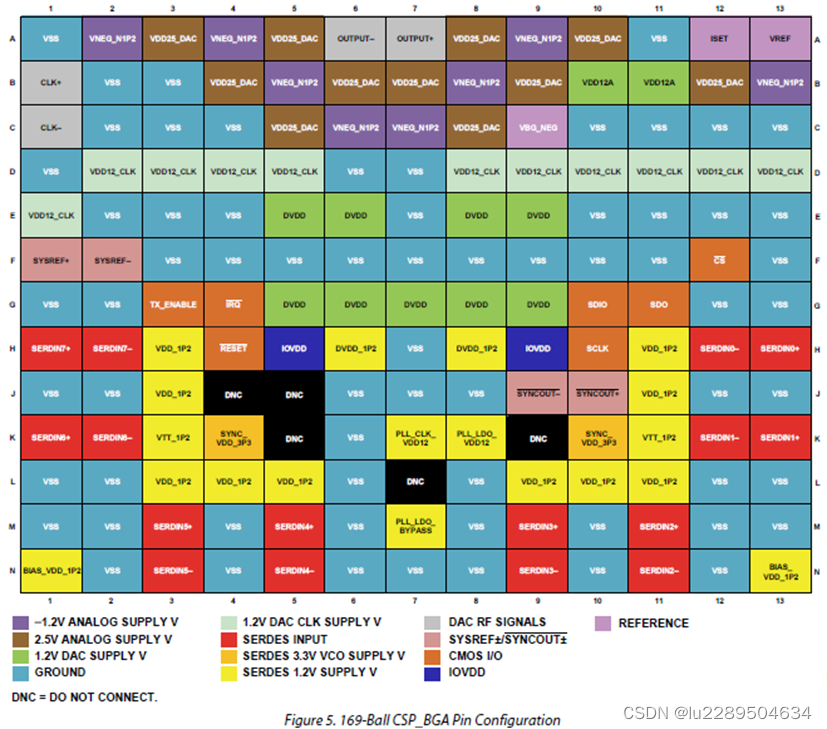

SPI接口配置AD9164并监控所有寄存器的状态。AD9164提供165球、8毫米×8毫米、0.5毫米间距的CSP_BGA封装和169球、11毫米×11毫米、0.8毫米间距的CSP _BGA封装,包括含铅选项。

产品亮点

1. 高动态范围和信号重建带宽支持高达7.5GHz的RF信号合成。

2.多达8条通道JESD204B SERDES接口,在通道数量和通道速度灵活。

3. 带宽和动态范围符合DOCSIS 3.1标准和多频带无线通信标准,并留有余量。

规格

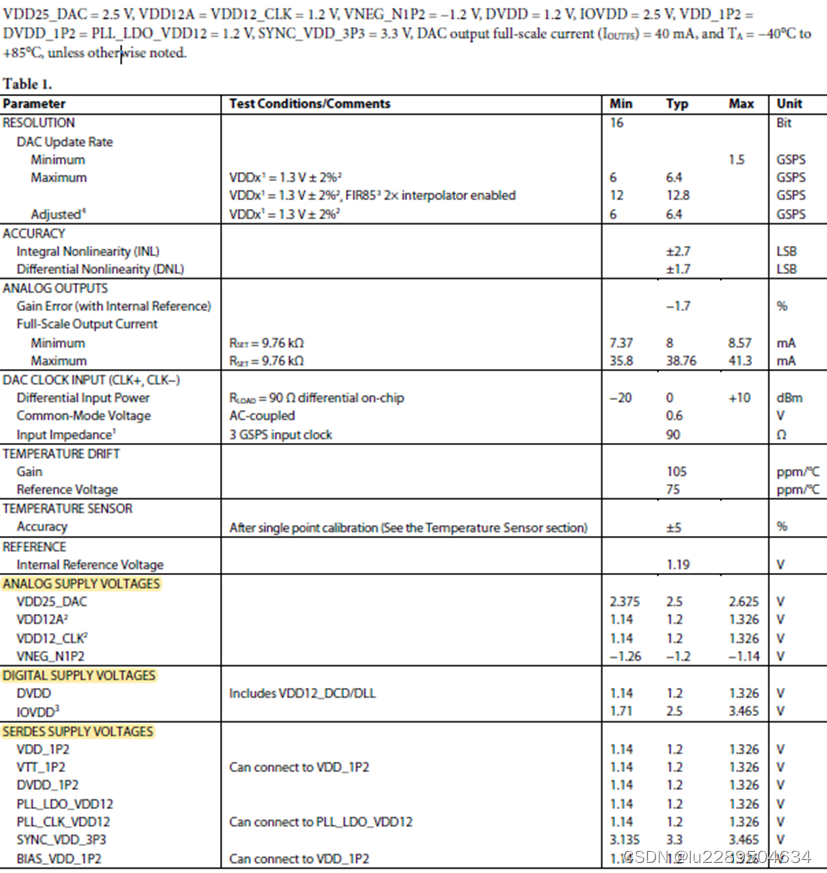

直流规格

1有关更多详细信息,请参阅时钟输入部分。

2为了获得最低的噪声性能,请为VDD12_CLK和VDD12A引脚使用单独的电源滤波器网络。

3 IOVDD的范围为1.8V至3.3V,公差为±5%。

4调整后的DAC更新率计算为fDAC除以所需的最小插值因子。对于AD9164,最小插值因子为1。因此,在fDAC=6 GSPS的情况下,调整后的fDAC=6GSPS。当启用FIR85时,使设备进入2×NRZ模式,fDAC=2×(DAC时钟输入频率),最小插值增加到2×(插值值)。因此,对于AD9164,启用FIR85,DAC时钟=6 GSPS,fDAC=12 GSPS,最小插值=2×,调整后的DAC更新率=6 GSPS。

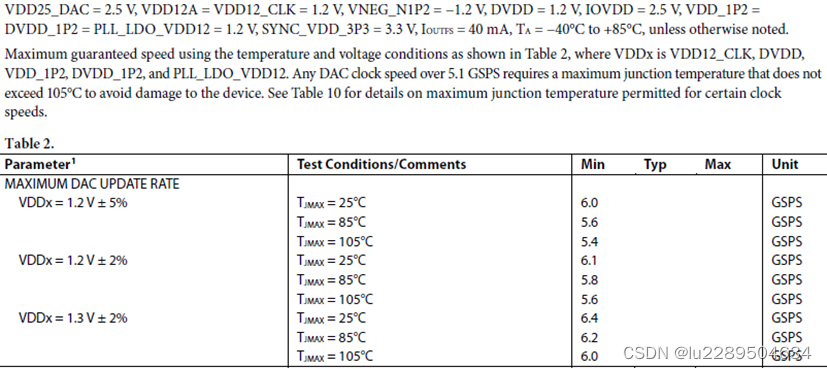

DAC输入时钟超频规范

1 TJMAX是最高结温。

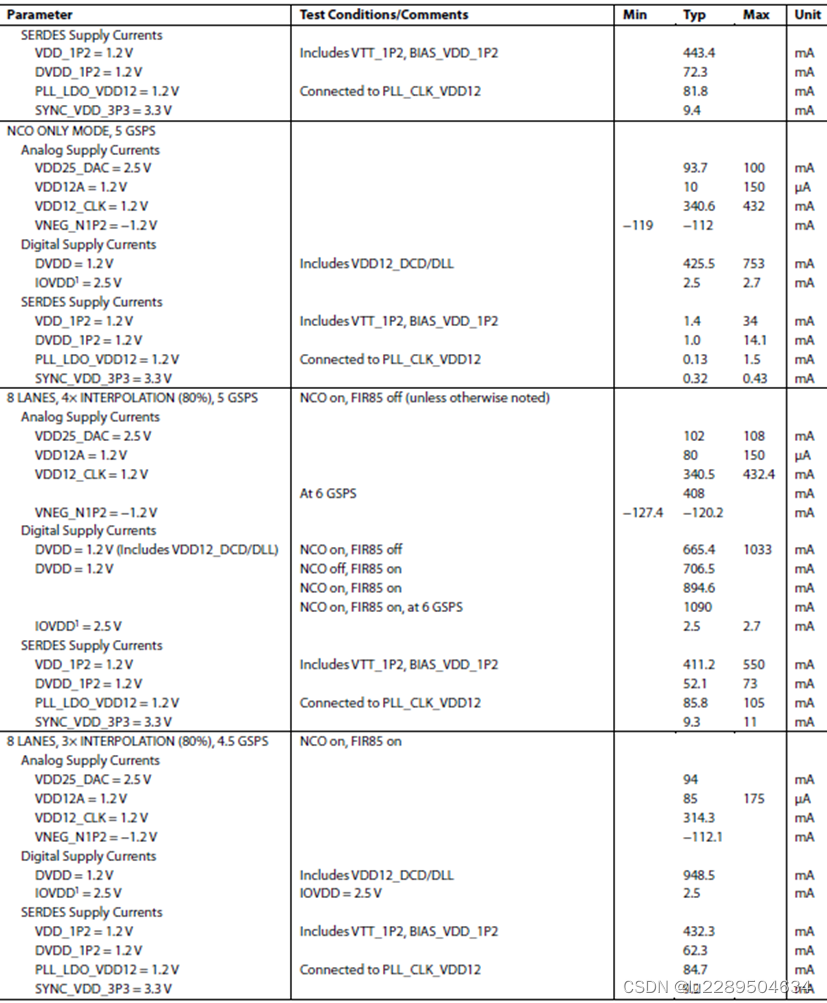

直流供电规范

1 IOVDD的范围为1.8V至3.3V,公差为±5%。

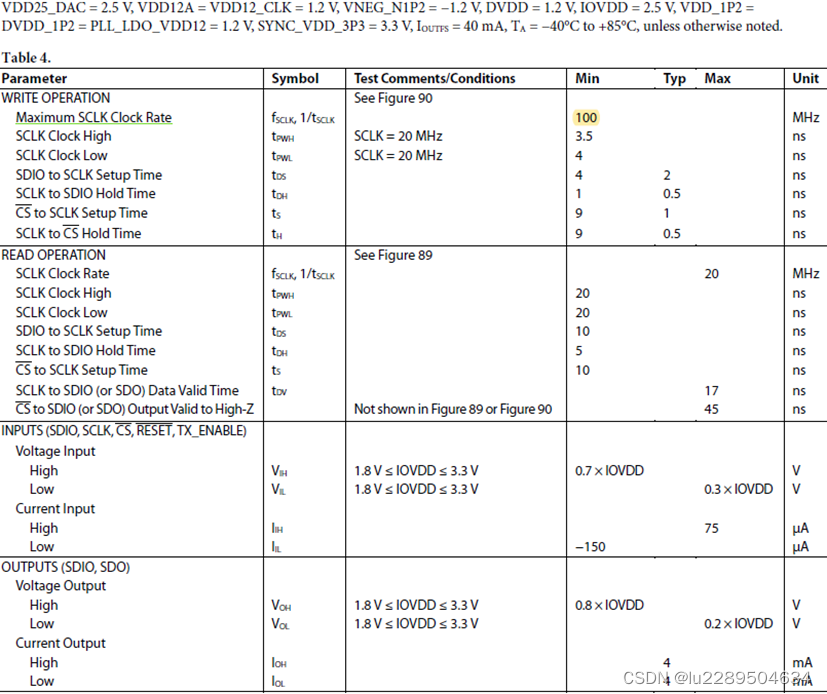

串行端口和CMOS引脚规格

JESD204B串行接口速度规范

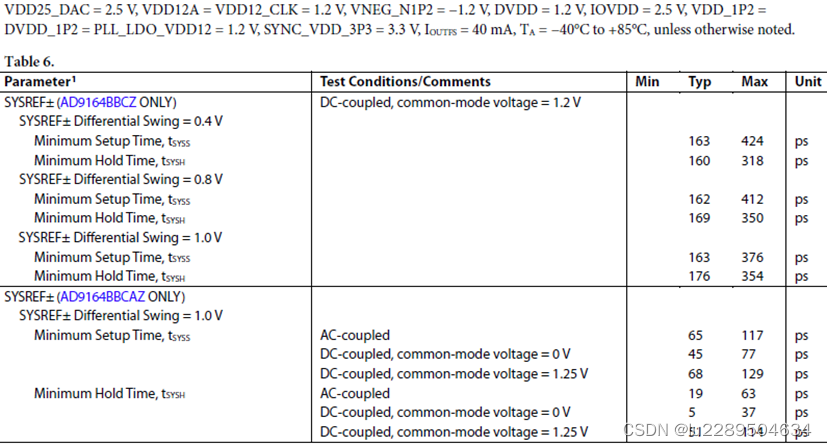

SYSREF±至DAC时钟定时规范

1 SYSREF±脉冲必须至少有四个DAC时钟边沿宽度加上表6中的设置和保持时间。有关更多信息,请参阅同步处理模式概述部分。

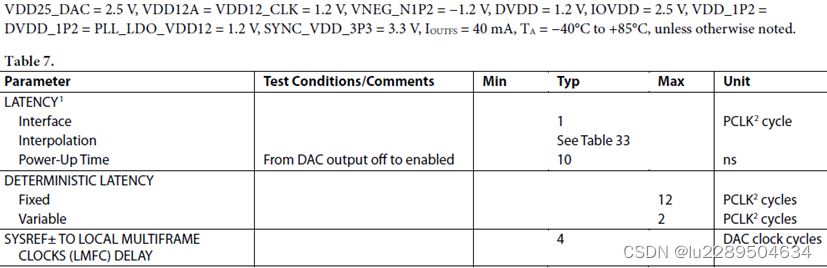

数字输入数据定时规范

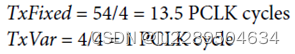

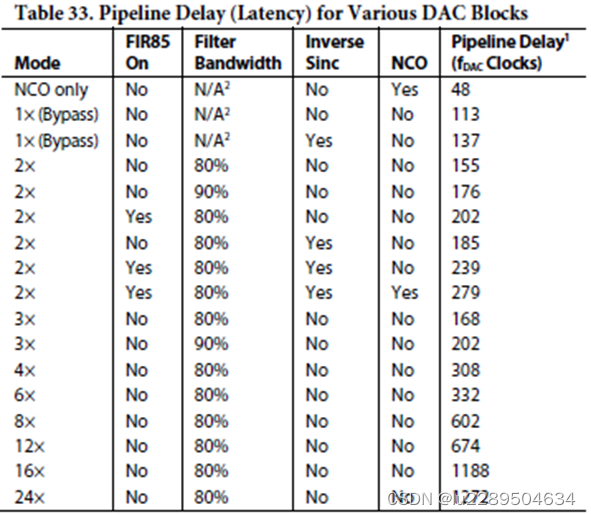

1通过设备的总延迟(或管道延迟)计算如下:

总延迟=接口延迟+固定延迟+可变延迟+管道延迟

每个块的管道延迟示例见表33。

2 PCLK是AD9164的内部处理时钟,等于通道速率÷40。

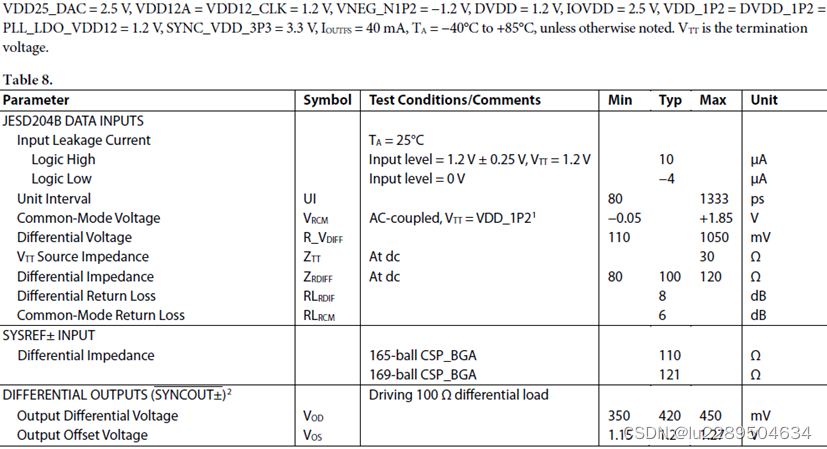

JESD204B接口电气规范

1在交流耦合电容器的输入侧测量。

2 IEEE标准1596.3 LVDS兼容。

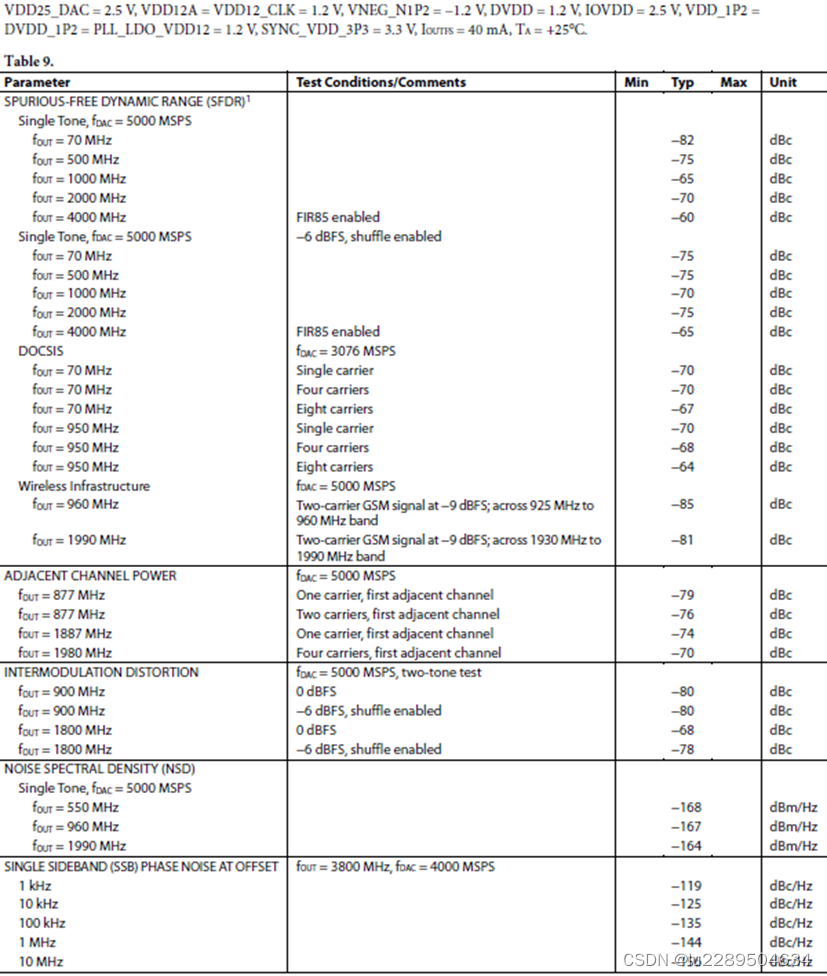

交流规格

1 有关通过调整时钟输入优化 SFDR 和减少基波镜像的更多详情,请参阅 "时钟输入 "部分。

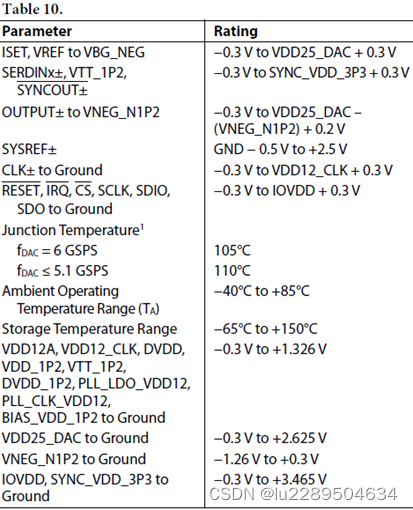

最大额定值

1 在支持的环境温度下运行时,设备的某些运行模式可能会导致设备接近或超过最高结温。器件的散热可能需要采取额外措施,如主动气流、散热器或其他措施。

达到或超过绝对最大额定值下所列的应力可能会对产品造成永久性损坏。这仅仅是应力额定值;并不意味着在这些条件下或任何其他超过了本规范操作部分所标明的条件,芯片能够正常运行。长时间超出最大工作条件运行可能会影响产品的可靠性。

回流焊曲线

AD9164 回流曲线符合 JEDEC JESD204B 无铅器件标准。最高回流焊温度为 260°C。

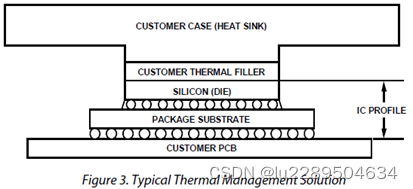

热管理

AD9164 是一款高功率器件,耗散功率接近 3 W,具体取决于用户应用和配置。由于功率耗散,AD9164 采用裸露芯片封装,为客户提供最有效的芯片温度控制方法。裸露芯片可直接冷却芯片。

图 3 显示了安装在用户印刷电路板 (PCB) 和散热器(通常是铝外壳)上的器件剖面图,以保持结点(裸露裸片)低于表 10 中的最大结点温度。

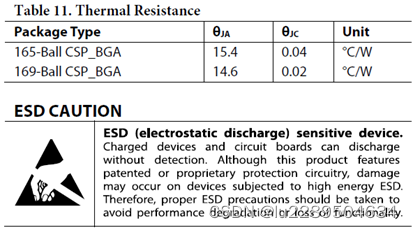

热阻

典型的 θJA 和 θJC 值是针对球形表面贴装封装的4层 JEDEC 2S2P高有效导热率测试板而规定的。气流可增加散热,有效降低 θJA。θJC是在封装底部监测温度时获得的。

其中

θJA是在一立方英尺密封外壳中测量的自然对流结至环境空气热阻。

TJ是芯片结温。

TA是静止空气环境中的环境温度。

P是芯片耗散的总功率(热量)。(在 AD9164 的情况下,这是在裸芯片的封装顶部测量的)。

TC是封装外壳温度。(对于 AD9164,温度是在裸芯片上测量的)。

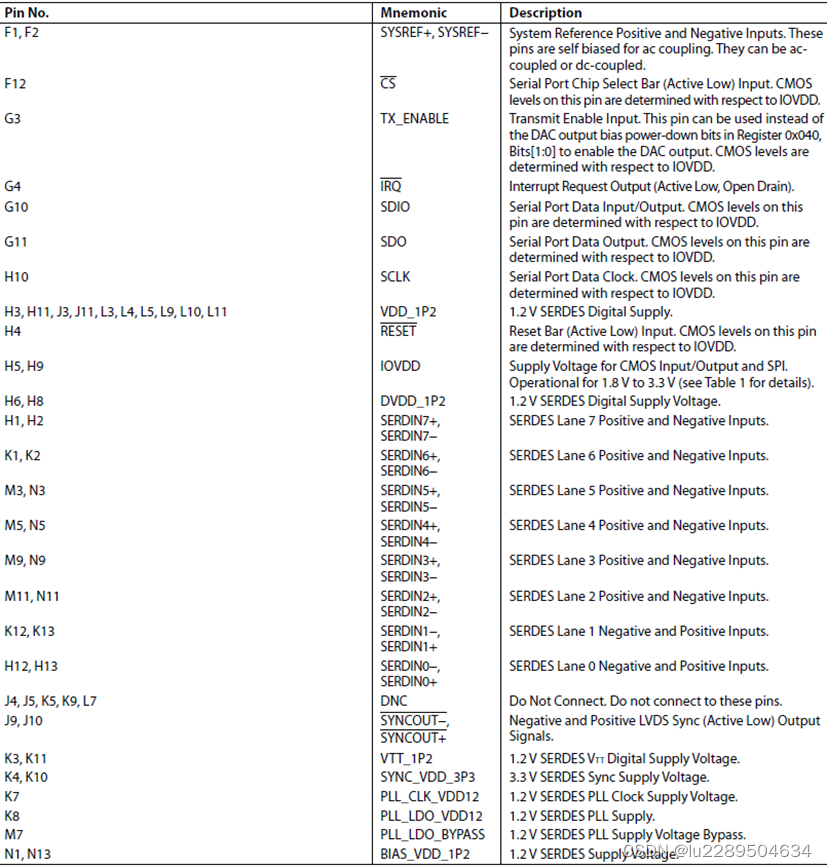

引脚配置和功能描述

典型性能

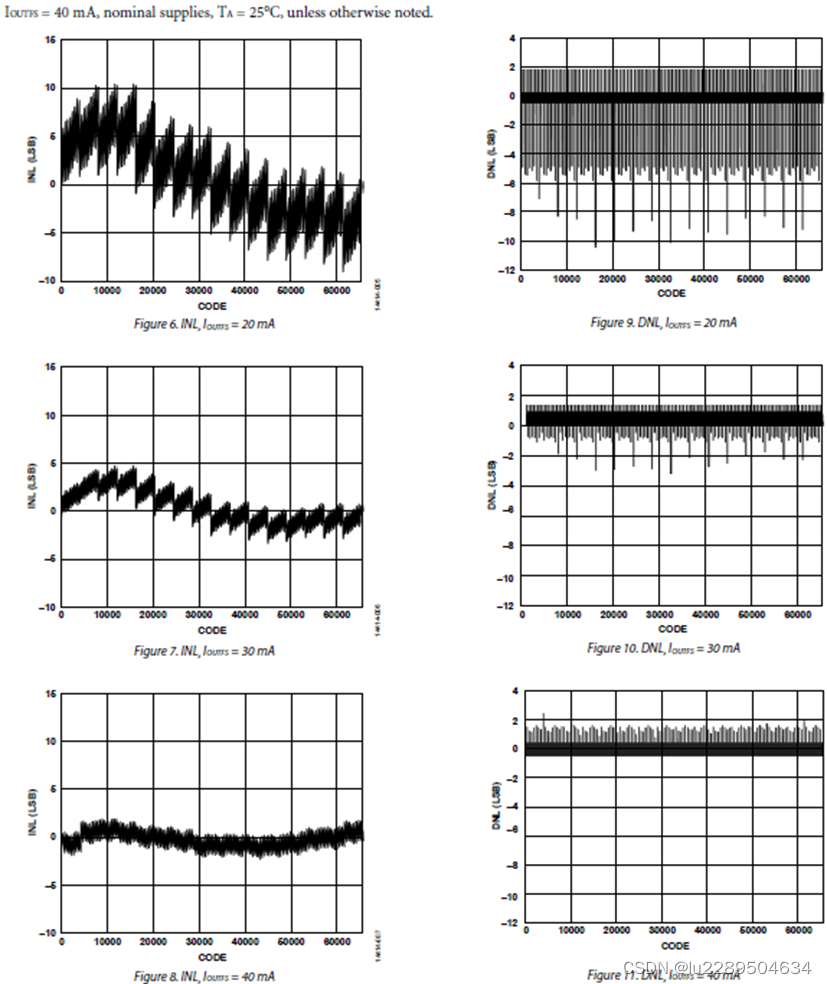

静态线性

随着IOUTFS增大,INL和DNL指标得到优化。

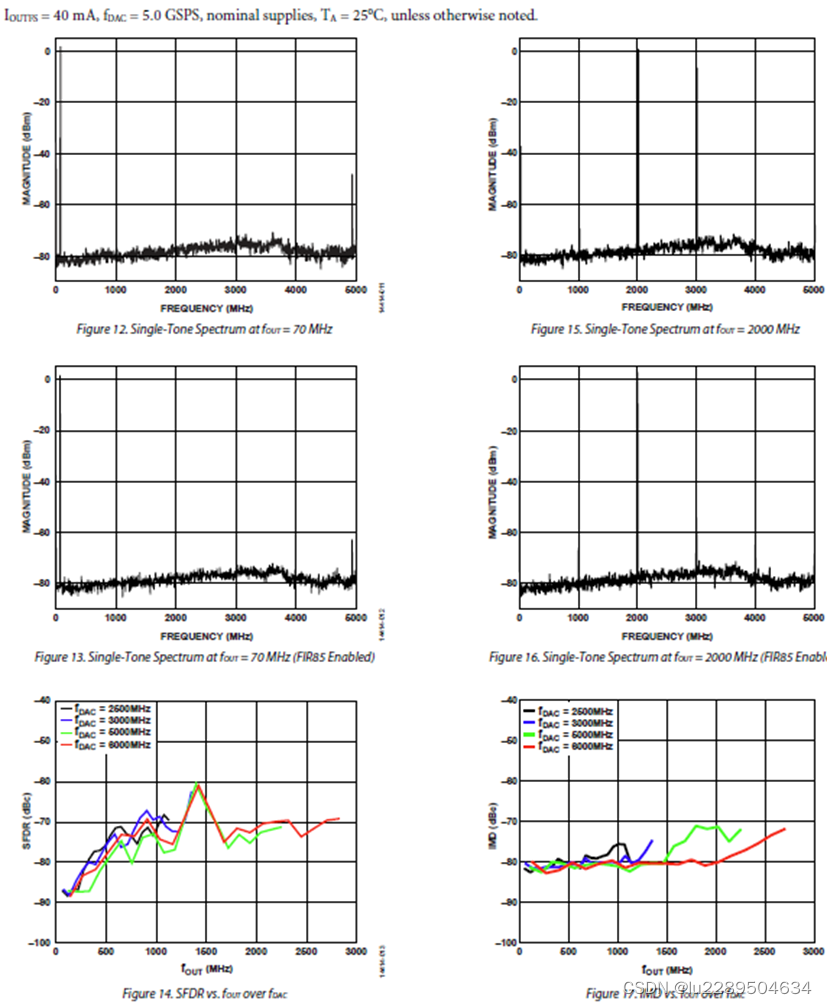

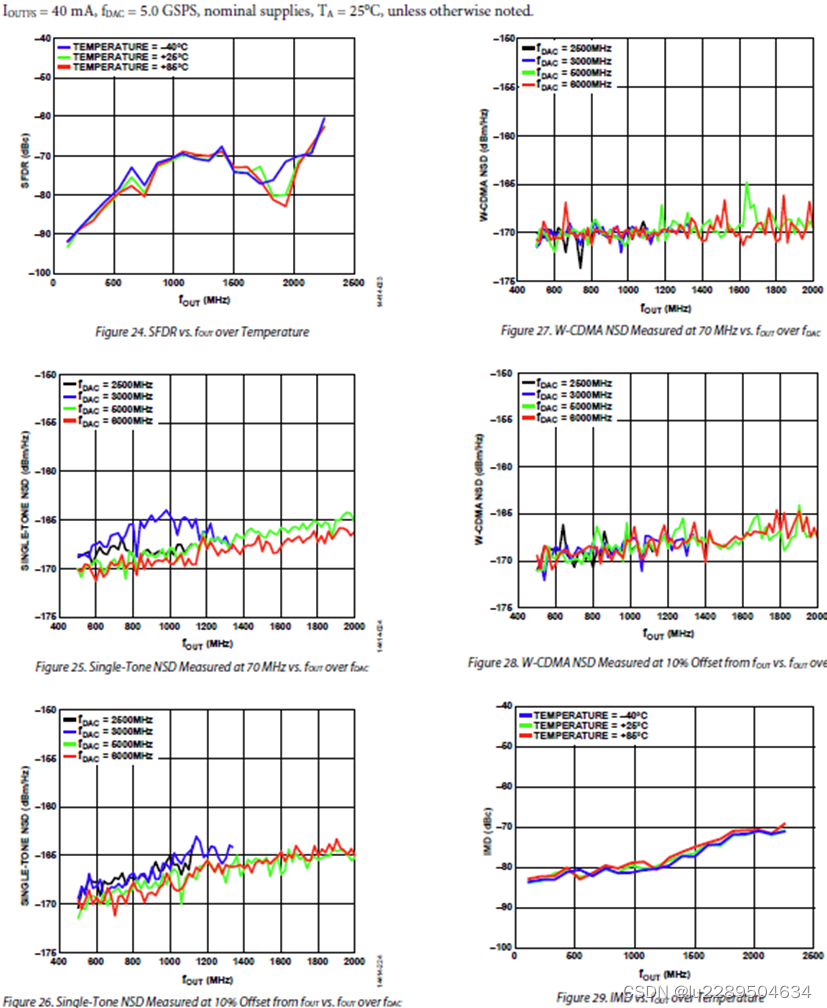

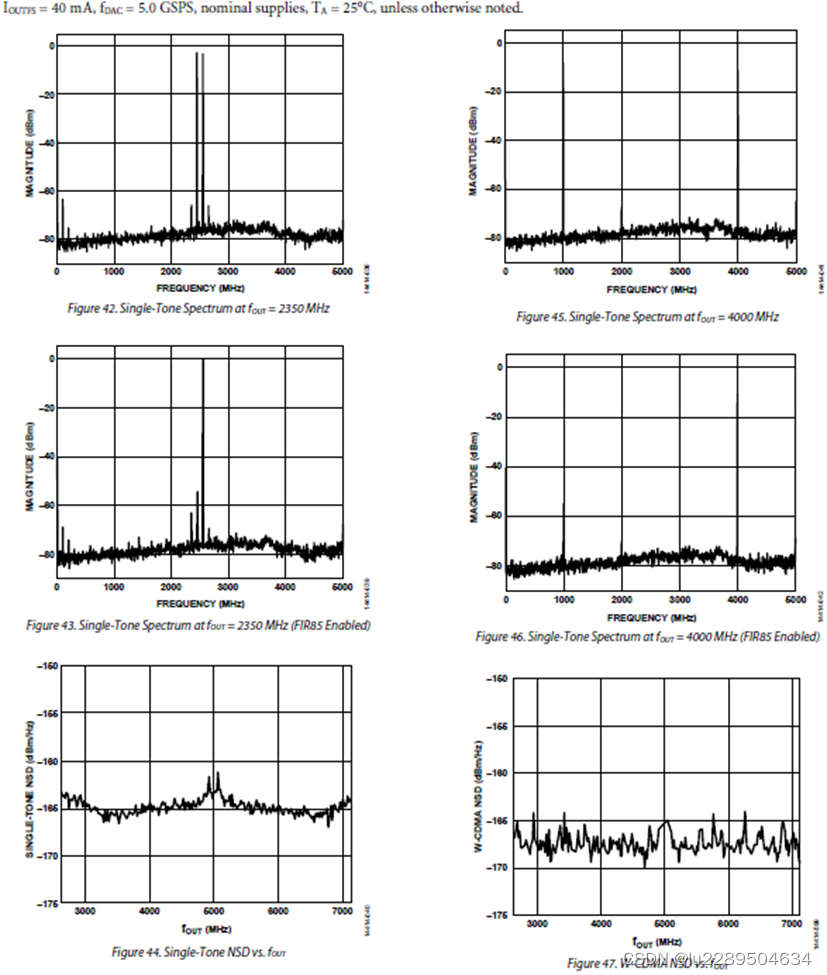

交流性能(NRZ模式)

使能FIR85,对于杂散和镜像指标有所改善

AC(混合模式)

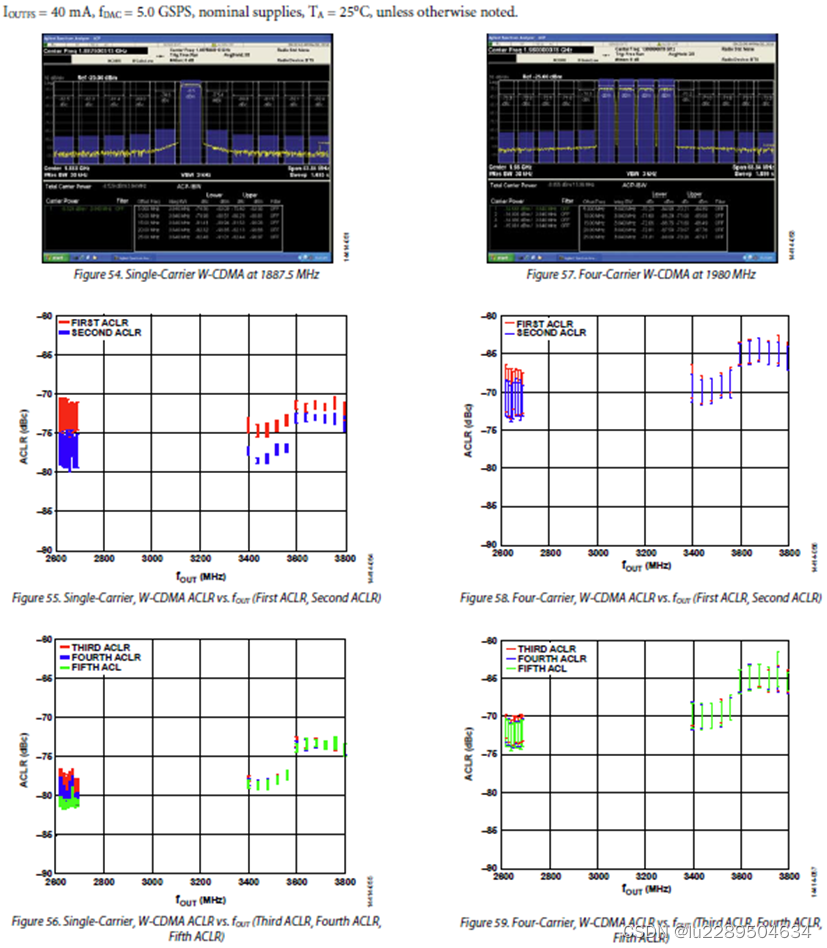

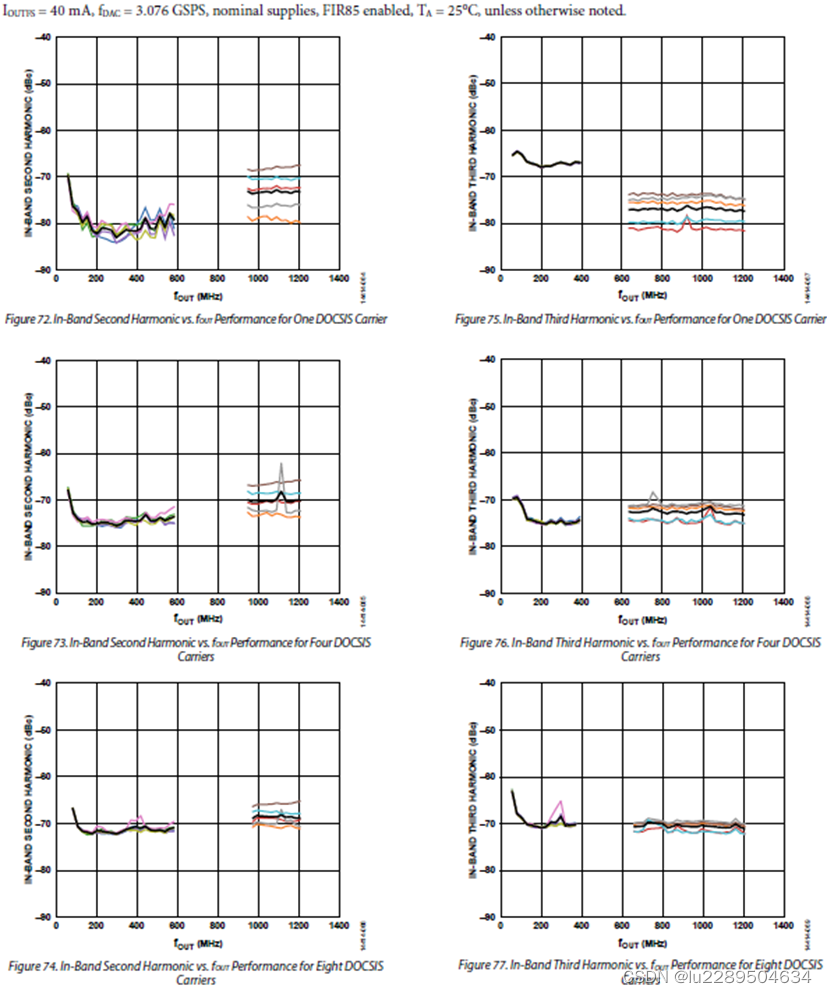

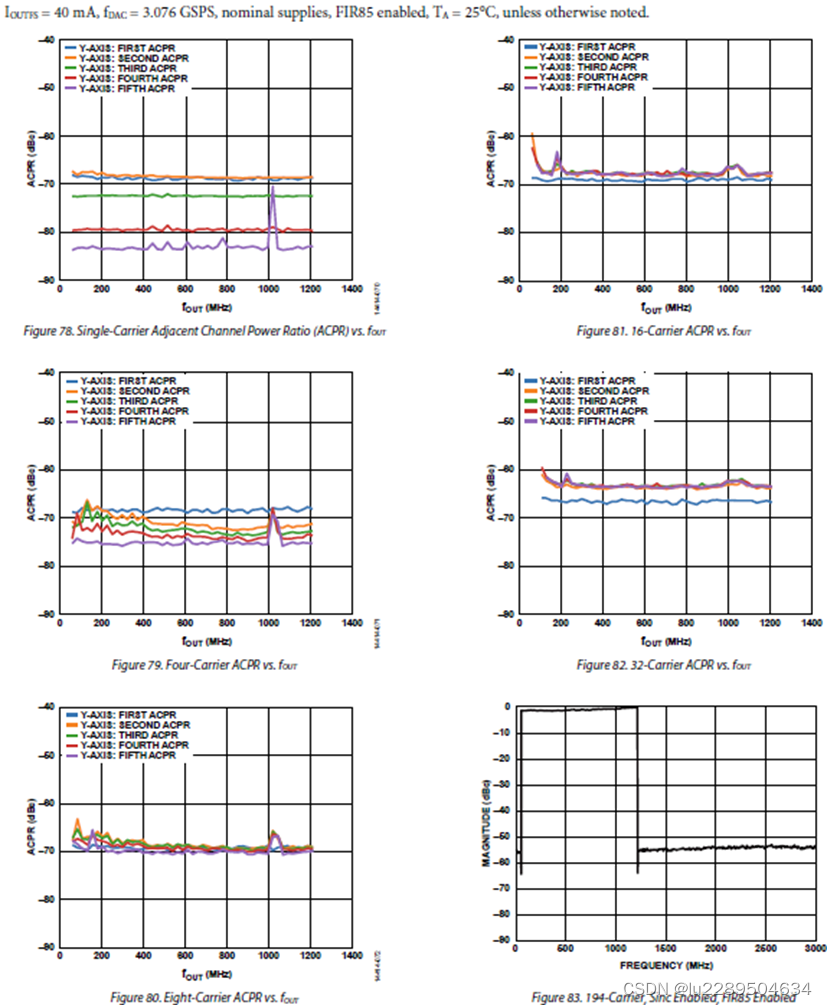

DOCSIS性能(NRZ模式)

术语

积分非线性(INL):表征DAC整体的非线性程度。是实际模拟信号输出与理想输出的最大偏差,由从零刻度到满刻度的直线确定。

微分非线性(DNL):表征DAC局部的非线性程度。是模拟值变化的度量,归一化为满刻度,与数字输入代码中 1 LSB 的变化相关。

偏移误差(Offset error):偏移误差是输出电流与0 mA理想值的偏差。对于output+,当所有输入设置为0时,输出电流理论为0 mA。对于OUTPUT−,当所有输入设置为1时,输出电流理论为0 mA。

增益误差(Gain error):增益误差是实际输出跨度和理想输出跨度之间的差值。实际跨度=输入最大代码时的输出-输入最小代码时的输出。

温度漂移(Temp Drift):环境温度由室温变化至最大或最小温度时,指标的最大变化量。

建立时间(Settling time):从输出转换开始测量,输出稳定在最终值指定误差范围内所需的时间。

杂散动态范围(Spurious-Free Dynamic Range,SFDR):SFDR是输出信号的峰值振幅与DAC直流至奈奎斯特频率范围内的杂散信号峰值之间的差值,单位为分贝。通常,该频带中的能量能够被插值滤波器抑制。因此,该规格定义了插值滤波器的工作性能以及其他寄生耦合路径对DAC输出的影响。

信噪比(Signal-to-Noise Ratio,SNR):SNR是测量输出信号的均方根值与奈奎斯特频率以下所有其他频谱分量(不包括前六次谐波和dc)的均方根和的比值。SNR的值以分贝表示。

插值滤波器(Interpolation Filter):如果DAC的数字输入以插值速率的倍数(fDATA)进行采样,则可构建一个数字滤波器,在 fDATA/2 附近形成一个尖锐的过渡带。通常出现在输出数据速率 (fDAC) 附近的镜像可被大大抑制。

相邻信道泄漏率(Adjacent Channel Leakage Ratio ,ACLR):ACLR 是一个信道内相对于其相邻信道的测量功率与载波(dBc)的比率,单位为dB。

调整后的DAC更新率(Adjusted DAC Update Rate):调整后的DAC更新速率是DAC更新速率除以最小插值因子。为了清楚具有多个插值因子的DAC,可以给出每个插值因子的调整后的DAC更新率。

物理通道(Physical Lane):物理通道x对应SERDINx ±。

逻辑通道(Logical Lane):逻辑通道x指矩阵开关(寄存器 0x308 至寄存器 0x30B)重新映射后的物理通道。

链路通道(Link Lane):链路中所指定的逻辑通道。

关于线性度指标,详见:对ADC(DAC)的线性度(INL和DNL)的一点理解_adc线性度-CSDN博客![]() https://blog.csdn.net/wzk456/article/details/39055215

https://blog.csdn.net/wzk456/article/details/39055215

工作原理

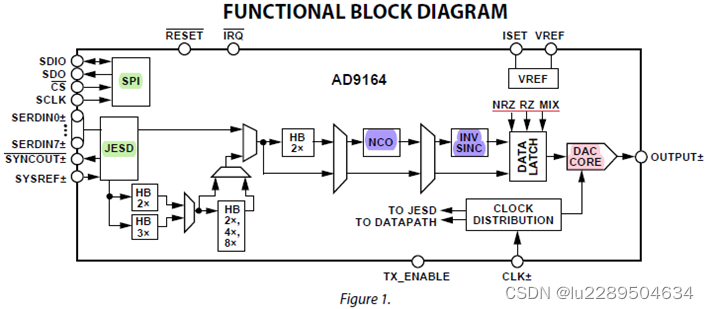

AD9164是一个带有SERDES接口的16位单通道RF DAC和数字上变频器。图1显示了AD9164的功能框图。八个高速串行通道以最高12.5 Gbps的速度传输数据,并且向DAC提供5 GSPS实数输入或2.5 GSPS复数输入数据速率。与LVDS或CMOS接口相比,SERDES接口简化了器件的引脚数、板布局和输入时钟要求。

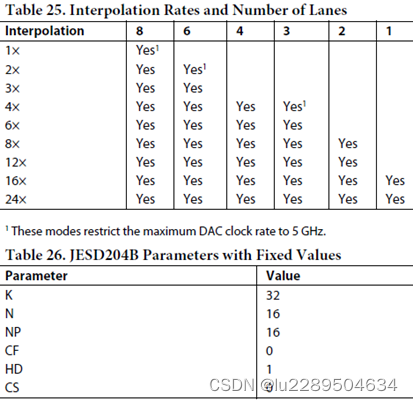

输入数据的时钟来自DAC时钟或芯片时钟(JESD204B规范要求)。芯片时钟来源于高保真度直接外部DAC采样时钟。通过 SPI 端口对时钟输入进行片上调整,可以优化 DAC 的性能。根据所需的输入数据速率,该器件可以配置为在单通道、双通道、三通道、四通道、六通道或八通道模式。

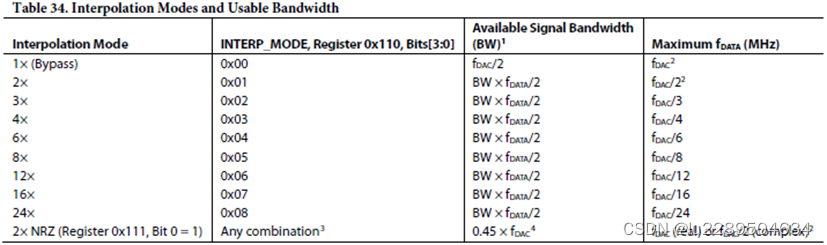

AD9164 的数字数据通路提供旁路 (1×) 模式和多种插值模式(2×、3×、4×、6×、8×、12×、16× 和 24×),通过一个初始半带 (2×) 或第三带 (3×) 滤波器(带宽可编程为 80% 或 90%)以及三个后续半带滤波器(带宽均为 90%)实现,最大DAC采样率为6GSPS。反向sinc滤波器用于补偿sinc函数的滚降。另外一个半带滤波器 FIR85 利用四开关架构在时钟下降沿进行内插,在2× NRZ模式下有效地将 DAC 更新速率提高了一倍。提供48位可编程模数 NCO,以近乎无限的精度实现信号的数字频移。NCO可在NCO模式下单独运行,也可与来自 SERDES 接口和数字数据通路的数字数据一起运行。SPI 写入接口的速度为 100MHz,可快速更新NCO的FTW。

除了主48位NCO外,AD9164还为选定的DDS应用提供了FFH NCO。FFH NCO由32个32位NCO组成,每个NCO具有自己的相位累加器、用于选择其中一个NCO的FTW选择寄存器以及相位相干跳频模式;这些元件共同实现了相位相干FFH。使用FTW选择寄存器和100MHz SPI,可以实现高达260ns的驻留时间。

AD9164 DAC内核提供全差分电流输出,标称满量程电流为38.76 mA。满标度输出电流IOUTFS通常可由用户在8 mA至38.76 mA之间调节。差分电流输出是互补的。DAC使用四开关架构,使DAC解码器选项能够通过混合模式、归零(RZ)模式和2×NRZ模式(启用FIR85)将输出频率范围扩展到第二和第三奈奎斯特区域。混合模式可用于获取1.5 GHz到5 GHz左右的频率。在插值模式中(2×NRZ),使用NCO将瞬时带宽高达 1.8 GHz 的信号搬移到所需的fOUT,输出范围可以从0Hz到6GHz。

AD9164 具有多芯片同步功能,既能同步多个 DAC,又能为 DAC 建立恒定的确定性延迟(延迟锁定)路径。从链路建立到链路建立,每个 DAC 的延迟都保持恒定,不超过几个 DAC 时钟周期。外部对齐(SYSREF±)信号使 AD9164 符合 Subclass 1 标准。系统中可使用多种 SYSREF± 信号处理模式。

SPI配置各种功能块并监控其状态。各种功能块和数据接口必须按照特定的顺序设置,才能正常运行(参见启动顺序部分)。评估板包中包含了设置JESD204B链路的简单SPI初始化例程。本数据表更详细地介绍了AD9164的各个模块。介绍了 JESD204B 接口、控制参数以及用于设置和监控器件的各种寄存器。推荐的启动程序能够可靠地设置数据链路。

SPI串口

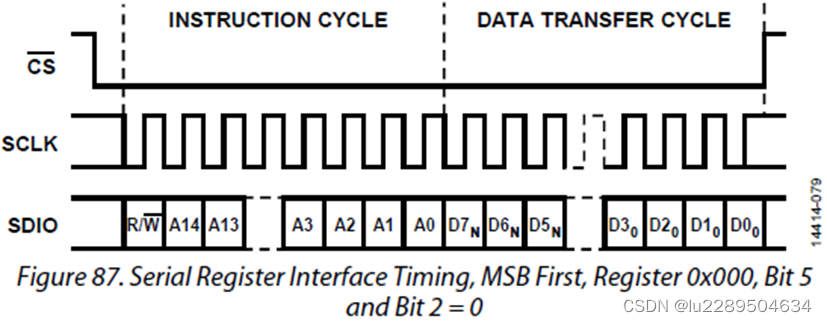

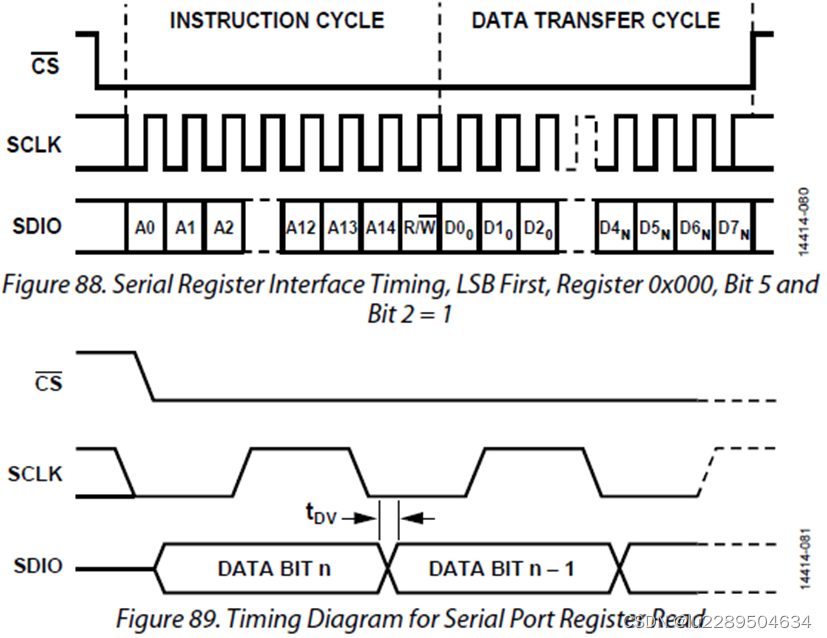

串行端口是一个灵活的同步串行通信端口,可与许多行业标准微控制器和微处理器轻松连接。串行输入/输出(I/O)兼容大多数同步传输格式,包括摩托罗拉 SPI 和英特尔 SSR 协议。该接口允许读/写访问配置 AD9164 的所有寄存器。支持 MSB 优先或 LSB 优先的传输格式。串行端口接口可配置为 4 线接口或 3 线接口,其中3线接口模式中,输入和输出共用一个单引脚 I/O (SDIO)。

|

|

AD9164 的通信周期分为两个阶段。第 1 阶段是指令周期(向设备写入指令字节),与前 16 个 SCLK 上升沿对齐。指令字为串行端口控制器提供有关数据传输周期(通信周期的第 2 阶段)的信息。第 1 阶段指令字定义了即将进行的数据传输是读还是写,以及后续数据传输的起始寄存器地址。

\CS 引脚上的逻辑高电平和随后的逻辑低电平将串行端口时序复位到指令周期的初始状态。在此状态下,接下来的 16 个 SCLK 上升沿代表当前 I/O 操作的指令位。

剩余的 SCLK 边沿用于通信周期的第 2 阶段。第 2 阶段是设备与系统控制器之间的实际数据传输。通信周期的第 2 阶段可传输一个或多个数据字节。在传输周期中,传输 N 个字节需要 8 × N 个 SCLK 周期。写入每个传输字节的最后一位后,寄存器会立即发生变化,但 FTW 和 NCO 相位偏移除外,它们只有在频率调整字 FTW_LOAD_REQ 位被设置时才会发生变化。

串口数据格式

指令字节包含信息如表14所列。

|

|

R/W,指令字的第 15 位,决定指令字写入后是进行读还是写数据传输。逻辑 1 表示读操作,逻辑 0 表示写操作。

A14 至 A0,即指令字的I14位至I0位,决定通信周期数据传输部分访问的寄存器。对于多字节传输,A[14:0] 是起始地址。其余寄存器地址由设备根据地址增量位生成。如果地址增量位设置为高位(寄存器 0x000,位 5 和位 2),则多字节 SPI 写入从 A[14:0] 开始,每发送/接收 8 个位增量 1。如果地址增量位设置为 0,则地址每八位递减 1。

串行端口引脚说明

串行时钟(SCLK)

串行时钟引脚用于同步进出设备的数据,并运行内部状态机。SCLK 的最大频率为 100 MHz。所有数据都在 SCLK 上升沿输入,在 SCLK 下降沿输出。

片选信号(\CS)

低电平启动并开启一个通信周期。\CS 允许在同一串行通信线路上使用多个设备。当该输入为高电平时,SDIO 引脚进入高阻抗状态。在通信周期中,芯片选择必须保持低电平。

串行数据输入/输出(SDIO)

该引脚为双向数据线。在 4 线模式下,该引脚作为数据输入,SDO 作为数据输出。

串行端口选项

串行端口可支持MSB优先和LSB优先两种数据格式。该功能由LSB优先位(寄存器 0x000,位 6 和位 1)控制。默认为MSB优先(LSB位=0)。

当 LSB 位 = 0(MSB 优先)时,指令和数据位必须从 MSB 写入 LSB。R/(\W)之后的 A[14:0] 为指令字,D[7:0] 为数据字。当 LSB 第一位 = 1(LSB 第一位)时,情况正好相反。A[0:14]之后是 R/(\W),之后是 D[0:7]。

串行端口支持 3 线制或 4 线制接口。当 SDO 有效位 = 1 时(寄存器 0x000,位 4 和位 3),使用的是带有独立输入引脚(SDIO)和输出引脚(SDO)的 4 线接口。当 SDO 有效位 = 0 时,SDO 引脚未使用,SDIO 引脚用于输入和输出。

在指令周期后的第一个数据传输字之后的多个数据传输周期(8 个 SCLK)内,将\CS引脚保持为低电平,也可进行多字节数据传输。指令周期后的前8个 SCLK 会读取或写入指令周期中提供的寄存器。在接下来的每8个 SCLK 周期中,地址都会递增或递减,并在新寄存器上进行读/写操作。地址方向可通过 ADDRINC 或 ADDRINC_M(寄存器 0x000,位 5 和位 2)设置。当 ADDRINC 或 ADDRINC_M 为 1 时,地址递增。当 ADDRINC 或 ADDRINC_M 为 0 时,地址将递减。新的写周期总是可以通过将 CS 调至高电平再调至低电平来启动。为防止混淆并确保设备之间的一致性,芯片会测试地址阶段后的第一个字节,而忽略第二个字节。该测试独立于 LSB 第一位完成,并确保在软复位位(寄存器 0x000,位 0 和位 7)之后有额外的时钟周期。对第一个字节的测试仅适用于写入寄存器 0x000。

|

|

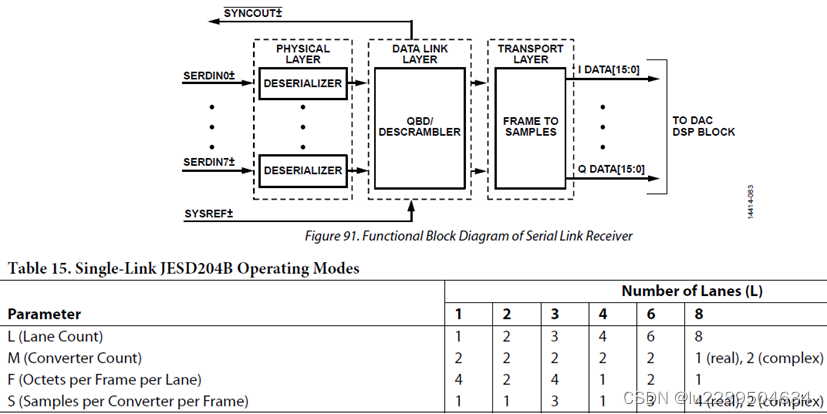

JESD204B串口

JESD204B简述

AD9164 有8个用于接收数据的JESD204B数据端口。 这8个JESD204B端口可配置为单一JESD204B链路(使用单一系统基准SYSREF±和器件时钟CLK±)的一部分。

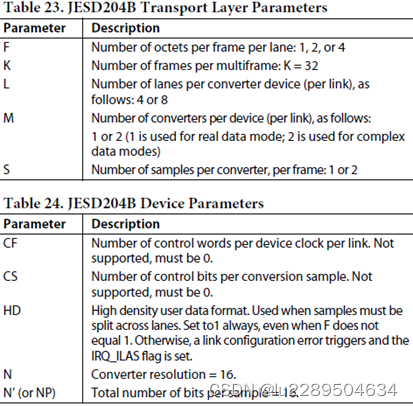

JESD204B 串行接口硬件由三层组成:物理层、数据链路层和传输层。这些硬件部分将在后续章节中介绍,包括配置接口各个方面的信息。图 91 显示了 AD9164串行数据接口中实现的通信层,这些层用于在数据发送到芯片的数字信号处理模块(DSP)之前,恢复时钟并对数据进行解串、解扰和解帧。传输层接收解扰后的JESD204B帧,并将其转换为DAC样本。一些JESD204B参数(L、F、K、M、N、NP、S、HD)定义了数据的打包方式,并告诉芯片如何将串行数据转换为样本。传输层部分对这些参数进行了详细定义。AD9164 还具有可选的解扰功能(更多信息请参阅解扰器部分)。

M——每个器件的转化数(每个AD或DA的转换通道数);

N——转换分辨率(AD采样位数)

N’——所需半字节总的位数,即所需nibble数乘以4,也可称为协议的字长(word size);

S——每一帧所传输的采样数;

L——数据传输的通道(lane)数量;

F——每一帧的字节数(octets);

K——多帧模式下,表示一包数据有多少帧,取值范围为1-32;

JESD204B的配置参数完全取决于所使用的通道数。因此,可以通过选择要使用的通道数来确定一组独特的参数。此外,插值速率和通道数可用来定义设置 AD9164 所需的其他配置。插值速率和通道数在寄存器0x110中选择。

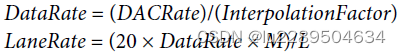

AD9164有单个DAC输出;但是,为了在芯片上进行复数信号处理,只要使用插值,转换器数量就定义为 M = 2。对于特定应用,使用的转换器数量 (M)和数据速率(DataRate)是已知的。通道速率和通道数 (L)可按以下方式进行权衡:

其中LaneRate必须介于750 Mbps和12.5Gbps之间(此处默认N’=16,且进行8B/10B编码)。

实现和恢复通道同步非常重要。为了简化与发射器的接口,AD9164为每个JESD204B 链路指定了一个主同步信号。SYNCOUT±引脚用作所有通道的主信号。如果链路中的任一通道失去同步,则会通过链路的同步信号向发送器发送重新同步请求。发送器停止发送数据,转而向该链路中的所有通道发送同步字符,直至实现重新同步。

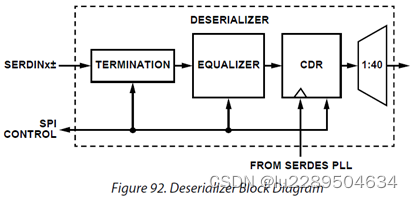

物理层

JESD204B 接口的物理层(以下称为解串器)有八个相同的通道。每个通道由终端器、均衡器、时钟和数据恢复 (CDR) 电路以及 1:40 解复用功能块组成(见图 92)。

根据 JESD204B 规范,JESD204B 数据通过SERDINx±1.2 V差分输入引脚输入AD9164。

|

接口上电和输入终端

在使用 JESD204B 接口之前,必须通过设置寄存器0x200的第0位=0来上电。此外,必须关闭每个不使用的物理通道(PHY)(SERDINx±)的电源。为此,如果物理通道正在使用,则将寄存器0x201中物理通道x的相应位x设置为0;如果未使用,则将其设置为1。

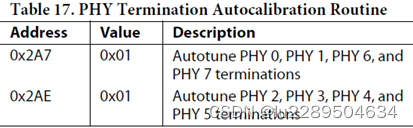

AD9164会将输入终端自动校准到50 Ω。在运行终端校准之前,必须按照表 17 中的说明写入寄存器 0x2A7 和寄存器 0x2AE,以确保正确校准。当寄存器0x2A7位0和寄存器 0x2AE位0从低电平转换为高电平时,终端校准开始。寄存器 0x2A7控制PHY0、PHY1、PHY6和PHY7的自动校准。寄存器0x2AE控制PHY2、PHY3、PHY4 和 PHY5的自动校准。

PHY终端自动校准例程如表17所示。

|

DAC 的输入终端电压从外部通过 VTT_1P2 引脚(8 mm × 8 mm 封装上的球 M3 和球 M13,或 11 mm × 11 mm 封装上的球 K3 和球 K11)获取。将 VTT(终端电压)连接至 VDD_1P2,设置 VTT。建议使用 100 nF 电容将 JESD204B 输入与 JESD204B 发送设备进行交流耦合。

可以从寄存器0x2AC(PHY 0、PHY 1、PHY 6、PHY 7)和寄存器0x2B3(PHY 2、PHY 3、PHY 4、PHY 5)中的位[3:0]读取终端的校准码。如果需要,可以使用几个寄存器调整或设置终端值。TERM_BLKx_CTRLREG1寄存器(寄存器0x2A8和寄存器0x2AF)可以覆盖自动校准值。当设置为0xXXX0XXXX时,终端自动校准,这是正常的默认设置。当设置为0xXXX1XXXX时,自动校准值将被寄存器0x2A8和寄存器0x2AF的位[3:1]中的值覆盖。可以在寄存器0x2BB到寄存器0x2C2的位[3:0]中对每个通道自校准值的单独偏移量进行编程。该值是一个带符号的幅度,其中位3为符号位。终端阻抗的总范围约为94Ω至120Ω,整个范围内的增量约为3.5%(例如,范围底部的步长小于顶部的步长)。

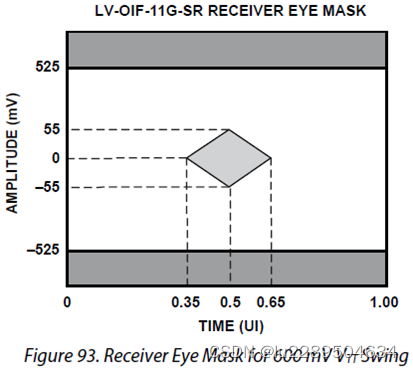

接收器眼图波罩

AD9164符合关于接收器眼图波罩的JESD204B规范,并且能够捕获符合该眼图波罩的数据。图93显示了在600 mV VTT摆动的情况下,归一化为数据速率间隔的接收器眼图波罩。请参阅JESD204B规范,了解有关眼图波罩和允许的接收器睁眼的更多信息。

时钟关系

数据速率(DataRate)=DAC速率/插值因子;

通道速率(LaneRate)=(20*数据速率*M)/L;

字节速率(ByteRate)= LaneRate/10;

这种关系来自8位/10位编码,其中每个字节由10位表示。

处理时钟(PCLK Rate) = ByteRate/4

处理时钟用于四字节解码器。

FrameRate = ByteRate/F

其中F被定义为每个通道每帧的八位字节数。

PCLK Factor = FrameRate/PCLK Rate = 4/F

其中,M是JESD204B参数中每个链路的转换器数量。L是JESD204B参数中每个链路的通道数。F是JESD204B参数中每个通道每帧八位字节的数量。

Serdes PLL

独立的SERDES PLL使用整数N分频来实现时钟合成。整个SERDES PLL集成在芯片上,包括VCO和环路滤波器。SERDES PLL VCO在6 GHz到12.5 GHz的范围内工作。

在SERDES PLL中,VCO分频模块将VCO时钟除以2以生成用于解串器内核的3GHz~6.25GHz正交时钟。该时钟作为时钟模块和数据恢复模块的输入。

SERDES PLL的参考时钟(fREF)总是以通道速率(PCLK速率)的1/40的频率运行。该时钟除以DivFactor(由SERDES_PLL_DIV_FACTOR设置),生成一个频率在35MHz~80MHz之间的时钟信号,送至鉴相器模块(PFD)。表18给出了每个期望的PLL_REF_CLK_RATE选项所对应的SERDES_PLL_DIV_FACTOR(图94中的CDR OVERSAMP REG)寄存器设置。

寄存器0x280控制合成器的启用和重新校准。要启用SERDES PLL,首先设置PLL分频器寄存器(见表18)。然后通过写入寄存器0x280,位0=1来启用SERDES PLL。如果需要重新校准,写入寄存器0x280,位2=0b1,然后将该位重置为0b0。该位的上升沿触发重新校准。

通过读取寄存器0x281确认SERDES PLL正在工作。如果寄存器0x281,位0=1,则SERDES PLL已锁定。如果寄存器0x281,位3=1,则SERDES PLL已成功校准。如果寄存器0x281,Bit 4或Bit 5为高电平,则PLL到达其校准频带的下端或上端,并且必须通过向寄存器0x280,Bit 2先写入0再写入1来重新校准。

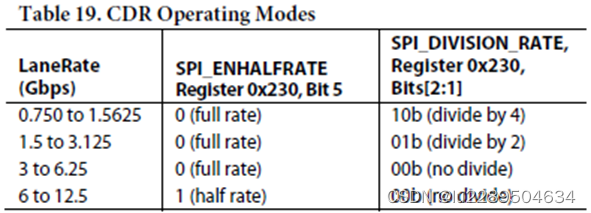

时钟及数据恢复(CDR)

解串器配备有CDR电路。CDR不是从JESD204B串行通道恢复时钟,而是从SERDES PLL恢复时钟。SERDES PLL的3 GHz至6.25 GHz输出,如图94所示,是CDR的输入。必须选择CDR采样模式才能在设备内生成通道速率时钟。如果期望的通道速率大于6.25GHz,则必须使用半速率CDR操作。如果所需的通道速率小于6.25 GHz,则禁用半速率操作。如果通道速率小于3 GHz,则禁用全速率并启用2×过采样以恢复适当的通道速率时钟。表19列出了根据LaneRate值必须设置的CDR采样设置。

CDR电路可独立完成各串行通道的相位(用于数据采样)同步工作。每个串行接口的这种独立相位调整机制确保了准确地数据采样,并简化了PCB上多个串行接口的实现。配置CDR电路后,需重置,然后通过向寄存器0x206的位0先写1再写0释放重置。

关闭未使用的PHY

请注意,任何未使用和启用的通道都会消耗不必要的额外电力。每个未使用的通道(SERDINx±)必须通过向PHY_PD(寄存器0x201)的相应位写入1来关闭电源。

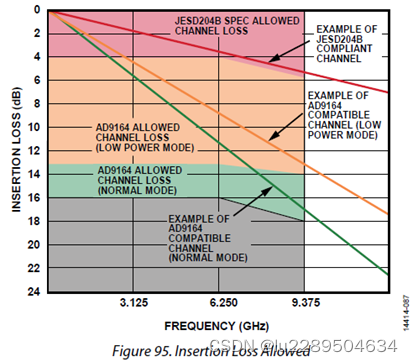

均衡器

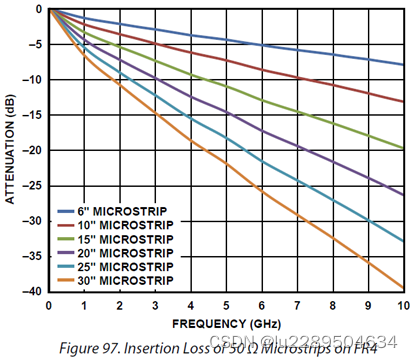

为了补偿由于PCB迹线长度和阻抗导致的每个PHY信道的信号完整性失真,AD9164在每个JESD204B信道上采用了易于使用的低功率均衡器。AD9164均衡器可以补偿远远大于JESD204B规范要求的插入损耗。均衡器有两种操作模式,由寄存器0x268中的EQ_POWER_MODE寄存器设置Bits[7:6]确定。在低功耗模式下(寄存器0x268,Bits[7:6]=2b'01),并且以12.5 Gbps的最大通道速率操作,均衡器可以补偿高达11.5 dB的插入损耗。在正常模式下(寄存器0x268,Bits[7:6]=2b'00),均衡器可以补偿高达17.2 dB的插入损耗。这种性能如图95所示,是JESD204B插入损耗规范的叠加。图95显示了12.5 Gbps的均衡性能,接近AD9164的最大波特率。

图96和图97是硬件设计师的参考点,分别显示了不同长度布局良好的带状线和微带传输线的插入损耗。有关JESD204B通道的具体布局建议,请参阅硬件注意事项部分。如果JESD204B PCB通道的插入损耗小于低功耗模式所支持的最大通道插损值,则建议使用低功耗模式(如图95所示)。如果插入损耗大于此值,但仍小于正常模式所支持的最大通道插损值(如图95所示),则使用正常模式。在12.5Gbps操作下,正常模式下的均衡器比低功耗模式下的均衡器,每个通道多消耗约4mW的功率。请注意,任何一种模式都可以与发射机预加重结合使用,以确保功能和/或优化功率。

数据链路层

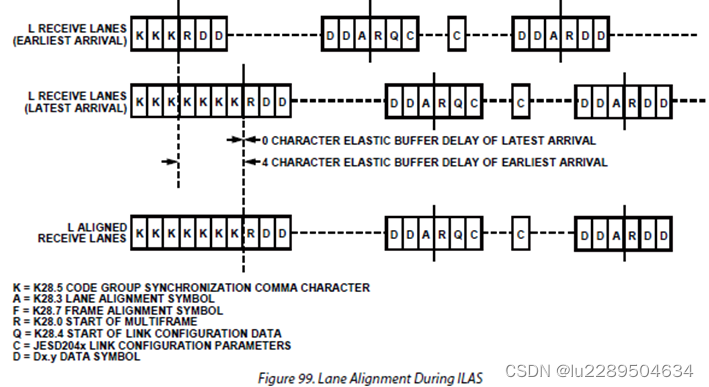

AD9164芯片JESD204B接口的数据链路层接收来自PHY和解帧的解串数据,并对它们进行解扰,使得数据以8字节形式(octets)被呈现给传输层,进而作为DAC采样样本。数据链路层的体系结构如图98所示。数据链路层由每个通道的同步FIFO、矩阵开关、解帧器和解扰器组成。AD9164可以作为单链路高速JESD204B串行数据接口运行。JESD204B接口的所有8个通道均可处理链路层通信,例如代码组同步(CGS)、帧对齐和帧同步。AD9164可解码8位/10位控制字符,从而标记帧的开始和结束,并在串行通道之间进行对齐。每个AD9164串行接口链路可以通过将其\SYNCOUT±信号设置为低电平来发出同步请求。同步协议遵循JESD204B标准的第4.9节。当接收到连续四个/K/符号流时,AD9164通过在下一个内部LMFC上升沿将\SYNCOUT±信号置高来停用同步请求。然后,AD9164等待发射器发出初始通道对准序列(ILAS)。在ILAS期间,如JESD204B串行链路建立部分所述,使用/A/到/R/字符转换来对齐所有通道。弹性缓冲区保存早期到达的通道数据,直到最新通道的对齐字符到达。此时,释放所有通道的缓冲区,并对齐所有通道(见图99)。

K=K28.5代码组同步逗号字符

A=K28.3车道线形符号

F=K28.7帧对齐符号

R=K28.0多帧启动

Q=K28.4链路配置数据的开始

C=JESD204x链路配置参数

D=Dx.y数据符号

JESD204B串行链路建立

下面简要介绍子类 1 的高速串行链路建立过程。详情请参见 JESD204B 规范文件第 5.3.3 节。

第一步:代码组同步

每个接收器必须在其输入数据流中定位/K/(K28.5)字符。在所有链路通道上检测到连续四个/K/字符后,接收器模块在接收器LMFC边沿取消向发射器块发送\SYNCOUT±信号。发射机捕捉\SYNCOUT±信号的变化,并在发射机LMFC上升沿启动ILAS。

第二步:初始化通道排列顺序

此阶段目的为对齐一个链路中的所有通道,并验证链路参数。在建立链路之前,将每个链路参数写入接收器设备,以指定如何将数据发送到接收器块。

ILAS由四个或更多的多帧组成。每个多帧的最后一个字符是一个多帧对齐字符/a/。第一、第三和第四个多帧填充的是数据值。请注意,JESD204B规范文件第8.2节描述了ILAS期间预期的数据斜坡。AD9164不需要此斜坡。解帧器使用每个通道的最终/A/来对准接收器内的多帧的末端。第二个多帧包含/R/(K.28.0)、/Q/(K.28.4),然后是与链路参数相对应的数据。如果接收机需要,可以向ILAS添加额外的多帧。默认情况下,AD9164在ILAS中使用四个多帧(这可以在寄存器0x478中更改)。如果使用子类1,则必须使用恰好四个多帧。在最后一个ILAS的最后一个/A/字符之后,多帧数据开始流式传输。接收器调整/A/字符的位置,使其与此时接收器的内部LMFC对齐。

第三步:数据流

在这个阶段,数据从发送器块流式传输到接收器块。

可选地,可以对数据进行加扰。ILAS之后的第一个8位字节才开始加扰。

接收器块处理并监控其接收到的数据是否存在错误,包括以下错误:

•运行差错(8位/10位错误)

•不在表中(8位/10位错误)

•意外的控制字符

•不良ILAS

•行间偏移错误(通过字符替换)

如果存在这些错误中的任何一个,则通过以下方式之一将其报告给发射器模块(有关详细信息,请参阅JESD204B错误监测部分):

•发送\SYNCOUT±信号:对于最后两个错误,每次出错时都会请求重新同步(\SYNCOUT±信号拉低)。对于前三个错误,当错误计数器达到设置的错误阈值时,可以发送一个可选的重新同步请求。

•对于前三个错误,每个有错误的多帧都会在\SYNCOUT±上产生一个小脉冲。

•错误可以选择性地触发中断请求(IRQ)事件,并发送到发射器。

有关验证链路完整性的各种测试模式的更多信息,请参阅JESD204B测试模式部分。

通道先进先出(FIFO)

矩阵开关和解帧器前面的FIFO通过调整输入数据的相位,将高速串行数据接口上发送的样本与解帧器时钟同步。FIFO吸收数据源和解帧器之间的时序变化;这使得发送器最多可以有两个 PCLK 周期的漂移。可以监控FIFO_STATUS_REG_0寄存器和FIFO_STAT US_REG_1寄存器(分别为寄存器0x30C和寄存器0x30D),以识别FIFO是满的还是空的。

通道FIFO 中断请求

总通道的FIFO错误位也可用作IRQ事件。使用寄存器0x020,位2启用FIFO错误位,然后使用寄存器0x024,位2读回其状态并重置IRQ信号。有关更多信息,请参阅中断请求操作部分。

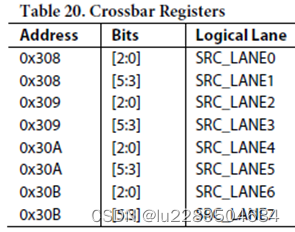

矩阵开关

寄存器0x308到寄存器0x30B允许将物理通道(SERDINx±)任意映射到SERDES解帧器使用的逻辑通道。用所需物理通道(SERDINx±)的编号(x)写入每个SRC_LANEy,从中获取数据。默认情况下,所有逻辑通道都使用相应的物理通道作为数据源。例如,默认情况下,SRC_LANE0=0;因此,逻辑通道0从物理通道0获得数据(SERDIN0±)。要使用SERDIN4±作为逻辑通道0的源,用户必须写入SRC_LANE0=4。

通道反向

寄存器0x334允许反向所需的逻辑通道,可用于简化SERDINx±信号的路由。对于每个逻辑通道x,将寄存器0x334的位x设置为1以将其反向。

解帧器

(用于解析和还原JESD数据流的模块,具备解析JESD数据流的能力,可以提取出其中的数据、时钟和控制信号)

AD9164由一个4字节解帧器(QBD)组成。解帧器接收来自解串器的8比特/10比特编码数据(通过交叉开关),对其进行解码,并在将其传递到传输层用于转换为DAC样本之前将其解扰为JESD204B帧。解帧器每个处理时钟周期(PCLK)处理四个符号(或八位字节)。

解帧器使用用户已编程到寄存器映射中的JESD204B参数来识别数据是如何打包和解包的。传输层部分详细描述了JESD204B参数;在传输层中还需要许多参数来将JESD204B帧转换为样本。

解扰器

AD9164提供了一个可选的解扰器块,使用具有以下多项式的自同步解扰器:1+x14+x15。启用数据加扰可以减少当相同的8bit数据从一帧到另一帧重复时产生的频谱峰值。它还使频谱数据独立,从而使电接口上出现可能的频率选择性效应,进而不会导致数据相关误差。通过将SCR位(寄存器0x453,位7)设置为1来启用数据解扰。

同步本地多帧时钟(LMFC)信号

保证链路和设备之间同步的第一步是同步LMFC信号。在子类0中,LMFC信号与内部处理时钟同步。在子类1中,LMFC信号与外部SYSREF±信号同步。

SYSREF±信号

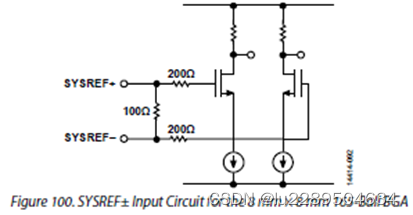

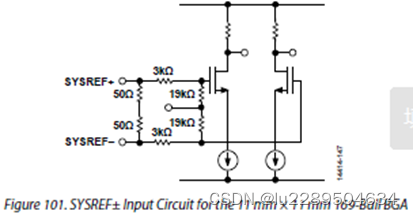

SYSREF±信号是一个差分源同步输入,用于同步JESD204B子类1系统中发射器和接收器中的LMFC信号,以实现确定性延迟。SYSREF±信号是一个由设备时钟上升沿采样的上升沿敏感信号。推荐设计为:设备时钟和SYSREF±信号由同一个源生成,例如HMC7044时钟生成器,这样信号之间的相位对齐是固定的。在设计最佳确定性延迟操作时,应考虑多点链路系统(多芯片)中SYSREF±信号的时序分布偏差。

AD9164支持周期性SYSREF±信号。周期可以是连续、选通或间隙周期。SYSREF±信号可以始终直流耦合(共模电压为0 V至1.25 V)。当直流耦合时,从SYSREF±引脚会产生少量共模电流(<500μA)。SYSREF±内部电路见图100和图101。为避免这种共模电流消耗,可使用占空比为 50%、带有交流耦合电容的周期性SYSREF±信号。如果交流耦合,交流耦合电容与图100或图101中所示的电阻器组合成一个RC时间常数为τ=RC的高通滤波器。选择C,使τ>4/SYSREF±频率。此外,边缘速率必须足够快,以满足SYSREF±与DAC时钟保持窗口(KOW)的要求。

通过使用SYSREF±滞后(寄存器0x088和寄存器0x089),可以在不满足频率-时间常数约束(τ=RC和τ>4/SYSREF±频率)的情况下使用交流耦合模式。然而,使用滞后会使DAC时钟KOW(表6不适用)增加一个量,该量取决于SYSREF±频率、滞后水平、电容器选择和边缘速率。

同步处理模式概述

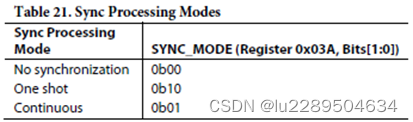

AD9164支持多种LMFC同步处理模式。这些模式包括一次性、连续和监控模式。所有同步处理模式都执行相位检查,以确认LMFC与对准边缘相位对齐。在子类1中,SYSREF±上升沿充当对齐边;在子类0中,内部处理时钟充当对齐边缘。SYSREF±信号由DAC时钟/4进行采样。在对SYSREF±进行采样后, DAC时钟/4的相位作为温度计代码存储在寄存器0x037,Bits[7:0]和寄存器0x038,Bits[3:0]中。SERDES数据发送器(例如,FPGA)可以使用该偏移来对齐多个DAC(在发送数据时考虑该时钟偏移)。同步模式如下所述。有关同步LMFC信号的过程的详细信息,请参阅同步过程部分。

一次同步模式(SYNCMODE=寄存器0x03A,Bits[1:0]=0b10)

在一次同步模式中,相位检查仅发生在同步机待命后接收的第一个对准边缘上。相位在第一个边缘对齐后,AD9164转换到监控模式。尽管LMFC同步只发生一次,SYSREF±信号仍然可以是连续的。在这种情况下,相位被监测和报告,但不发生时钟相位调整。

连续同步模式(SYNCMODE=寄存器0x03A,Bits[1:0]=0b01)

连续模式必须在第1子类中使用,且仅支持周期性SYSREF±信号。在连续模式中,相位检查/对齐发生在每个对齐边缘上。连续模式与单次同步模式有两个不同之处。首先,不需要SPI循环配置设备;在启用连续模式之后,监测到的对齐边缘会进行相位检查。其次,在连续模式下,每个对齐边沿都会进行相位检查。

监视器同步模式(SYNCMODE=寄存器0x03A,Bits[1:0])=0b00)

在监测模式下,用户可以实时监测相位误差。将此同步模式与周期性SYSREF±信号一起使用。对相位进行监测和报告,但不进行时钟相位调整。当出现对齐请求(SYSREF±边缘)时,最后一个相位误差的信息被放入可读寄存器中以供参考(寄存器0x037和寄存器0x038,位[3:0]),并在酌情设置IRQ_SYSREF_JITTER中断。

同步过程

启用同步的过程如下:

1. 设置 DAC;SERDES PLL 锁定 DAC 并启用 CDR(参见启动顺序部分)。

2. 设置寄存器 0x039(SYSREF± 抖动窗口)。建议至少设置四个 DAC 时钟周期。设置见表 22。

3. 可选择回读 SYSREF± 计数,检查是否接收到 SYSREF± 脉冲。

a. 设置寄存器 0x036 = 0。向 SYSREF_COUNT 写入任何内容都将重置计数。

b. 设置寄存器 0x034 = 0。向 SYNC_LMFC_STAT0 写入任何内容都将保存数据以供回读并记录计数。

c. 从寄存器 0x036 中的值读取 SYSREF_COUNT。

4. 执行一次同步。

a. 设置寄存器 0x03A = 0x00。如果已启用,则清除单次同步模式。

b. 设置寄存器 0x03A = 0x02。启用单次同步模式。同步发生后,状态机进入监控模式。

5. 可选择回读同步 SYNC_LMFC_STATx 寄存器,以验证同步是否正确完成。

a. 设置寄存器 0x034 = 0。必须写入寄存器 0x034 才能读取该值。

b. 读取寄存器 0x035 和寄存器 0x034 以查找 SYNC_LMFC_STATx 的值。建议将 SYNC_LMFC_STATx 设置为 0,但也可设置为 4,或由于抖动而将 LMFC 周期设置为 DAC 时钟 - 4。

6. 可选择回读同步 SYSREF_PHASEx 寄存器,以确定 SYSREF± 采样使用的是DAC时钟/4的哪个相位。读取寄存器 0x038 和寄存器 0x037 作为温度计代码。寄存器 0x037 位[7:4]的 MSB 通常显示温度计代码值。

7.开启链路(寄存器0x300,位0=1)。

8.回读寄存器0x302(动态链路延迟)。

9. 重复建立链路数次(步骤1至步骤7),并记下动态链路延迟值。根据这些值,对LMFC延迟(寄存器0x304)和LMFC变量(寄存器0x306)进行编程,然后重新启动链路。

两个最低有效数字被忽略,因为SYSREF±信号是用DAC时钟/4采样的。因此,抖动窗口是通过这个除以4的时钟而不是DAC时钟来设置的。建议至少选择一个4-DAC时钟SYSREF±抖动窗口。

确定性延迟

JESD204B系统包含分布在整个系统中的各种时钟域。数据从一个时钟域穿越到另一个时钟域时,会导致 JESD204B 链路出现不明确的延迟。这些不明确性会导致每次新链路建立时,从电源周期到电源周期的链路延迟不可重复。JESD204B 规范第 6 节通过定义为子类 1 和子类 2 的机制来解决确定性延迟问题。

AD9164支持JESD204B子类0和子类1操作,但不支持子类2。将子类写入寄存器0x458,Bits[7:5]。

子类0

此模式在32个DAC时钟周期内提供确定性延迟。它不需要SYSREF±引脚上的任何信号,可以保持断开状态。子类0仍然要求所有通道在相同的LMFC周期内到达,并且双DAC必须彼此同步。

子类1

此模式提供确定性延迟,并允许链路在四个DAC时钟周期内同步。它需要一个与DAC时钟精确相位对准的外部SYSREF±信号。

确定性延迟要求

在JESD204B子类1系统中实现确定性延迟需要几个关键因素。

•系统内的SYSREF±信号分布偏差必须小于所需的不确定性。

•系统中的每个设备都必须满足SYSREF±设置和保持时间要求。

•所有通道、链路和器件的总延迟变化必须≤10 PCLK周期,既包括可变延迟,也包括系统中不同通道、不同链路和不同设备之间固定延迟的变化。

链路延迟

JESD204B系统的链路延迟是发射机、信道和接收机的固定和可变延迟的总和,如图102所示。

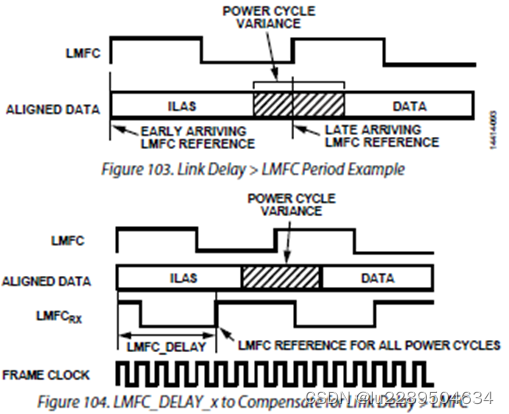

为了正常运行,必须在同一LMFC期间读取链路上的所有通道。JESD204B规范第6.1节规定,LMFC周期必须大于最大链路延迟。对于AD9164,情况并非如此;相反,AD9164为每个链路(LMFCRx)使用一个本地LMFC,该链路可以从与SYSREF±对齐的LMFC延迟产生。因为LMFC是周期性的,所以这种延迟可以解释任何数量的固定延迟。因此,LMFC周期仅必须大于链路延迟的变化,这样AD9164就能以较小的总延迟实现适当的性能。图103和图104显示了链路延迟大于LMFC周期的情况。请注意,它可以通过延迟LMFCRx来适应。

选择LMFCDel(寄存器0x304)和LMFCVar(寄存器x306)变量的方法在链路延迟设置示例的“已知延迟”部分中进行了描述。

适当地设置LMFCDel可以确保所有相应的数据样本在相同的LMFC周期内到达。然后LMFCVar被写入接收缓冲器延迟(RBD)以吸收所有链路延迟变化。此写入操作可确保所有数据样本在读取之前都已到达。通过在运行和设备之间将这些设置为固定值,可以实现确定性延迟。

JESD204B规范中描述的RBD取值范围为1个帧时钟周期到K个帧时钟周期,而AD9164的RBD取值范围为0个PCLK周期到10个PCLK周期。因此,可以吸收多达10个PCLK周期的总延迟变化。LMFCVar 和 LMFCDel 均以PCLK周期为单位。PCLK因子(每个PCLK 周期的帧时钟周期数)等于4/F。有关此关系的详细信息,请参阅“时钟关系”部分。

下面的两个示例显示了如何确定LMFCVar和LMFCDel。计算完它们后,将LMFCDel写入系统中所有设备的寄存器0x304,并将LMFCVar写入系统内所有设备的注册表0x306。

具有已知延迟的链路延迟设置示例

所有已知的系统延迟均可以用于计算LMFCVar和LMFCDel。

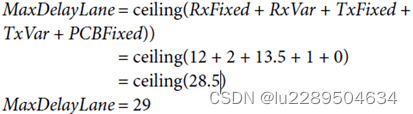

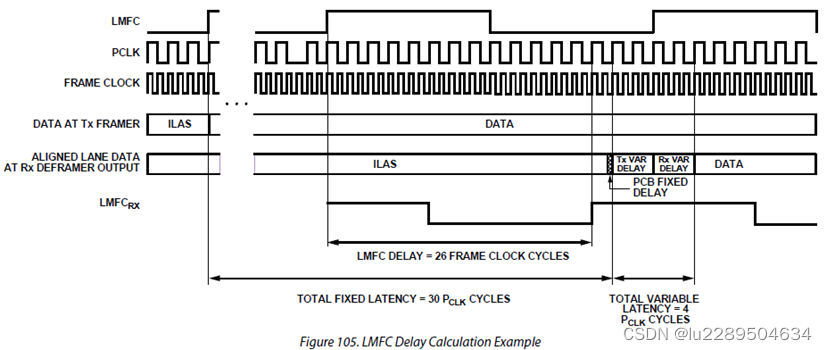

下面的步骤演示了图105中所示的示例。请注意,本例采用子类 1 以实现确定性延迟,其 PCLK 因子 (4/F) 为每个 PCLK 周期2个帧时钟周期,并使用 K = 32(帧/多帧)。由于 PCBFixed << PCLK 周期,PCBFixed 在本例中可忽略不计,也不包括在计算中。

1.使用表7查找接收器延迟。

RxFixed=12个PCLK周期

RxVar=2个PCLK周期

2.查找发射器延迟。JESD204B内核示例(在Virtex-6 FPGA上的GTH或GTX千兆收发器上实现)中的等效表指出,延迟为56±2字节时钟周期。

3. 由于 PCLK速率 = ByteRate/4(如时钟关系部分所述),以 PCLK 周期为单位的发送器延迟计算如下:

4. 计算 MinDelayLane 的方法如下:

5. 计算 MaxDelayLane的方法如下:

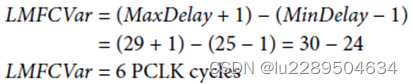

6. 计算 LMFCVar的方法如下:

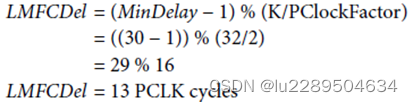

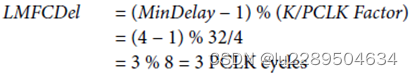

7. 计算 LMFCDel如下:

8. 将系统中所有设备的 LMFCDel 写入寄存器 0x304。将系统中所有设备的 LMFCVar 写入寄存器 0x306。

具有未知延迟的链路延迟设置示例

如果不知道系统延迟,AD9164可以读回每个链路的LMFCRX和与SYSREF±对齐的 LMFC之间的链路延迟。然后利用该信息计算 LMFCVar 和 LMFCDel。

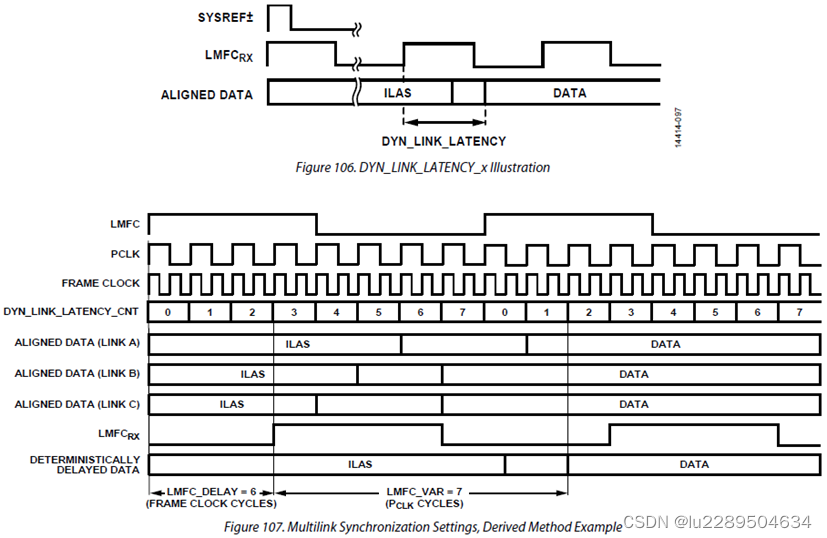

图 107 显示 DYN_LINK_LATENCY_0(寄存器 0x302)如何提供回读,该回读显示LMFCRX 与从 ILAS 过渡到第一个数据采样之间的延迟(以 PCLK 周期为单位)。通过反复进行功率循环和测量,可以确定跨功率循环的最小和最大延迟,并用于计算 LMFCVar 和 LMFCDel。

在图 107 中,对于链路 A、链路 B 和链路 C,对包含 AD9164 的系统(包括发射机)进行了 20 次电源循环和配置。AD9164 的配置如同步程序部分所述。由于本实验的目的是确定 LMFCDel 和 LMFCVar,因此将 LMFCDel 值编程为 0,并从寄存器 0x302 读取 DYN_LINK_ LATENCY_0 值。图 107 显示了 20 次运行过程中链路延迟的变化,说明如下:

- 链路 A 的回读值为 6、7、0 和 1。 请注意,记录的一组延迟值在 K/ PCLK 因子 = 8 的边界处越过了多帧的边缘。 由于 0 和 1 的回读值越过了多帧的边缘,因此将每个多帧的 PCLK 周期数 = 8 加到 0 和 1 的回读值上。延迟值范围为 6 至 9。

- 链路 B 的延迟值为 5 至 7。

- 链路 C 的延迟值为 4 至 7。

图 107 所示的示例按以下步骤演示。请注意,该示例采用子类 1 来实现确定性延迟,其 PCLK 因子(帧速率 ÷ PCLK 速率)为 4,使用 K = 32;因此每个多帧的 PCLK 周期 = 8。

1. 计算所有功率周期、链路和设备的所有延迟测量值的最小值,如下所示:

![]()

2. 计算所有电源周期、链路和设备的所有延迟测量值的最大值,计算公式如下:

![]()

3. 计算所有功率周期、链路和设备的总延迟变化(带保护带)如下:

![]()

4. 计算所有电源周期、链路和设备的 PCLK 周期(带保护带)最小延迟如下:

5. 将系统中所有设备的 LMFCDel 写入寄存器 0x304。将系统中所有设备的 LMFCVar 写入寄存器 0x306。

传输层

传输层接收解扰后的 JESD204B 帧,并根据表 23 所示的 JESD204B 编程参数将其转换为 DAC 样本。表 24 中定义了设备参数。

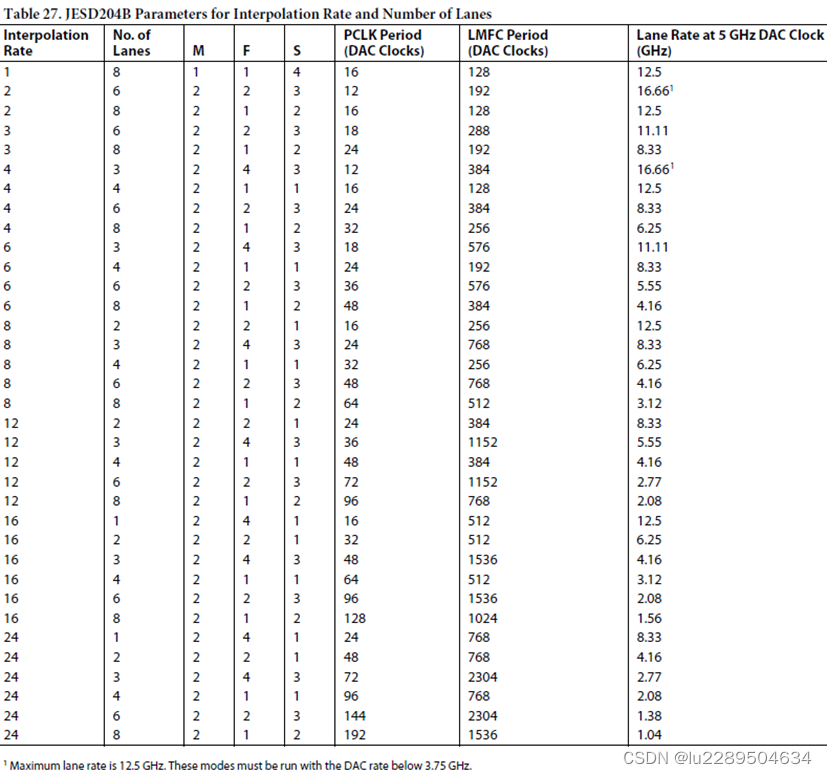

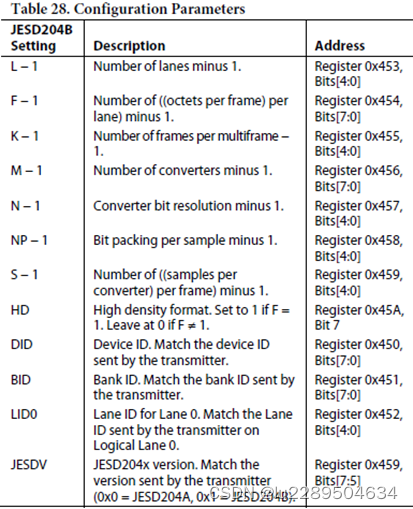

AD9164 支持这些参数的某些组合。表27列出了支持的插值速率以及每种插值速率所支持的通道数,并给出了 5 GHz DAC 时钟的通道速率示例。表 26 列出了具有固定值的 JESD204B 参数。如果表 25 中的值为 "是",则表示支持该通道数的插值速率。空白单元表示不支持。

配置参数

AD9164 模式参考了 L、K、M、N、NP、S 和 F 的链路配置参数。 表 28 提供了这些设置的说明和地址。

通过 JESD204B 接收器的数据流

链路配置参数决定了 JESD204B 接收器接口上的串行比特如何解扰并作为数据样本传送到 DAC。

纠偏和启用逻辑通道

正确配置后,逻辑通道会自动纠偏。所有逻辑通道是否启用取决于寄存器0x110,位[7:4]中的通道编号设置。默认情况下,所有物理通道都已通电。

要禁用未使用的物理通道的电源,可将寄存器0x201中的位x设置为1以禁用物理通道x,将其保持为0以启用物理通道 x。

JESD204B 测试模式

物理层 PRBS 测试

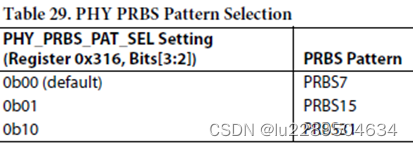

AD9164 上的 JESD204B 接收器在其物理层后端包含一个 PRBS 模式校验器。该功能可对 JESD204B 链路的每个物理通道进行误码率 (BER) 测试。物理层 PRBS 模式检查器不需要建立 JESD204B 链路。它可以与 PRBS7、PRBS15 或 PRBS31 数据模式同步。PRBS 模式验证可同时在多个通道上进行。故障通道的错误计数每次只报告一条 JESD204B 通道。在 AD9164 上执行 PRBS 测试的流程如下:

1. 开始从 JESD204B 发送器发送 PRBS7、PRBS15 或 PRBS31 模式。

2. 如表 29 所示,选择并向寄存器 0x316,位[3:2]写入适当的 PRBS 模式。

3. 通过写入 PHY_TEST_EN(寄存器 0x315)启用所有被测通道的 PHY 测试。寄存器 0x315 的每一位都会启用相应通道的 PRBS 测试。例如,向第0位写入1将启用物理通道 0的PRBS测试。

4. 将 PHY_TEST_RESET(寄存器 0x316,位 0)从 0 切换为 1,然后再切换回 0。

5. 根据需要设置 PHY_PRBS_TEST_THRESHOLD_xBITS(寄存器 0x319 至寄存器 0x317 的位[23:0])。

6. 向 PHY_TEST_START(寄存器 0x316,位 1)写入 0,然后再写入 1。PHY_TEST_START 的上升沿开始测试。

a. (可选)在某些情况下,此时可能需要重复步骤 4。将 PHY_TEST_RESET(寄存器 0x316,位 0)从 0 切换到 1,然后再切换回 0。

7. 等待 500 毫秒。

8. 写入PHY_TEST_START(寄存器0x316,位 1)= 0,停止测试。

9. 读取PRBS测试结果。

a. PHY_PRBS_PASS(寄存器0x31D)的每一位对应一个SERDES通道(0 =失败,1= 通过)。

b. 通过在 PHY_SRC_ERR_CNT(寄存器 0x316,位[6:4])中写入要检查的通道编号(0 至 7)并读取 PHY_PRBS_ERR_COUNT(寄存器 0x31C 至寄存器 0x31A),可读取每个故障通道上出现的 PRBS 错误数。最大错误计数为 224 - 1。如果寄存器 0x31C 至寄存器 0x31A 的所有位均为高电平,则所选通道上的最大错误计数被超出。

传输层测试

AD9164 中的 JESD204B 接收器支持 JESD204B 标准中描述的短传输层 (STPL) 测试。该测试可用于验证 JESD204B 发射器和接收器之间的数据映射。要执行该测试,必须在逻辑器件中实现并启用该功能。在接收器端运行测试之前,链路必须已建立且运行无误。

STPL 测试确保根据转换器数量(M)和每个转换器的采样数量(S)对每个转换器的每个采样进行适当映射。根据 JESD204B 标准的规定,转换器制造商指定传输哪些测试样本。每个样本必须有一个唯一的值。例如,如果 M = 2,S = 2,则会重复传输四个唯一的样本,直到测试停止。预期样本必须编程到设备中,然后将预期样本与接收到的样本进行比较,每次一个样本,直到全部测试完毕。在 AD9164 上执行此测试的过程如下:

1. 同步 JESD204B 链路。

2. 在 JESD204B Tx 启用 STPL 测试。

3. 根据 JESD204B 的情况,最多可能有两个 DAC,每个帧最多可能包含四个 DAC 采样。配置 SHORT_TPL_REF_SP_MSB 位(寄存器 0x32E)和 SHORT_TPL_REF_SP_LSB 位(寄存器 0x32D),以匹配一个帧内一个转换器的其中一个采样。

4. 设置 SHORT_TPL_SP_SEL(寄存器 0x32C,位[7:4]),以根据表 30 为所选转换器选择一帧内的采样。

5. 将 SHORT_TPL_TEST_EN(寄存器 0x32C,位 0)设为 1。

6. 将 SHORT_TPL_TEST_RESET(寄存器 0x32C,位 1)设为 1,然后返回 0。

7. 等待所需的时间。所需时间的计算公式为 1/(采样率×误码率)。例如,给定误码率 BER = 1 × 10-10 和采样率 = 1 GSPS,则所需时间 = 10 秒。

8. 在 SHORT_TPL_FAIL 中读取测试结果(寄存器 0x32F,位 0)。

9. 为同一个或另一个转换器选择另一个采样,继续进行测试,直到验证完一帧中两个转换器的所有采样。(请注意,在 AD9164 的所有细分模式下,转换器计数为 M = 2,以便进行复数信号处理)。

测试采样排列指南请参见表 30。请注意,1×八通道模式的采样顺序是采样 1 和采样 2 对调。此外,三线和六线选项的 STPL 测试不起作用,总是失败。

1 Mx 是转换器编号,Sy 是采样编号。例如,M0S0 表示转换器 0,采样 0。 SPx 是采样模式字编号。例如,SP0 表示采样模式字 0。

重复 CGS 和 ILAS 测试

根据 JESD204B 规范第 5.3.3.8.2 节,AD9164 可检查是否接收到恒定的 /K28.5/ 字符流,或是否接收到 CGS 后的恒定 ILAS 流。

要运行重复 CGS 测试,请向 AD9164 SERDES 输入发送恒定的 /K28.5/ 字符流。接下来,设置设备并启用链路。通过读取寄存器 0x470 来验证 \SYNCOUT±是否断电以及 CGS 是否通过所有启用的链路通道,从而确保接收到 /K28.5/ 字符。

要在运行 CGS 之后重复进行 ILAS 序列测试,请按照设置链路的步骤进行,但在执行最后一次写入(启用链路)之前,通过向寄存器 0x477 第 7 位写入 1 来启用 ILAS 测试模式。然后,启用链路。当设备识别到每个通道上的四个 CGS 字符时,它将取消\SYNCOUT±。此时,发送器开始发送重复的 ILAS 序列。

读取寄存器 0x473,验证所有启用的链路通道是否通过了初始通道同步。

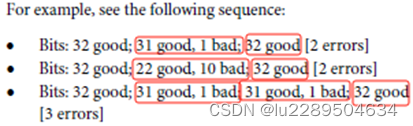

JESD204B 错误监控

不一致、不在表中和意外控制 (K) 字符错误

根据 JESD204B 规范的第 7.6 节,AD9164 可检测差异错误、不在表中 (NIT) 错误和意外控制字符错误,并可在发生错误时发出同步请求和重新初始化链路。

请注意,差异错误计数器会计算所有无效差异字符,无论它们是否在 8 位/10 位解码表中。这与 JESD204B 规范略有不同,后者只计算 8 位/10 位解码表中的差异错误。

本节将介绍对 JESD204B 规范的其他几种解释。当一个通道注入三个 NIT 错误且 QUAL_RDERR(寄存器 0x476,位 4)= 1 时,坏差异错误 (BDE) 计数寄存器的回读值为 1。对于 NIT 错误后字符中的差异错误,则不会禁用。因此,NIT 错误可能会导致 BDE 错误。

当寄存器 0x476 位 4 = 1 注入四个 NIT 错误时,将触发重新同步。当该位被设置时,错误计数器不会区分同时出现的具有错误运行差异但在 8 位/10 位解码表中的无效符号和 NIT 错误。因此,当注入四个 NIT 错误时,可能会触发重新同步,因为这些错误无法与差异错误区分开来。

检查错误计数

错误计数可检查差异错误、NIT 错误和意外控制字符错误。错误计数以每个通道和每个错误类型为基础。每个错误类型和通道都有一个专用寄存器。要检查错误计数,必须执行以下步骤:

1. 在寄存器 0x480,位[5:3]至寄存器 0x487,位[5:3]中选择并启用要监控的错误。如寄存器映射中所述,通过向相应位写入 1,可为每个通道选择意外 K (UEK) 字符、BDE 和 NIT 错误监控。这些位默认为启用。

2. 相应的错误计数器复位位位于寄存器 0x480 位[2:0]至寄存器 0x487 位[2:0]中。向相应位写入 0 可重置该错误计数器。

3. 寄存器 0x488,位[2:0]至寄存器 0x48F,位[2:0]具有每个错误计数器的终端计数保持指示符。如果启用该标志,当达到 0xFF 的终端错误计数时,计数器将停止计数并保持该值直至复位。否则,计数器将返回 0x00,并继续计数。选择所需的行为,并对每个通道的相应寄存器位进行编程。

检查错误次数是否超过阈值

要检查错误次数是否超过阈值,请按照以下步骤操作:

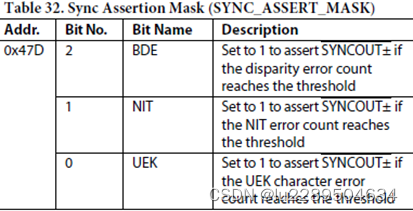

1. 定义错误计数阈值。错误计数器阈值可设置为寄存器 0x47C 中用户定义的值,或保留为默认值 0xFF。当达到错误阈值时,根据掩码寄存器的设置,将产生 IRQ 或 \SYNCOUT±,或同时产生 IRQ 和 \SYNCOUT±。这一个错误阈值用于所有三种类型的错误(UEK、NIT 和 BDE)。

2. 设置 SYNC_ASSERT_MASK 位。SYNCOUT± 断言行为在寄存器 0x47D,位[2:0]中设置。默认情况下,当任何车道的错误计数器等于阈值时,都会断言\SYNCOUT±(寄存器 0x47D,位[2:0] = 0b111)。

3. 读取达到的错误计数指示器。每个错误计数器的每个通道都有一个终端计数达到指示器。当某一车道的错误计数器的终端计数已达到时,该指示器被置 1。这些状态位位于寄存器 0x490 位[2:0]至寄存器 0x497 位[2:0]中。这些寄存器还通过设置位 3 = 0b1 来指示特定车道是否处于活动状态。

错误计数器和 IRQ 控制

关于错误计数器和 IRQ 控制,请按以下步骤操作

1. 启用中断。启用 JESD204B 中断。UEK、NIT 和 BDE 错误计数器的中断位于寄存器 0x4B8,位[7:5]。启动链路时,还需要监控其他中断,如车道纠偏、初始车道同步、良好检查和、帧同步、代码组同步(寄存器 0x4B8,位[4:0])和配置不匹配(寄存器 0x4B9,位 0)。这些位默认为关闭,但可通过向相应位写入 0b1 来启用。

2. 读取 JESD204B 中断状态。中断状态位位于寄存器 0x4BA,位[7:0]和寄存器 0x4BB,位 0,状态位位置与使能位位置相对应。

3. 建议在启动 JESD204B 链路之前启用所有计划使用的中断。链路启动后,可以重置中断,然后用于监控链路状态。

通过 \SYNCOUT±监控错误

当出现一个或多个差异、NIT 或意外控制字符错误时,将根据 JESD204B 规范第 7.6 节的规定在 \SYNCOUT±引脚上报告错误。JESD204B 规范规定,当发生错误时,\SYNCOUT±信号将在两个帧周期内保持有效。对于 AD9164,\SYNCOUT±脉冲的宽度可编程为 ½、1 或 2 个 PCLK 周期。表 31 列出了实现 \SYNCOUT±脉冲两个帧时钟周期的设置。

1 这些寄存器设置声明\SYNCOUT±信号为两个帧时钟周期脉冲宽度。

意外控制字符、NIT、不一致IRQ

对于 UEK 字符、NIT 和色差错误,错误计数超过阈值事件可作为 IRQ 事件使用。通过写入寄存器 0x4B8,位[7:5]来启用这些事件。启用 IRQ 后,可通过寄存器 0x4BA,位[7:5]读取 IRQ 事件状态。

有关重置 IRQ 的信息,请参阅错误计数器和 IRQ 控制部分。有关 IRQ 的更多信息,请参阅中断请求操作部分。

需要重新初始化的错误

根据 JESD204B 规范第 7.1 节的规定,当收到四个无效差异字符时,链路将自动重新初始化。发生链路重初始化时,重同步请求的长度为五个帧九个八位字节。

当不一致错误、NIT 错误或 UEK 字符错误的错误计数达到可编程的错误阈值时,用户可选择重新初始化链路。针对某些错误类型启用重新初始化功能的过程如下:

1. 在寄存器 0x480,位[5:3]至寄存器 0x487,位[5:3]中选择并启用要监控的错误。如表 46 所述,可通过向相应位写入 1 来为每个通道选择 UEK、BDE 和 NIT 错误监控。这些默认为启用。

2. 根据表 32,通过向 SYNC_ASSERT_MASK(寄存器 0x47D,位[2:0])写入内容,为每种类型的错误启用同步断言屏蔽。

3. 将所需的错误计数阈值写入 ERRORTHRES(寄存器 0x47C)。

4. 对于 SYNC_ASSERT_MASK 寄存器中启用的每种错误类型,如果任何车道上的错误计数器达到编程阈值,SYNCOUT± 就会下降,发出同步请求。请注意,所有错误计数都会在链路重新初始化时重置。IRQ 不会重置,必须手动重置。

CGS、帧同步、校验和 ILAS 监控

可对寄存器 0x470 至寄存器 0x473 进行监控,以验证 JESD204B 链路建立的每个阶段是否都已发生。

如果链路通道 x 收到至少四个 K28.5 字符并通过码组同步,则 CODE_GRP_SYNC(寄存器 0x470)的位 x 为高电平。

如果链路巷 x 完成了初始帧同步,则 FRAME_SYNC(寄存器 0x471)的位 x 为高电平。

如果通过通道发送的校验和与链路 x 的 ILAS 期间通过通道发送的 JESD204B 参数之和相匹配,则 GOOD_CHECKSUM(寄存器 0x472)的 x 位为高电平。如果寄存器 0x300,位 6 = 0(默认),则计算的校验和为以下字段之和的低八位: DID、BID、LID、SCR、L - 1、F - 1、K - 1、M - 1、N - 1、SUBCLASSV、NP - 1、JESDV、S - 1 和 HD。如果寄存器 0x300,位 6 = 1,计算出的校验和是寄存器 0x400 至寄存器 0x40C 和 LID 之和的低八位。

如果链路车道 x 通过了初始车道对齐序列,INIT_LANE_SYNC(寄存器 0x473)的位 x 为高。

CGS、帧同步、校验和 ILAS IRQ

CGS、帧同步、校验和以及 ILAS 的故障信号可作为 IRQ 事件使用。通过写入寄存器 0x4B8,位[3:0]来启用它们。启用 IRQ 后,可通过寄存器 0x4BA,位[3:0]读取 IRQ 事件状态。向寄存器 0x4BA 位 0 写 1,重置 CGS IRQ。向寄存器 0x4BA 位 1 写 1,重置帧同步 IRQ。向寄存器 0x4BA,位 2 写 1,重置校验和 IRQ。向寄存器 0x4BA 位 3 写 1 复位 ILAS IRQ。

更多信息,请参阅 "中断请求操作 "部分。

配置不匹配 IRQ

AD9164 有一个配置不匹配标志,可作为 IRQ 事件使用。使用寄存器 0x4B9 位 0 启用不匹配标志(默认情况下已启用),然后使用寄存器 0x4BB 位 0 读回其状态并复位 IRQ 信号。更多信息,请参阅 "中断请求操作 "部分。

当链路配置设置(寄存器 0x450 至寄存器 0x45D)与 JESD204B 传输设置(寄存器 0x400 至寄存器 0x40D)不匹配时,配置不匹配事件标志为高电平。

该功能与寄存器 0x472 中的良好校验和标志不同。良好校验和标志确保传输校验和与根据传输设置计算的校验和相匹配。配置不匹配事件确保传输的设置与配置的设置相匹配。

硬件注意事项

有关硬件注意事项的信息,请参阅应用信息部分。

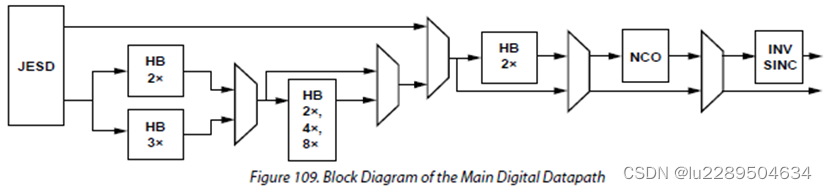

主数字数据通路

图109给出了主数字数据通路原理框图。数字处理包括一个可选择旁路1×、2×或3×插值的输入插值块,三个额外的2×半带插值滤波器,一个可旁路的2×NRZ模式插值滤波器FIR85,以及一个由48位NCO和反向sinc块组成的正交调制器。

所有插值滤波器都接受同相(I)和正交(Q)数据流作为复数数据流。类似地,正交调制器和反向sinc函数也接受作为复数数据流的输入数据。因此,使用数字数据路径函数要求输入数据是复数数据流。在旁路模式(1×插值)下,输入数据流应为真实数据。

通道延迟随着所选的数字数据路径函数而变化。每个块的通道延迟示例见表33。这些延迟是对JESD204B延迟的补充。

1. 给定的流水线延迟是一个代表性的数字,并且可以基于启动时的内部切换定时条件而变化一两个周期。

2. N/A表示未使用。

数据格式

AD9164上所有模式的输入数据格式为16位二进制补码。数字数据路径和DAC解码器以二进制补码格式操作。

为了避免NCO频率泄漏,输入DAC的数字代码必须在零代码附近平衡(正代码的数量必须等于负代码的数量)。也就是说,必须从输入数字代码中去除输入DC偏移。否则,在频率合成中,当使用NCO对高于或低于0Hz的信号进行移位时,泄漏可能变得明显。NCO频率被视为NCO FTW的一个小杂散。

插值滤波器

主数字路径包含五个半带内插滤波器,加上在2×NRZ模式中使用的最后一个半带外插滤波器。滤波器级联,如图109所示。

第一对滤波器是2×(HB2)或3×(HB3)滤波器。这些滤波器中的每一个都有两个带宽选项,80%或90%。80%的滤波器比90%的滤波器功率低。滤波器默认为低功率80%带宽。要将滤波器带宽选择为90%,请将DATAPATH_CFG寄存器中的FILT_BW位编程为1(寄存器0x111,位4=0b1)。

第一对滤波器之后是一系列2×半带滤波器,每个滤波器的可用带宽是前一对滤波器的一半。HB4具有45%,HB5具有22.5%,HB6具有11.25%的fDATA带宽。

最终的半带滤波器FIR85用于2×NRZ模式。它以2×fDAC速率计时,可用带宽为fDAC速率的45%。FIR85滤波器是一个复杂的滤波器,因此带宽以0Hz为中心。FIR85滤波器与复数插值模式结合使用,以提高DAC更新率,使得镜像频率远离所需信号频率。

表34显示了如何选择每个可用的插值模式、它们的可用带宽以及它们的最大数据速率。将可用信号带宽计算为插值器滤波器带宽BW乘以fDAC/插值因子,如下所示:

BWSIGNAL=BWFILT×(fDAC/插值因子)

1. 所有插值器模式的数据速率(fDATA)是一个复数数据速率,意味着I数据和Q数据中的每一个都以该速率运行。可用信号带宽是数据速率乘以初始2×或3×插值滤波器的带宽,可以设置为BW=80%或BW=90%。该带宽以0 Hz为中心。

2 1×和2×插值的最大速度受JESD204B接口的限制,在1×或2×插值模式下为5000 MHz(实数)或2500 MHz(复数)。

3 2×NRZ滤波器FIR85可与任何插值器组合使用。

4 FIR85滤波器的带宽以0 Hz为中心。

滤波器性能

插值滤波器在现有数据之间进行插值,使得它们对输入数据的影响最小化,同时抑制插值镜像信号的产生。图110中显示了每个滤波器的数据路径。

可用带宽(如表34所示)定义为滤波器通带纹波小于±0.001 dB和图像抑制大于85 dB的频带。图110显示了每个滤波器的相对带宽。所有滤波器的最大通带幅度相同;为了增进理解,他们在插图中有所不同。

一些插值滤波器被指定为0.4×fDATA(带通带)。以增加通带波纹和降低插值镜像抑制为代价时,可以使用稍微超过该速率。图111显示了超过0.4×fDATA的插值滤波器的性能。纹波的增加比图像抑制的减少慢得多。这意味着,如果应用场景能够容忍插值滤波器的镜像抑制性能下降,则可以使用更多的带宽。大多数滤波器被指定为0.45×fDATA(带通带)。图112至图119显示了AD9164上每个插值器滤波器的滤波器响应。

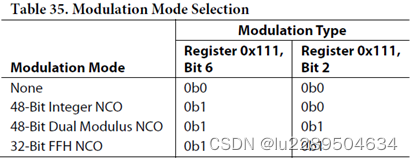

数字调制

AD9164具有数字调制功能,可将基带正交信号调制到所需的DAC输出频率。AD9164配备了多种NCO模式。默认NCO是一个48位的整数NCO。双模NCO的A/B比允许以非常精细的精度合成输出频率。选择NCO模式,如表35所示。

当启用主48位NCO时,通过将非零字写入其FTW寄存器来启用FFH NCO(请参阅快速跳频(FFH)部分)。

48位双模NCO

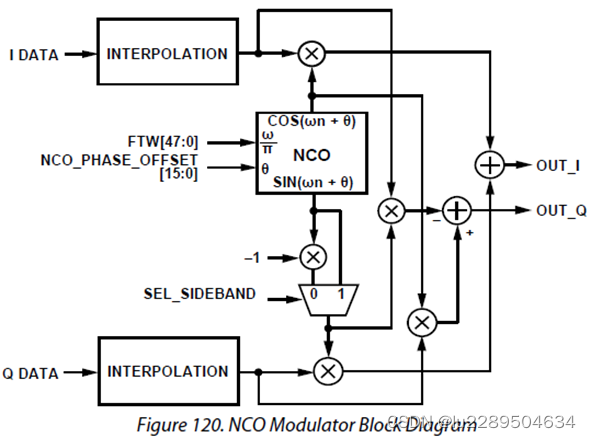

调制模式使用NCO、移相器和复数调制器通过可编程载波信号对信号进行调制,如图120所示。这种配置允许输出信号在输出频带范围内,具备非常精细的频率分辨率。

NCO产生正交载波用于将输入信号转换为新的中心频率。正交载波是一对同频的正弦波形,相位偏移90°。正交载波的频率是通过FTW设置的。正交载波与I和Q数据混频,求和后送至I和Q的数据路径中,如图120所示。

整数NCO模式

通过使用以下公式创建频率调谐字(FTW),可以将主48位NCO用作整数NCO:−fDAC/2≤fCARRIER<+fDAC/2,FTW=(fCARRIR/fDAC)×248

其中FTW是48位的二进制补码数。

在2×NRZ模式下(寄存器0x111启用FIR85,位0=1),频率调谐字计算为:0≤fCARRIER<fDAC,FTW=(fCARRIR/fDAC)×248

其中FTW是48位二进制数。

当翻转FIR85使能位并且不改变FTW以考虑数字格式的变化时,这种计算方法会导致第二奈奎斯特区域中的fCARRIER值看起来移动到fDAC−fCARRIR。

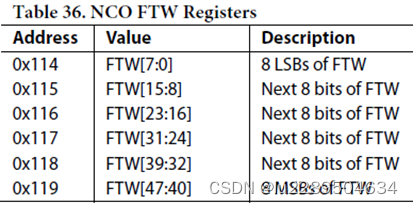

当FIR85使能位设置为寄存器0x111,在fCARRIR/fDAC=0.5之前,位0=0b1时,预期效果是,NCO从0 Hz到fDAC−fDAC/248的扫描看起来是无缝的。从检查中可以看出,从0到小于fDAC/2时, FTW在任何一种情况下无差别,但从fDAC/2到fDAC−fDAC/248时,它们意味着不同的fCARRIER值。在构造FTW值和使用2×NRZ模式时,必须考虑这种影响。频率调谐字的设置如表36所示。

与其他寄存器不同,FTW寄存器在写入时不会立即更新。相反,FTW寄存器在FTW_LOAD_REQ的上升沿更新(寄存器0x113,位0)。更新请求后,FTW_LOAD_ACK(寄存器0x113,位1)必须为高电平,以确认FTW已更新。

SEL_SIDEBAND比特(寄存器0x111,比特1=0b1)可以设置为使用下边带调制结果,这相当于翻转FTW的符号。

模数NCO模式(直接数字合成(DDS))

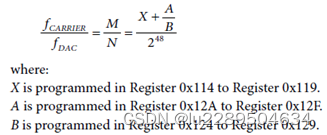

主48位NCO也可以在双模模式中使用,以创建超过48位精度的分数频率。通过将DATAPATH_CFG寄存器中的modulus_EN位编程为1(寄存器0x111,位2=0b1)来启用模数模式。

可编程模数直接数字合成(DDS)的频率比与典型的基于累加器的DDS的频率比非常相似。唯一的区别是,对于可编程模数,N不需要是2的幂,而是可以是任意整数。在实践中,硬件约束限制了N的值范围。因此,模数将NCO的使用扩展到需要精确有理频率合成的应用。可编程模量技术的基本功能是改变累加器模量。

AD9164中可编程模数函数的实现使得分数M/N可根据等式1表示。注意,方程的形式意味着复合频率调谐字,其中X表示整数部分,A/B表示小数部分。

可编程模数示例

考虑fDAC=2500MHz并且fCARRIER的期望值为250MHz的情况。这种情况合成的输出频率不是采样率的二次幂,即fCARRIER=(1/10)fDAC,这对于典型的基于累加器的DDS是不可能的。根据频率比fCARRIR/fDAC可确定M和N,这是通过将分数(250000000/25000000)减少到其最低项来确定的,即,M/N=250000000/2500000=1/10。因此,M=1和N=10。

经计算,X=28147497671065,A=3,B=5。将这些值编程到X、A和B的寄存器中(X在寄存器0x114到寄存器0x119中编程,B在寄存器0x124到寄存器0x129中编程,A在寄存器0x12A到寄存器0x12F中编程)会导致NCO在给定2500 MHz采样时钟的情况下产生精确为250 MHz的输出频率。有关更多详细信息,请参阅Analog Devices,股份有限公司网站上的AN-953应用说明。

重置NCO

在确定NCO的开始时间和相位时,重置NCO可能很有用。NCO可以通过几种不同的方法复位,包括SPI写入、使用TX_ENABLE引脚或通过SYSREF±信号。由于设备之间的内部时序变化,这些方法实现了±6个DAC时钟周期的精度。

编程寄存器0x800,位[7:6]至0b01,通过对SPI端口的写入将NCO设置为相位不连续切换模式。然后,每当频率调谐字更新时,NCO相位累加器复位,NCO开始在新FTW计数。

快速跳频(FFH)

为了支持FFH,AD9164在NCO块中具有几个功能。NCO功能有两种实现方式。主48位NCO是一种通用NCO,支持一些FFH模式,而FFH NCO是专门为支持几种不同的FFH模式而设计的。

主NCO跳频

在主48位NCO中,更新频率调谐字的模式可以通过写入FTW_LOAD_REQ位(寄存器0x113,位0)改变为自动更新模式。在自动更新模式中,一旦写入选定的FTW字,FTW就会被更新。要设置自动FTW更新模式,请将适当的字写入FTW_REQ_mode位(寄存器0x113,位[6:4]),选择特定的FTW字用于自动更新。例如,如果需要相对粗略的频率步长,则将单个字写入FTW的MSB字节就足够了,因此FTW_REQ_MODE位可以编程为110(寄存器0x113,位[6:4]=0b110)。然后,每次写入最高有效字节FTW5时,NCO FTW都会自动更新。

FTW_REQ_MODE位可以被配置为使用任何FTW字作为自动更新触发字。这种配置在选择FTW寄存器的编程顺序时提供了便利。SPI端口写入功能的速度(最低为100 MHz,见表4)能够保证自动更新的速度。因此,在自动更新模式下,通过一个寄存器写入,NCO FTW可以在低至240ns的时间内更新。

FFH NCO

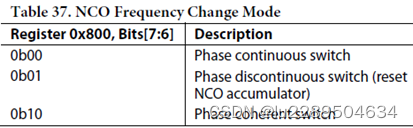

FFH NCO通过为48位主NCO配置31个32位NCO实现。这些FTW可以被预加载到跳频寄存器组中。32个FTW中的任何一个都可以通过一个寄存器写入HOPF_CTRL寄存器中的HOPF_SEL位(寄存器0x800,位[4:0])来选择。NCO转换到新频率的方式由选择的跳频模式来确定。FFH NCO支持几种快速跳频模式:相位连续跳频、相位不连续跳频和相位相干跳频。跳频模式如表37所示。

在相位连续模式中,NCO的频率调谐字被更新,并且相位累加器继续累加到新的频率。在相位不连续模式下,NCO的FTW被更新,相位累加器被重置,从而瞬时跳到新频率。在相位相干模式中,启用附加的31个相位累加器的组,每个累加器遮蔽跳频寄存器组中的每个FTW。

在启用相位相干切换模式(寄存器0x800,Bits[7:6]=0b10)时,所有32个NCO相位累加器同时开始计数,并且无论当前在数字数据路径中使用哪个单独的NCO输出,都继续计数。通过这种方式,可以选择单个NCO的频率,并且该频率总是与时刻0相位相干。因此,建议对所有FTW进行预加载,然后选择相位相干开关模式来同时启动它们。

为了节省功率,只有当FTW编程到其寄存器中时,才启用31个附加NCO和相位累加器中的每一个。要关闭特定NCO和相位累加器的电源,请将给定NCO的FTW寄存器写0。所有NCO FTW的默认值均为0x0。主48位NCO,即FFH NCO中的FTW0,由DATAPATH_CFG寄存器中的NCO_EN位启用(寄存器0x111,位6=0b1)。

为了确保某个32位NCO在通电后再断电,不会有残余功耗或可能的残余杂散,建议将额外NCO断电的方法是首先将FTW编程为0x0001,然后将其编程为0x0000。这确保了相位累加器在接收全零字之前被清除残余值,进而实现输出断电而不是累加器断电。寄存器0x111中的NCO_EN位6使能累加器断电。

仅NCO模式

AD9164能够在仅启用NCO的模式下运行。在此模式下,NCO引擎生成单音正弦波,并将其发送至DAC输出。数字调制部分中讨论的所有功能都可以在仅NCO模式下使用。在这种模式下,没有必要打开JESD204B链接。该模式是一个有用的选项,可以在不需要数字数据源的情况下启动发射机无线电信号链,因为设备在内部生成NCO数据。这种模式也可以用于只需要正弦波的应用中,例如本地振荡器应用中。

要启用仅NCO模式,请对寄存器0x150中的DC_TEST_EN位进行编程,位1=0b1。然后,将dc值编程到寄存器0x14E(MSB)和寄存器0x14F(LSB)中的二进制补码dc测试数据字中。默认值为0x0000(零振幅),0x7FFF(满量程振幅)。最后一步是通过在寄存器0x110,Bits[3:0]中选择INTERP_mode=0b0000,将插值编程为1×旁路模式。这是必要的,因为直流测试值仅在旁路路径中可用,而在复杂数据路径中不可访问。

当DC_TEST_EN=1时,数字数据路径的数据源是DC测试数据字。这意味着可以启动JESD204B链路,并且可以通过该链路将数据成功地传输到设备,但是当DC_TEST_EN=1时,数据不呈现给DAC。只有当DC_TEST_EN=0时,才能实现到SERDES数据源的连接。DC_TEST_EN位可以动态设置,但由于禁用模式和切换到SERDES数据路径通常需要也设置通道和/或插值模式,因此动态设置或重置DC_TEST_EN位通常是不可行的。

反向SINC

AD9164提供了一个数字反正弦滤波器来补偿DAC随频率的衰减。滤波器通过设置INVSINC_EN位(寄存器0x111,位7)启用,默认情况下禁用。

反向sinc(sinc−1)滤波器是一个七抽头FIR滤波器。图121显示了sin(x)/x滚降的频率响应、反向sinc滤波器和复合响应。复合响应的通带纹波小于±0.05dB,频率高达0.4×fDACCLK。当启用2×NRZ模式时,反向sinc滤波器工作至0.4×f2×DACCLK。为了在高频段提供必要的峰值,所示的反向sinc滤波器具有大约3.8dB的固有插入损耗。

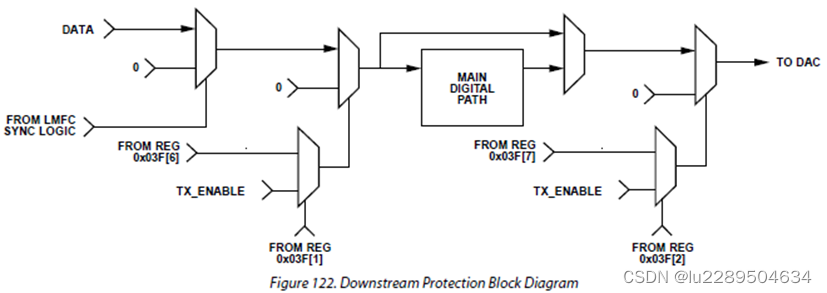

下游模块保护

AD9164具有几个功能,旨在保护系统的功率放大器(PA)以及其他下游块。它们由来自LMFC同步逻辑的控制信号和传输使能功能组成。每种情况下的保护机制都是对传递到DAC解码器的数据进行消隐。不同之处在于数据路径中的位置和功能的细微变化。

JESD204B串行链路具有多个标志和质量度量,以指示串行链路已启动并运行无错误。如果这些测量中的任何一个标记了问题,则来自LMFC同步逻辑的信号被发送到多路复用器,该多路复用器停止数据流向DAC解码器,并用0替换它。

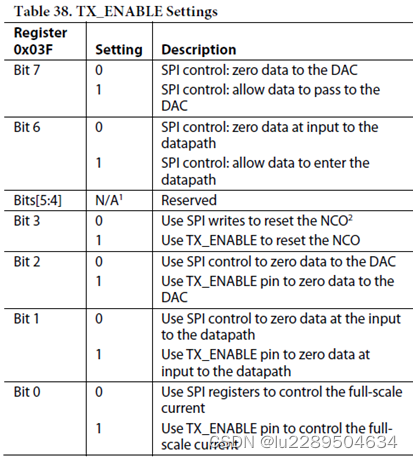

有几个传输启用功能,包括TX_enable寄存器,该寄存器可用于抑制数据路径中几个点的数据,或配置TX_enable引脚以进行类似操作。

传输启用

传输启用功能可以配置为SPI控制功能或引脚控制功能。它可以用于多种不同的目的。SPI控制的功能由于依赖于微控制器对其进行编程而具有较不精确的定时;因此,它通常在加电或配置设备时用作预防措施。

SPI控制的TX_ENABLE函数可用于将数字数据路径的输入归零或将数字数据通路的输出归零,如图122所示。如果数字数据路径的输入为零,则所选择的任何滤波都会对0信号进行滤波,从而导致数字数据路径中的能量逐渐下降。如果数字数据路径被旁路,如在1÷模式中,DAC输入端的数据立即降至零。

当启用或禁用DAC输出时,TX_ENABLE引脚可用于更准确的定时。TX_ENABLE引脚的效果可以由用于SPI控制功能的相同TX_ENABLE寄存器(寄存器0x03F)来配置,并且可以使其具有与SPI控制功能相同的效果,即使数字数据路径的输入为零或者使数字数据路径的输出为零。此外,TX_ENABLE引脚还可以被配置为斜坡下降(或上升)DAC的满刻度电流。斜坡下降将DAC的输出功率从满标度降低到最小输出电流约20dB。

TX_ENABLE引脚也可以被编程为重置NCO相位累加器。有关TX_ENABLE功能可用设置的说明,请参见表38。

N/A表示不适用。

如果需要重置NCO,请使用SPI写入来重置NCO。寄存器0x800,位[7:6]确定NCO是否复位。详见表37。

数据路径伪随机码(PRBS)

数据路径PRBS可以验证AD9164数据路径接收并正确解码数据。数据路径PRBS验证发射机和接收机的JESD204B参数匹配,接收机的通道被适当映射,通道被适当反转,并且,如果需要,启动例程被正确执行。

要运行数据路径PRBS测试,请完成以下步骤:

1.使用启动顺序将设备设置为所需的操作模式。

2.发送PRBS7或PRBS15数据。

3.写入寄存器0x14B,对于PRBS7,位2=0或对于PRBS15,位2=1。

4.写入寄存器0x14B,Bits[1:0]=0b11以启用和重置PRBS测试。

5.写入寄存器0x14B,Bits[1:0]=0b01以启用PRBS测试并释放重置。

6.等待500毫秒。

7.如Datapath PRBS IRQ部分所述,通过检查I和Q路径PRBS的IRQ来检查PRBS的状态。

8.读取寄存器0x14B,位[7:6]。如果I通道有任何错误,则位6为0。如果Q信道有任何错误,则位7为0。

9.读取寄存器0x14C以读取I通道的错误计数。

10.读取寄存器0x14D以读取Q通道的错误计数。PRBS一次处理32个比特,并将32个新比特与之前的32比特集进行比较。它在每组32位中只检测并报告1个错误;因此,错误计数在一定程度上取决于何时看到错误。

数据路径伪随机码中断请求

I和Q路径的PRBS故障信号可用作IRQ事件。使用寄存器0x020,Bits[1:0]启用故障信号,然后使用寄存器0x024,Bits[1:0]读回状态并重置IRQ信号。有关更多信息,请参阅中断请求操作部分。

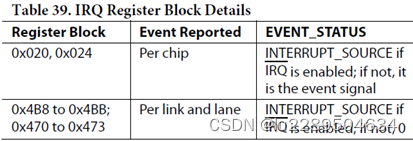

中断请求

AD9164在球G1(8毫米×8毫米CSP_BGA)或球G4(11毫米×11毫米CSP_BGA)上提供中断请求输出信号(IRQ),可用于通知外部主机处理器重大设备事件。在发生中断时,查询设备以确定发生的具体事件。IRQ引脚是一个漏极开路、低电平有效输出。将IRQ引脚拉高。该引脚可以连接到具有漏极开路输出的其他设备的中断引脚,以将这些引脚连接在一起。

图123显示了IRQ块简化原理框图。如果IRQ_EN为低,则INTERRUPT_SOURCE信号被设置为0。如果IRQ_EN为高,则EVENT的任何上升沿导致INTERRUPT_SOURCE信号被设置为高。如果任何INTERRUPT_SOURCE信号为高电平,则IRQ引脚被拉低。INTERRUPT_SOURCE可以通过IRQ_reset信号或DEVICE_reset信号重置为0。

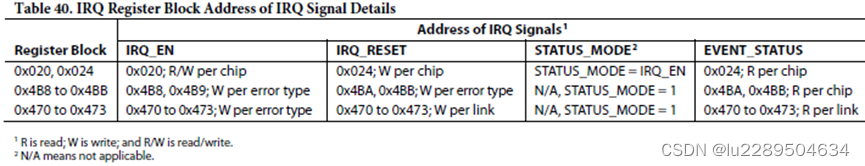

根据STATUS_MODE信号,EVENT_STATUS位读回一个事件信号或INTERRUPT_SOURCE信号。AD9164具有多个中断寄存器块(IRQ),可监视多达75个事件(取决于设备配置)。某些细节因IRQ寄存器块而异,如表39所示。表40显示了图123中IRQ_EN、IRQ_RESET和STATUS_MODE信号的源寄存器,以及读取EVENT_STATUS的地址。

中断服务程序

中断请求管理通过选择需要主机干预或监视的一组事件标志开始。启用需要主机操作的事件,以便在事件发生时通知主机。对于IRQ激活时需要主机干预的事件,运行以下例程以清除中断请求:

1.读取正在监视的事件标志位的状态。

2.通过将0写入IRQ_EN来禁用中断。

3.读取事件源。

4.执行任何可能需要的行动,以澄清事件的原因。在许多情况下,可能不需要采取具体行动。

5.验证事件源是否按预期运行。

6.通过向IRQ_RESET写入1来清除中断。

7.通过向IRQ_EN写入1来启用中断。

应用场景信息

硬件注意事项

电源

所有AD9164供电必须尽可能保持无噪声,以实现最佳操作。电源噪声具有影响性能的频率分量,并且以伏特rms术语指定。建议在电源输出端设计LC滤波器来抑制噪声,并且必须尽可能靠近AD9164。

VDD12_CLK电源是设备上对噪声最敏感的电源,其次是VDD25_DAC和VNEG_N1P2电源,它们是DAC输出轨。强烈建议VDD12_CLK本身配备超低噪声稳压器,如ADM7154或ADP1761,以实现最佳的相位噪声性能。噪声较大的稳压器将恶化DAC输出的相位噪声。

VDD12A电源可以通过单独的滤波器网络连接到数字DVDD电源。所有SERDES(SERializer(串行器)/DESerializer(解串器))1.2V电源都可以连接到一个具有独立滤波器网络的稳压器。IOVDD电源可以通过单独的滤波器网络连接到VDD25_ DAC电源,或者可以由1.8V至3.3V电源的系统控制器(例如,微控制器)供电。必须满足电源顺序要求;因此,当用VDD25_DAC连接到IOVDD电源时,必须使用开关或其他解决方案。

注意表3中给出的最大功耗数字,以确保电源设计能够承受极端温度和IC工艺变化。所消耗的电流量取决于所选择的用例,并为几个用例提供了规范,以说明单个块的示例和贡献,并帮助计算每个电源所需的最大电流。

电源设计的另一个考虑因素是峰值电流处理能力。与处于空闲模式或合成直流信号时相比,当合成具有显著幅度变化的信号(如调制信号)时,AD9164在主数字电源中汲取更多电流。因此,电源必须能够快速提供电流以适应突发信号,例如GSM、TDMA或具有开/关时域响应的其他信号。由于电流变化量取决于所使用的信号,因此最好先进行实验室测试以确定范围。典型的差异可以是几百毫安。

上电顺序

AD9164需要电源顺序,以避免损坏DAC。AD9164的板设计必须包括电源定序器芯片,如ADM1184,以确保域按正确顺序通电。ADM1184在通电时监测电源域的级别。它向下一组电源域发送启用信号。当所有电源域通电时,将向系统控制器发送电源良好信号,以指示所有电源已通电。

IOVDD、VDD12A、VDD12_CLK和DVDD域必须首先通电。然后,VNEG_N1P2、VDD_1P2、PLL_CLK_VDD12、DVDD_1P2和SYNC_VDD_3P3可以通电。VDD25_DAC域必须最后通电。没有断电顺序的要求。

电源和接地平面

建议使用实心接地平面,以避免接地回路,并为需要控制阻抗的高速传输线提供实心、不间断的接地参考。建议将电源平面堆叠在接地层之间以进行高频滤波。这样做除了增加去耦电容之外,还增加了电源域之间的额外滤波和隔离。

除非受控阻抗线的整个长度仅穿过单个分段平面,否则不要使用分段电源平面作为受控阻抗的参考。JESD204B串行接口输入(SERDIN0±至SERDIN7±)一节介绍了高速输电线路拓扑结构的这些和附加指南。

对于某些需要最高性能和更高输出频率的应用,PCB材料的选择会显著影响结果。例如,可以使用诸如聚酰亚胺的材料或罗杰斯公司的材料提高对高温的耐受性并提高性能。Rogers 4350材料用于一些评估板设计中的顶部三层:顶部信号层和其下方的接地层之间,接地层和内部信号层之间,以及该信号层和另一接地层之间。

JESD204B串行接口输入(SERDIN0±至SERDIN7±)

在考虑JESD204B串行接口传输线的布局时,要保持最佳链路性能,需要考虑许多因素。这些因素包括插入损耗、回波损耗、信号偏斜和差分线的拓扑结构。

插损

JESD204B规范限制了传输信道中允许的插入损耗量(见图95)。AD9164均衡电路允许信道中的损耗明显大于JESD204B规范所要求的损耗。仍然重要的是,PCB的设计者应遵守以下准则,最大限度地减少插入损耗:

- 通过将AD9164放置在尽可能靠近传输逻辑设备的位置,并在设备之间尽可能直连传输线,使差分线保持较短。

- 使用实心接地平面作为参考,在单个平面上布置差分对。建议在与AD9164相同的层上布线SERDES通道,以避免在SERDES通道中使用过孔。

- 如果可能的话,使用低介电常数(<4)的PCB材料以最大限度地减少损耗。

在选择带状线和微带技术时,请记住以下注意事项:带状线损耗较小(见图96和图97),发射的EMI较少,但需要使用过孔,这可能会增加控制阻抗的复杂性;而微带更容易实现(如果元件放置和密度允许在顶层上布线),并且便于控制阻抗。

如果使用PCB顶层有问题,或者需要带状线的优势,请遵循以下建议:

- 尽量减少过孔的数量。

- 如果可能,使用盲过孔来消除过孔短截线效应,并使用微孔来最小化过孔电感。

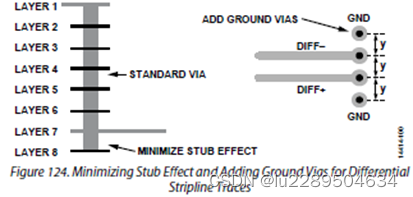

- 如果使用标准过孔,请使用最大过孔长度来最小化短截线大小。例如,在8层板上,使用第7层作为带状线对(见图124)。

- 对于每个过孔对,在其附近放置一对接地过孔,以最大限度地减少阻抗不连续性(见图124)。

回波损耗

JESD204B规范限制了转换器设备和逻辑设备中允许的回波损耗量,但没有指定信道的回波损耗。然而,必须尽一切努力在传输逻辑器件和AD9164之间的传输线上保持连续阻抗。尽量减少过孔的使用,或将其全部消除,可以减少传输线上阻抗失配的主要来源之一(请参阅插入损耗部分)。在差分线下方(对于微带)或上方和下方(对于带状线)保持一个实心参考地,以确保传输线阻抗的连续性。如果使用带状线技术,请遵循“插入损耗”部分中列出的指南,以最大限度地减少阻抗失配和短截线效应。阻抗失配的另一个主要来源是传输线的任一端,必须注意使终端的阻抗与传输线的阻抗匹配。AD9164通过线路接收端的校准端接方案在内部处理这一问题。有关该电路和校准程序的详细信息,请参阅接口通电和输入端接部分。

信号偏斜(Signal Skew):多信号之间的延时差异

信号偏斜的来源有很多,但在布置PCB时要考虑的两个来源是单个JESD204B链路内的互连偏斜和多个JESD204B链路之间的偏斜。在每种情况下,保持信道长度匹配在12.5mm以内对于以高达12.5Gbps的速度操作JESD204B链路是足够的。这种通道长度匹配量相当于AD9164评估板上约85%的UI。管理单个链路内的互连偏斜是相当简单的。跨多个设备管理多个链接更为复杂。但是,请遵循12.5 mm的长度匹配准则。由于JESD204B接收器中有六个PCLK周期缓冲区,AD9164可以处理比85%UI更多的偏斜,但仍然建议尽可能接近地匹配信道长度。

拓扑

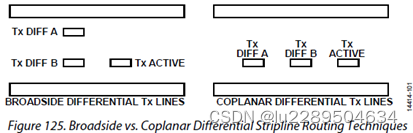

构造差分SERDINx±对,在任何一种情况下,重要的是保持这些传输线与潜在的噪声源分离,例如高速数字信号和噪声源。如果使用带状线差分迹线,请使用共面方法布线,使两根线位于同一层上。尽管这种方法没有比宽边布线方法(在相邻层上布线的迹线)提供更多的抗噪声性,但它更容易布线和制造,从而保持阻抗连续性。宽边与共面的图解如图125所示。

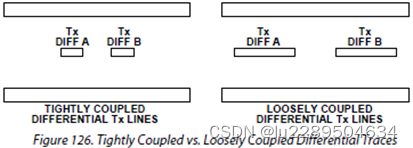

当考虑线宽与铜重量和厚度的关系时,必须考虑界面的速度。在多千兆比特的速度下,导电材料的趋肤效应将电流限制在表面。通过使走线宽度变宽来最大化导体的表面积,以减少损耗。此外,耦合度小的差分线需要更宽的走线宽度。当差分线必须分开以容纳组件、过孔、连接器或其他布线障碍时,这种耦合有助于减少串扰并最大限度地减少阻抗失配。紧密耦合与松散耦合的差分线如图126所示。

交流耦合电容

AD9164要求将JESD204B输入信号耦合到源。这些电容器必须是100nF,并且放置得尽可能靠近传输逻辑器件。为了最大限度地减少焊盘处的阻抗失配,请选择PCB上的焊盘尺寸尽可能与线宽匹配的电容封装尺寸。

\SYNCOUT±, SYSREF±, and CLK± Signals

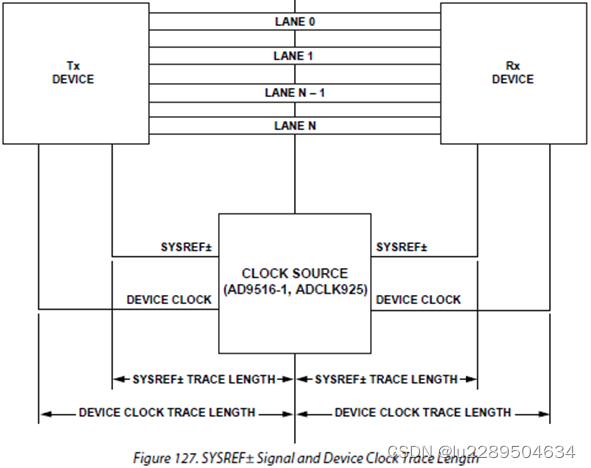

AD9164上的\SYNCOUT±和SYSREF±信号是低速LVDS差分信号。在布线这些信号时,使用100Ω差分阻抗和50Ω接地的受控阻抗迹线。与SERDIN0±至SERDIN7±数据对一样,重要的是要将这些信号与潜在的噪声源(如高速数字信号和噪声源)分离。将\SYNCOUT±信号与其他噪声信号分开,因为\SYNCOUT±上的噪声可能被解释为对/K/字符的请求。对于从时钟源到JESD204B链路任一端的每个设备的CLK±和SYSREF±信号,保持相近的线长度是很重要的(见图127)。如果使用能够严格控制CLK±和SYSREF±相位的时钟芯片,则大大降低了迹线长度匹配要求。

模拟接口注意事项

模拟操作模式

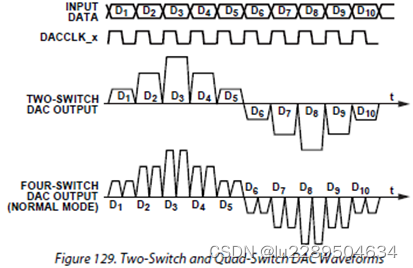

AD9164使用如图128所示的四开关架构体系结构。在半个时钟周期内,只有一对开关被启用,因此要求每对开关在交替的时钟边沿上被计时。四开关架构的一个关键优点是它屏蔽了传统的两开关DAC架构中出现的与代码相关的毛刺。在两开关架构中,在D1和D2处于不同状态时切换,将发生故障。然而,如果D1和D2恰好处于相同状态,则开关正常转换并且不发生毛刺。这种与代码相关的毛刺会导致DAC中失真量的增加。在四元开关架构中(无论代码是什么),总是有两个开关在每半个时钟周期转换,从而消除了与代码相关的故障,但在这个过程中,会在2×fDAC处产生恒定的故障。因此,在DAC输出频谱中,2×fDAC处将出现明显的时钟杂散。

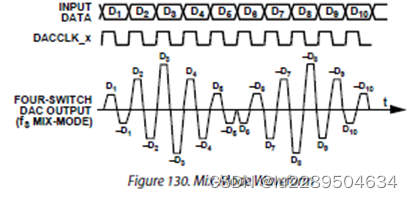

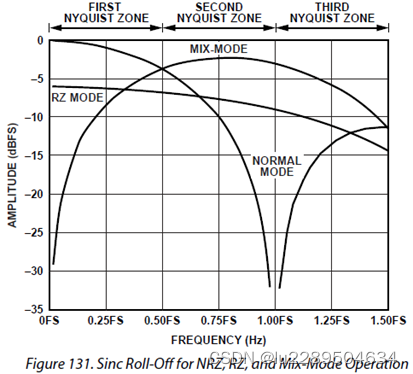

由于四元开关架构能够在每半个时钟周期进行更新,因此,如果在DAC时钟的上升沿和下降沿将新的数据样本锁存到DAC核心中,则可以以2倍DAC时钟速率操作DAC内核。这一概念是在混合模式或归零(RZ)模式下操作AD9164的基础。在每种情况下,DAC内核在每个时钟边沿上都有新的数据样本:在RZ模式下,上升沿时钟采样数据,下降沿时钟采样零,而在混合模式下;下降沿采样只是上升沿采样值的补码。当使用混合模式并以DAC采样率工作时,输出信号被有效斩波。这种斩波降低了基本信号的功率,同时增加了以DAC采样率为中心的镜像信号的功率,进而改善了镜像信号的动态范围。

这种改变模式的能力为用户提供了根据所选择的操作模式将载波放置在前三个奈奎斯特区域中的任何位置的灵活性。在基带和混合模式之间的切换重塑了DAC输出处固有的sinc滚降。在基带模式中,sinc null出现在fDACCLK,因为在上升时钟边缘锁存的相同样本也在下降时钟边缘再次锁存,从而导致传统DAC的相同普遍存在的sinc响应。在混合模式中,上升沿的补码样本被锁存在下降沿,因此将sinc null推至2×fDACCLK。图131显示了包括sinc滚降的三种模式的理想频率响应。

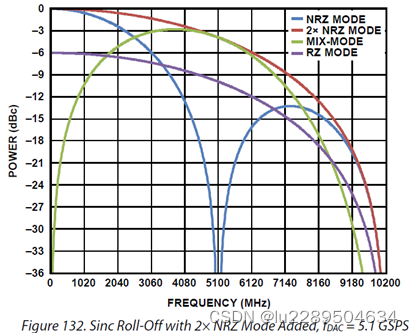

四元开关可以通过SPI(寄存器0x152,位[1:0])配置为在NRZ模式(0b00)、RZ模式(0 b10)或混合模式(0 b01)下操作。由于采用了FIR85滤波器,AD9164具有额外的频率响应特性。该滤波器在DAC时钟的上升沿和下降沿对数据进行采样,实质上使输入时钟频率加倍。因此,图131中的NRZ(正常)模式滚降扩展到图131的2×fDAC,并且由于在2×DAC时钟处的零阶保持而跟随混合模式滚降(见图132)。

时钟输入

AD9164包含一个低抖动、差分时钟接收器,能够直接连接到差分或单端时钟源。由于输入是自偏置的,标称阻抗为90Ω,因此建议时钟源交流耦合到CLK±输入引脚。标称差分输入为1 V p-p,但时钟接收器可以在250 mV p-p至2.0 V p-p的范围内工作。使用更高的时钟输入电平可以实现更好的相位噪声性能。

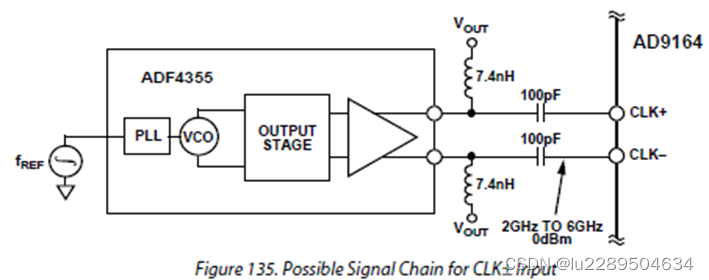

时钟源的质量及其与AD9164时钟输入的接口直接影响交流性能。选择时钟源的相位噪声和杂散特性,以满足目标应用要求。时钟源上给定频率偏移处的相位噪声和杂散被直接转换为输出信号。可以看出,当DAC时钟路径的贡献可以忽略不计时,重构输出正弦波的相位噪声特性与时钟源的关系为20×lg(fOUT/fCLK)。图135显示了基于ADF4355低相位噪声/抖动PLL的时钟源。ADF4355可以提供从54MHz到6.8GHz的输出频率。

时钟控制寄存器存在于地址0x082到地址0x084处。CLK_DUTY(寄存器0x082)可用于启用占空比校正(位7)、启用占空因数偏移控制(位6)和设置占空因数偏置(位[4:0])。占空比偏移字是带符号的幅度字,其中比特4是符号比特(1是负的),比特[3:0]是幅度。占空比在大约±3%的范围内进行调整。此寄存器的推荐设置列在“启动顺序”部分。

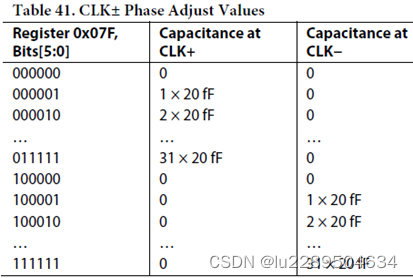

时钟输入有一个寄存器,用于调整CLK+和CLK-输入的相位。此寄存器位于地址0x07F。根据表41,寄存器具有一个带符号的幅值(1为负),该值将每阶20 fF的电容添加到CLK+或CLK-输入。CLK_PHASE_TUNE寄存器可用于调整时钟输入相位以获得更好的DAC镜像抑制。

进行这些调整所带来的性能改进取决于时钟输入平衡-不平衡巴伦的平衡精度,并且因单元而异。因此,如果需要高水平的镜像抑制,则可能需要每单位校准。执行这种校准可以产生显著的改进,由于不平衡,镜像的额外抑制高达20dB。图134显示了调整时钟相位、占空比(在这种情况下为默认值)和交叉控制的结果。性能的提高,特别是在更高的频率下,可以高达20dB。

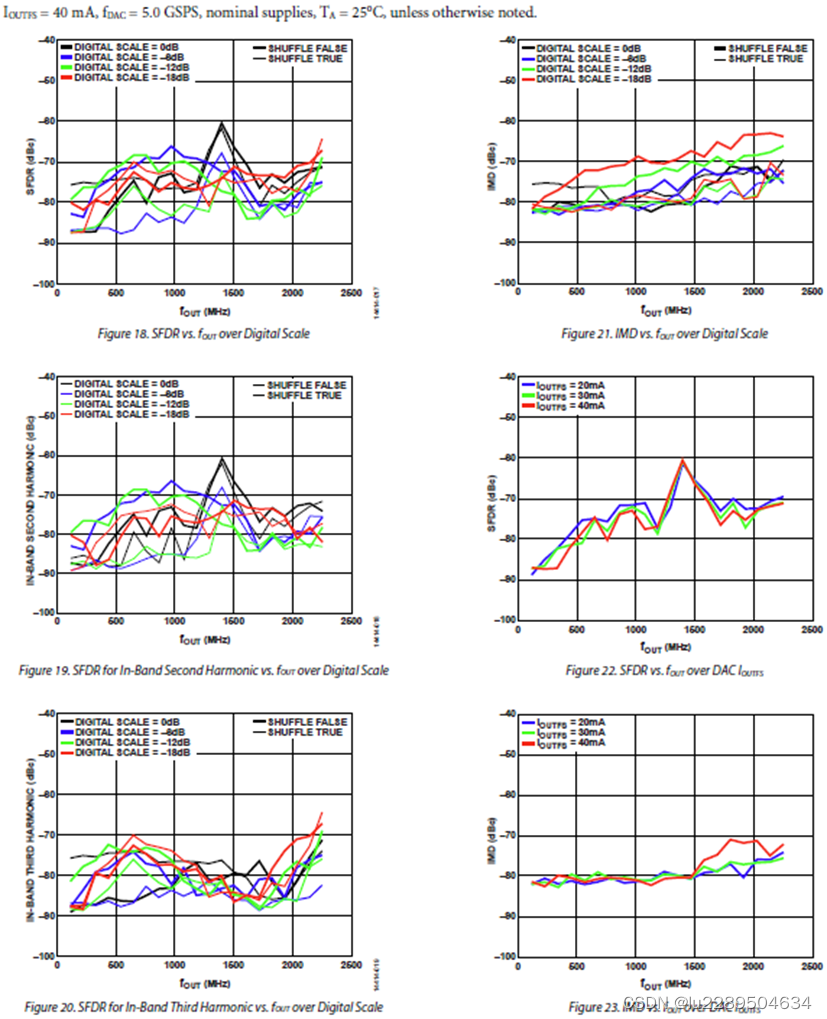

乱序模式(SHUFFLE MODE)

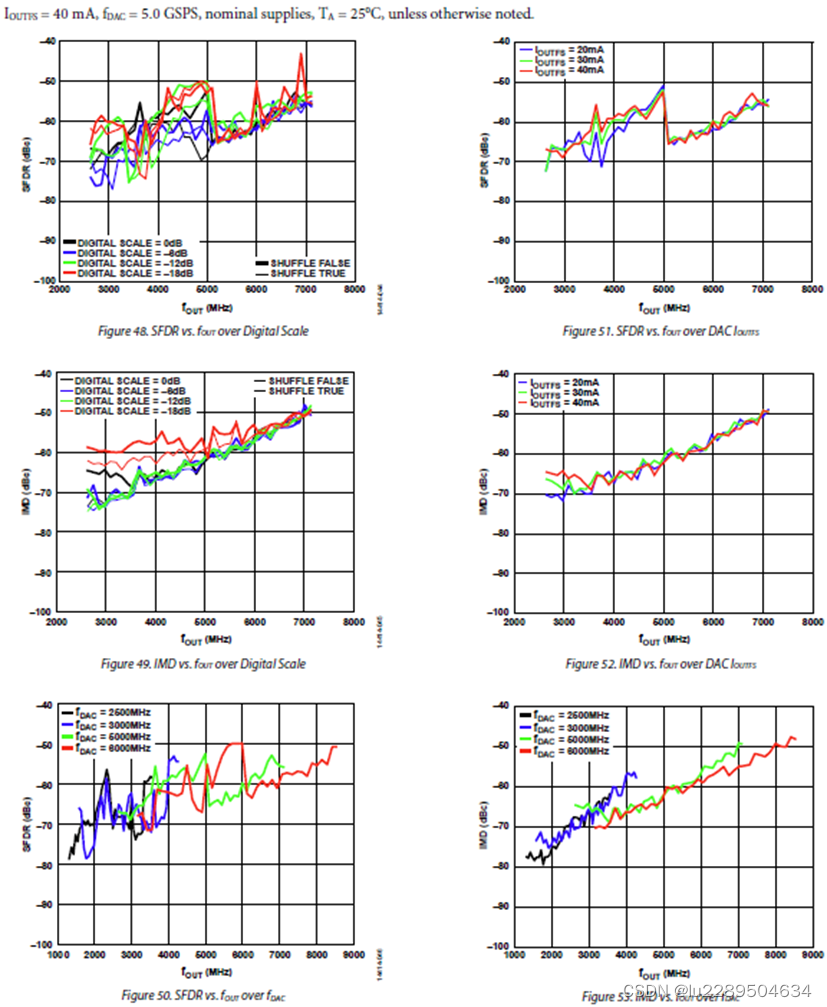

AD9164的杂散性能可以通过称为乱序模式的功能来改善。乱序模式使用专有技术将杂散信号的能量作为随机噪声分布在DAC输出上。通过编程寄存器0x151,位2=0b1,可启用乱序模式。因为乱序是用MSB实现的,所以当DAC用少量数字回退操作时,乱序更有效。

乱序模式引起的噪声上升量与受影响的杂散信号中的功率直接相关。因为AD9164在没有乱序激活的情况下具有良好的杂散性能,所以乱序模式对噪声频谱密度的优化通常约为1dB至3dB。乱序模式降低了与时钟和折返杂散相关的杂散性能,但不影响DAC输出的实谐波。乱序模式的效果示例见典型性能特征部分(见图48、图49、图63、图64和图65)。

DLL

CLK±输入进入高频DLL,以确保DAC采样时钟与输入时钟的稳健锁定。DLL是作为建议启动顺序的一部分进行配置和启用的。DLL控制寄存器位于寄存器0x090到寄存器0x09B处。DLL设置在产品表征过程中确定,并在推荐的启动顺序中给出(请参阅启动顺序部分)。通常不需要更改这些值,产品特性数据在除推荐设置之外的任何设置上都无效。

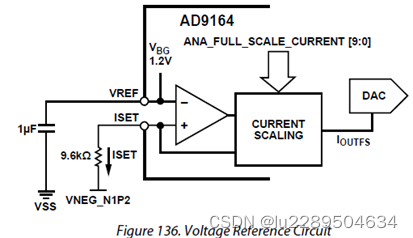

电压参考

AD9164输出电流由数字控制位和ISET参考电流的组合设置,如图136所示。将外部9.6kΩ电阻器上的带隙电压从ISET(165球CSP_BGA上的球A15和169球CSP_BGA上的球窝A12)连接到VNEG_N1P2,以获得参考电流。

1.2 V标称带隙电压(VREF)在9.6 kΩ电阻器RSET中产生125μA参考电流ISET。最大满刻度电流设置通过以下等式与外部电阻器相关:

IOUTFS=1.2V/RSET(kΩ)×320(mA)

配置电压参考电路时,请注意以下限制条件:

•需要9.6 kΩ电阻器和1μF旁路电容器才能正常工作。

•必须以数字的方式调整DAC输出满刻度电流(IOUTFS,默认设置为40 mA)。

•AD9164不是一个乘法DAC。不支持使用交流信号调制参考电流ISET。

•VREF引脚处出现的带隙电压必须进行缓冲,以便与外部电路一起使用,因为它具有高输出阻抗。

•外部参考可连接到VREF引脚用于强制驱动内部参考。

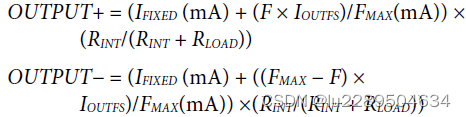

IOUTFS值可通过ANA_FULL_SCALE_CURRENT[9:0]位(寄存器0x042,位[7:0]和寄存器0x041,位[1:0])在8mA至40mA范围内进行数字调整。下面的等式将IOUTFS与ANA_FULL_SCALE_CURRENT[9:0]位相关联,这些位允许从0设置为1023。

IOUTFS=32 mA×(ANA_FULL_CALE_CURRENT[9:0]/1023)+8 mA

请注意,0x3FF的默认值会产生40 mA满量程,除非另有说明,否则该值用于本数据表中的大部分表征。

温度传感器

AD9164有一个带隙温度传感器,用于监测AD9164的温度变化。温度必须和已知温度进行校准,以消除器件之间带隙温度传感器的差异。为了校准温度,用户必须在已知环境温度下读取AD9164设备的单点校准读数。然后,公式的斜率计算为M=(TREF+190)/((CODE_REF)/1000)。其中:TREF是读取温度传感器时的校准温度。CODE_REF是测量温度TREF下的读回代码。为了监测温度变化,TX=TREF+M×(CODE_X−CODE_REF)/1000。其中:CODE_X是未知温度(TX)下的读回代码。CODE_REF是校准温度(TREF)下的读回代码。

要使用温度传感器,请通过将寄存器0x135设置为寄存器0xA1来启用传感器。在从寄存器0x132(LSB)和寄存器0x133(MSB)读取芯片温度之前,用户必须将1写入寄存器0x134的位0。

模拟输出

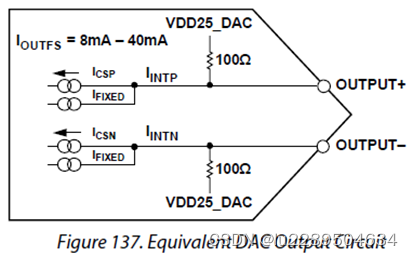

等效DAC输出和传递函数

AD9164 提供互补电流输出端 OUTPUT+ 和 OUTPUT-,可从参考 2.5 V VDD25_DAC 电源的外部负载吸收电流。图 137 显示了 DAC 的等效输出电路。与大多数此类电流输出 DAC 相比,AD9164 的输出包括一个恒定电流 (IFIXED) 和一个峰值差分交流电流 ICS(ICS = ICSP + ICSN)。这两个电流组合成图 137 所示的 IINTx 电流。内部电流 IINTP 和 IINTN 被送到输出引脚和一个相当于 100 Ω 的输入终端电阻,该电阻被拉到 VDD25_DAC 电源 (RINT)。该终端电阻的作用是根据拉至 VDD25_DAC 的外部终端电阻来分流输出电流。

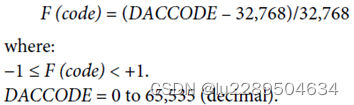

图 137 所示的示例可模拟为一对直流电流源,每个输出端都有 IOUT 电流。该差分交流电流源用于模拟 DAC 输出与信号(即数字代码)相关的性质。该交流电流源的极性和信号依赖性与数字代码 (F) 的关系如下式所示:

在 OUTPUT+ 和 OUTPUT- 输出端测量到的电流如下:

IFIXED 值约为 3.8 mA。值得注意的是,AD9164 输出无法支持与外部负载的直流耦合,因此必须通过适当大小的电容器进行交流耦合,以满足所选工作频率的要求。图 138 显示了 IOUTFS 设置为 40 mA 时的 OUTPUT+ 与 DAC 代码传递函数。

DAC 输出峰值功率能力

差分电流输出 DAC 的最大峰值功率能力取决于其峰值差分交流电流 IPEAK 和等效负载电阻。在 1:1 平衡器具有 100 Ω 差分源端接的情况下,DAC 交流电流源看到的等效负载为 29 Ω,包括 200 Ω 内部差分端接。如果将 AD9161/AD9162 编程为 IOUTFS = 40 mA,则其理想的交流电流峰值为 20 mA,在负载处测得的峰值电压为 580 mV。输送到 50 Ω 负载的均方根功率为 3.36 mW 或 5.3 dBm。

要计算输送到负载的均方根功率,请考虑以下因素:

- 数字波形的峰值有效值

- 数字满刻度的任何数字回退

- 外部网络中的 DAC sinc 响应和非理想损耗

- 开关寄生电容和负载阻抗导致的 DAC 模拟衰减

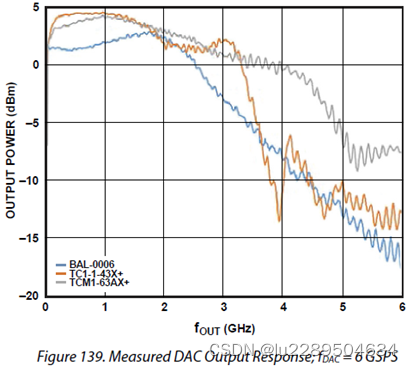

例如,没有数字衰减的正弦波理想测量值为 6 dBm。如果将 1.2 dB 的典型平衡器损耗计算在内,则在 DAC 的 sinc 响应影响可忽略不计且模拟衰减尚未开始的区域内,预计将测量到 4.8 dBm 的实际功率。提高输出功率的最佳方法是增加 IOUTFS。图 139 显示了几种平衡器和电路板类型的 DAC 输出特性示例。

|

输出级配置

AD9164 适用于需要宽信号重构带宽的高动态范围应用(如 DOCSIS 电缆调制解调器终端系统 (CMTS))和/或高中频/射频信号生成。只有当 DAC 输出配置为差分(即平衡)工作时,其输出共模电压偏置为稳定、低噪声的 2.5 V 标称模拟电源 (VDD25_DAC),才能实现最佳的交流性能。

用于连接 DAC 的输出网络为 VDD25_DAC 提供了接近 0 Ω 的直流偏置路径。OUTPUT+ 和 OUTPUT- 引脚之间的任何频率输出阻抗不平衡都会降低失真性能(主要是偶阶)和噪声性能。要发挥 AD9164 的性能潜力,元件选择和布局至关重要。

大多数需要在 10 MHz 至 3 GHz 范围内进行平衡至不平衡转换的应用,都可以利用几种阻抗比为 2:1 和 1:1 的变压器。

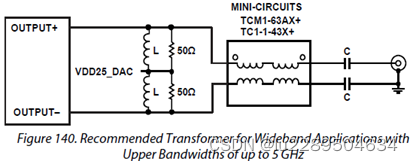

图 140 显示了 AD9164 与 Mini-Circuits TCM1-63AX+ 和 TC1-1-43X+ 变压器的接口。

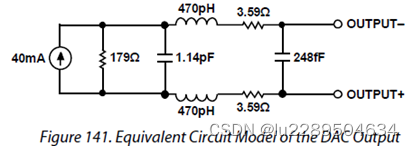

为了帮助匹配 AD9164 的输出,开发了一个输出等效模型,如图 141 所示。该等效模型包括从芯片中的理想 40 mA 电流源到 CSP_ BGA 封装球的所有效应,包括寄生电容、迹线电感和电阻、焊接凸点的接触电阻、过孔电感和其他效应。

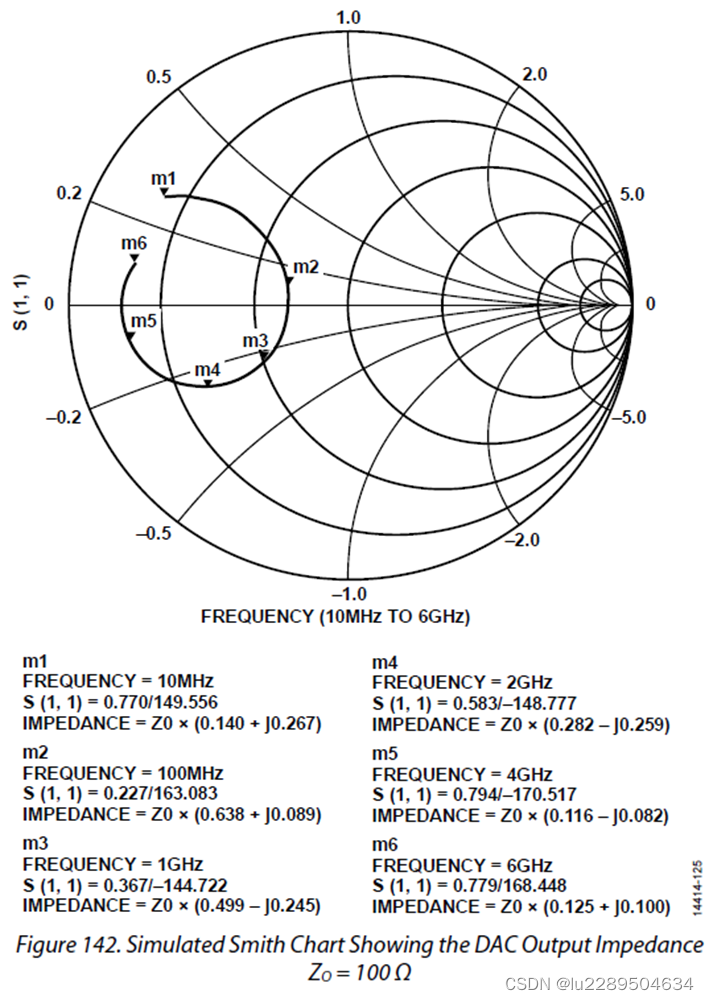

图 142 中的史密斯图显示了使用图 141 中的模型模拟的 DAC 输出 S11。该图使用图 141 中的电路绘制,用 100 Ω 差分负载代替了平衡器。DAC 输出的测量响应见图 139。

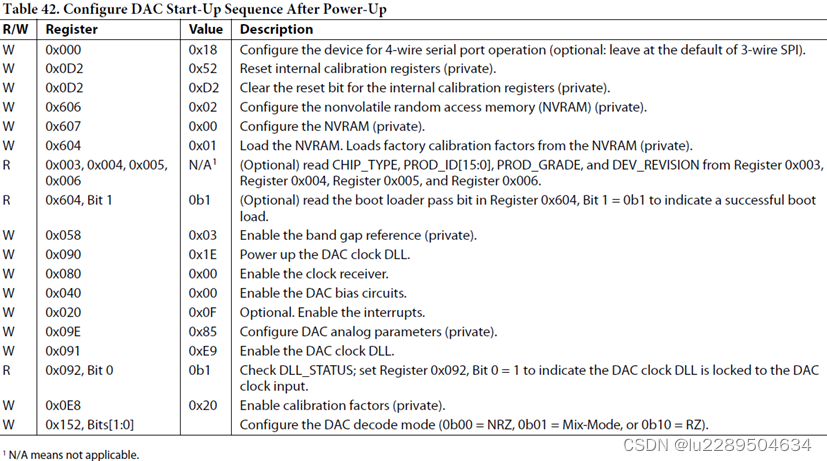

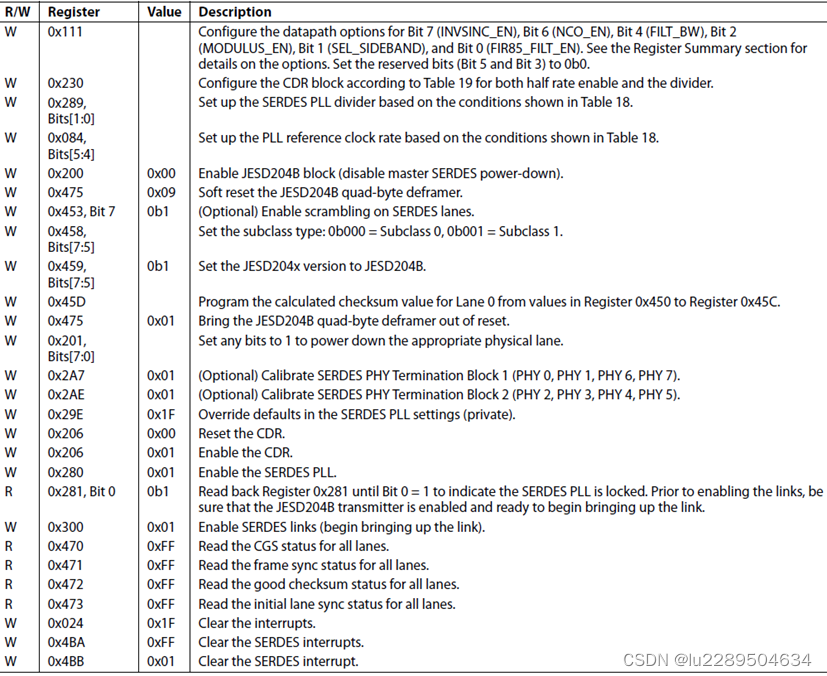

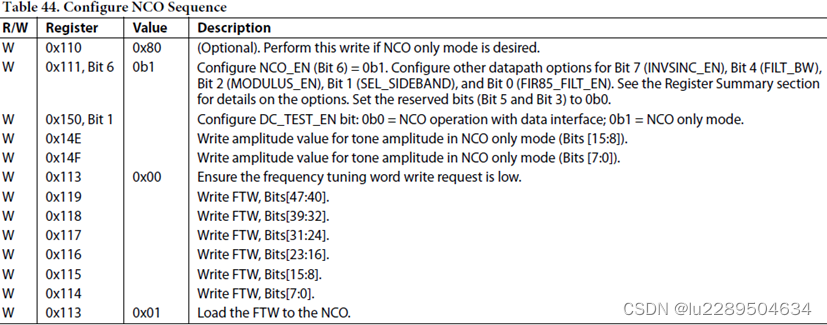

启动顺序

AD9164 上电后,需要几个步骤才能将其编程到正确的工作状态。该步骤分为表 42、表 43 和表 44 所列的几个步骤,并解释了每个步骤的目的。专用寄存器被保留,但必须写入才能正常工作。表 42 至表 44 中的空白单元表示该值取决于说明栏中描述的结果。

作为自动测试程序的一部分,AD9164 在出厂时已进行校准。配置 DAC 启动序列将加载出厂校准系数,并配置一些可优化 DAC 和 DAC 时钟 DLL 性能的参数(见表 42)。每当 DAC 断电或复位时,都要运行该序列。

配置 JESD204B 序列配置 SERDES 块,然后启动链接(见表 43)。首先运行配置 DAC 启动序列,然后运行配置 JESD204B 序列。

如果使用 NCO,则遵循配置 NCO 序列(见表 44)。请注意,NCO 可仅在 NCO 模式下使用,也可与来自 SERDES 数据接口的合成数据结合使用。一次只能使用一种模式,该模式在表 44 的第二步中选择。首先运行配置 DAC 启动序列,然后运行配置 NCO 序列。

寄存器简述

寄存器简述和详细信息详见英文版数据手册。

4583

4583

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?