1.MMCM和PLL区别

1、DCM实际上就是一个DLL(delay lock loop),可以对输入时钟进行相位移动,补偿,产生倍频和分频时钟,但是5以及以后的产品不用了。

2、PLL(phase lock loop)相对于DCM,除了不能相移时钟,其它的都一样,但是PLL产生时钟的频率比DCM更加精准,而且时钟的jitter也更好。

3、MMCM实际上就是PLL+DCM相移功能的结合体。7系列的FPGA还会在临近I/O部分放置一些PLL,专门给MIG来产生DDR时钟。

知识延伸:

一般在altera公司的产品上出现PLL的多,而xilinux公司的产品则更多的是DLL,开始本人也以为是两个公司的不同说法而已,后来在论坛上见到有人在问两者的不同,细看下,原来真是两个不一样的家伙。DLL是基于数字抽样方式,在输入时钟和反馈时钟之间插入延迟,使输入时钟和反馈时钟的上升沿一致来实现的。又称数字锁相环。

PLL使用了电压控制延迟,用VCO来实现和DLL中类试的延迟功能。又称模拟锁相环。功能上都可以实现倍频、分频、占空比调整,但是PLL调节范围更大,比如说:XILINX使用DLL,只能够2、4倍频;ALTERA的PLL可以实现的倍频范围就更大毕竟一个是模拟的、一个是数字的。两者之间的对比:对于PLL,用的晶振存在不稳定性,而且会累加相位错误,而DLL在这点上做的好一些,抗噪声的能力强些;但PLL在时钟的综合方面做得更好些。总的来说PLL的应用多,DLL则在jitter power precision等方面优于PLL。

目前大多数FPGA厂商都在FPGA内部集成了硬的DLL(Delay-Locked Loop)或者PLL(Phase-Locked Loop),用以完成时钟的高精度、低抖动的倍频、分频、占空比调整移相等。目前高端FPGA产品集成的DLL和PLL资源越来越丰富,功能越来越复杂,精度越来越高(一般在ps的数量级)。Xilinx芯片主要集成的是DLL,而Altera芯片集成的是PLL。Xilinx芯片DLL的模块名称为CLKDLL,在高端FPGA中,CLKDLL的增强型模块为DCM(Digital Clock Manager)。

Altera芯片的PLL模块也分为增强型PLL(Enhanced PLL)和高速(Fast PLL)等。这些时钟模块的生成和配置方法一般分为两种,一种是在HDL代码和原理图中直接实例化,另一种方法是在IP核生成器中配置相关参数,自动生成IP。Xilinx的IP核生成器叫Core Generator,另外在Xilinx ISE 5.x版本中通过Archetecture Wizard生成DCM模块。Altera的IP核生成器叫做MegaWizard。另外可以通过在综合、实现步骤的约束文件中编写约束属性完成时钟模块的约束。

(一)、PLL原理

PLL(Phase Locked Loop),生成时钟的核心部分是压控振荡器(Voltage-Controlled Oscillator,VCO)。它是可根据输入的电压调整输出频率的振荡器,如下图所示。

它的基本原理是通过负反馈形成闭环从而根据输入的基准时钟控制输出时钟。其中鉴相器就相当于一个比较器,它根据基准时钟和输出时钟的差值转换为控制电压,输出到低通滤波器滤除高频杂波,然后输入到VCO,VCO主频过高则降低电压,反之提升电压,使输出时钟跟随给定的基准时钟。

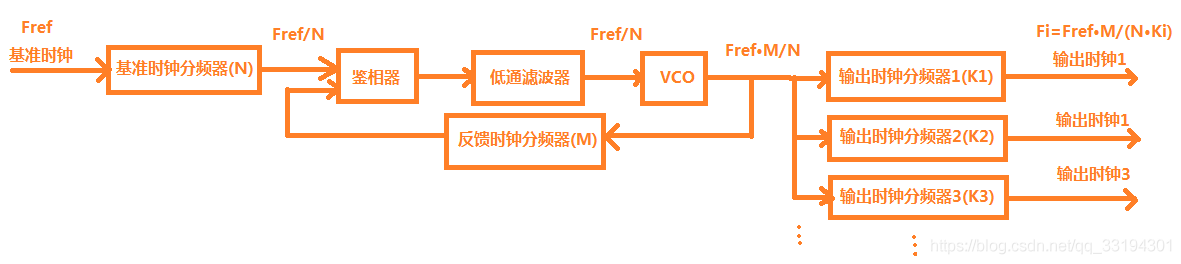

下图是FPGA典型的PLL块。各阶段的时钟频率说明如下。

- 基准时钟经过分频器后输出频率为Fref/N,并输入到鉴相器。

- 为了要让鉴相器与反馈频率相同,VCO的输出频率Fvco需要让反馈频率在经过反馈时钟分频器后输出到鉴相器的频率和分频后的基准时钟频率相同,所以Fvco=M/N·Fref。

- Fvco经过输出时钟分频器输出的时钟为 Fi=Fref·M/(N·Ki) ,其中Fi为输出频率,Fref为基准时钟的频率,Ki为输出时钟分频比,N为基准时钟分频比,M为反馈时钟分频比。

DLL(Delay Locked Loop),它不同于PLL使用VCO,它使用的是可变延迟线来控制时钟信号的延迟量,如下图所示,它可实现受控时钟和输入时钟的相位跟踪,通过调整基准时钟到受控时钟的来实现。它能消除时钟分配网络引起的时钟偏移,也可通过整合分频器来输出不同频率的时钟。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?