存算一体进入到版图设计步骤了,速速自学下基础内容,参考b站upnksunmoon(讲的很不错)。

一、寄生参数

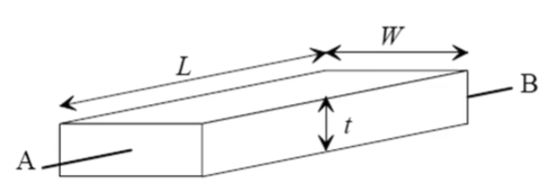

对于一块电阻,其阻值为

其中ρ为电阻率,t为高度,其比值称为方块电阻,对于一定的工艺而言,其金属层厚度和电阻率都是一定的。

1.导线模型

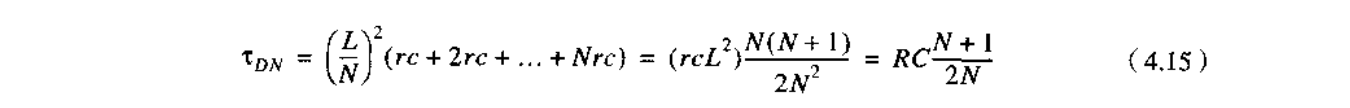

对于RC延迟的计算有集总模型和分布式模型两种,它们都是将一条长导线切割为n块小导线。为了后续便于理解如何降低RC,做简单介绍:

集总模型就是将n段导线的电阻和电容约化成一个电阻和电容。

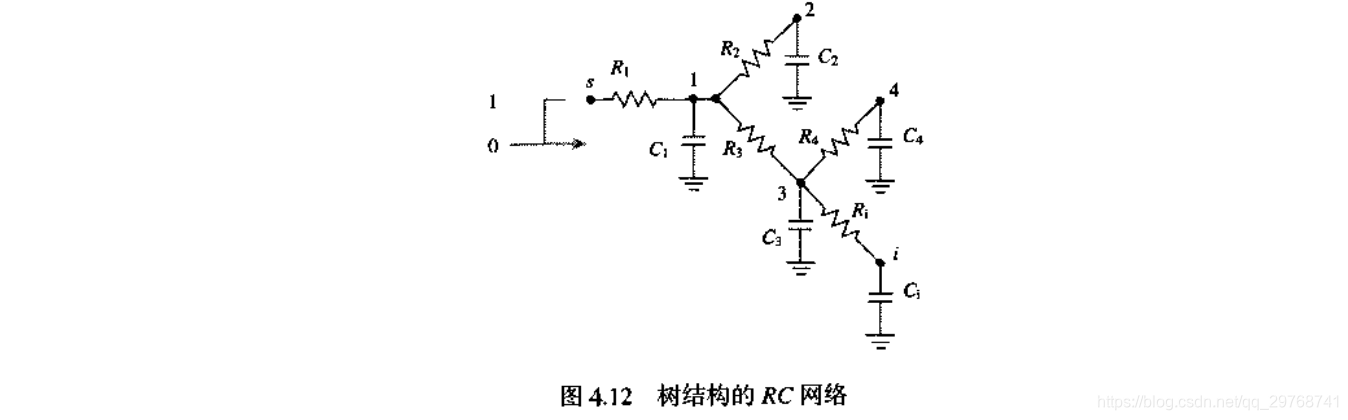

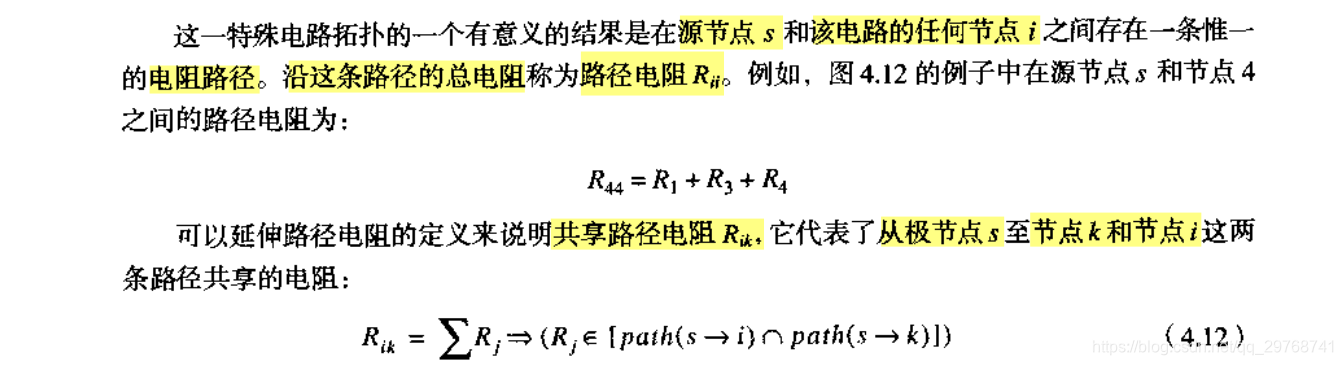

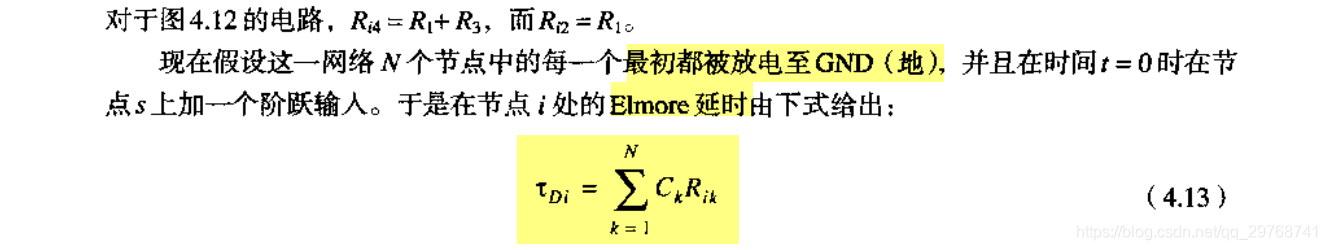

而分布式模型则考虑导电阻抗,引入树结构的RC模型

对于一条单路径的导线,即为将所有从出发节点到某一结点的电阻乘这个节点的电容的值加起来,得到总延迟。

对于一条单路径的导线,即为将所有从出发节点到某一结点的电阻乘这个节点的电容的值加起来,得到总延迟。

由此得到几个重要结论:

1.导线延迟与长度呈二次方关系

2.分布模型是集总模型延迟一半

一般地,采取集总模型进行估计,若频率要求小于RC,则可以认为不理想。

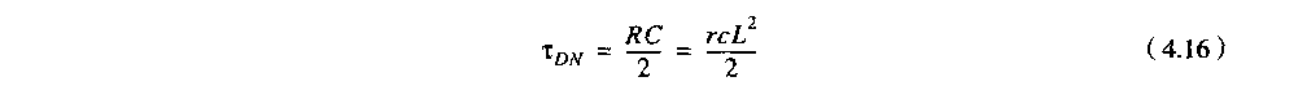

2.工艺中存在的寄生

从上图可以看出,.18工艺厚度一般为0.5微米。对于简单的两层金属,就存在多种寄生电容

在拉书中,给出当栅氧厚度为2n时,单位面积栅氧电容为17.25fF/μm2.

二、失效机理

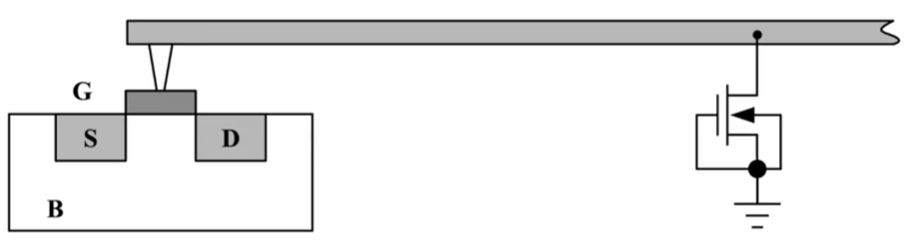

1.天线效应

栅通过金属线连接出去后,由于干法刻蚀加工金属的时候,大量带电粒子会注入到金属中,提高电场强度。如果太大,就会击穿栅氧。线越长,积累的电荷就越多。但与栅氧接触面积是一定的,所以会增强电场。

为了消除这一效应,有两种方法:第一是叫跳层法,说的是把原本很长的一段金属打断,在中间打通孔连到上层或下层,在后续将这些电荷释放掉,然后再通过通孔连回来。这样在计算天线效应比率的时候就能少算金属层的面积。这种方式尽量在临近gate的地方切断。第二种方法是在发生violation的net与地之间插入diode,这样聚集的电荷就会优先走diode这条路,就避免损坏MOS管。这两种方法都有一定缺点,第一种方法会产生更复杂的绕线,并且会影响原net的timing等,而第二种方法产生更复杂绕线的同时还要加入额外的器件,cell density比较高的情况下就更难摆放。

例如通过将mos栅源相连形成二极管(注意与二极管连接器件区分),当金属线上的电荷大到反向击穿二极管的时候,会产生极大的反向击穿电流,释放电荷,但会占用较大面积(为何不正向连接?是因为二极管存在0.6V内建电势会锁住金属线电压吗?是的,而且正向连接相当于提供了别的通路)

2. 软连接

如果画版图不设置衬底,会以远处的阱为衬底,形成较大的衬底压降。在释放掉栅极电压后,残留在沟道的电荷会向低压处扩散,影响栅电压。

在DRC中,会注明pick-up,即多少范围内需要有衬底。

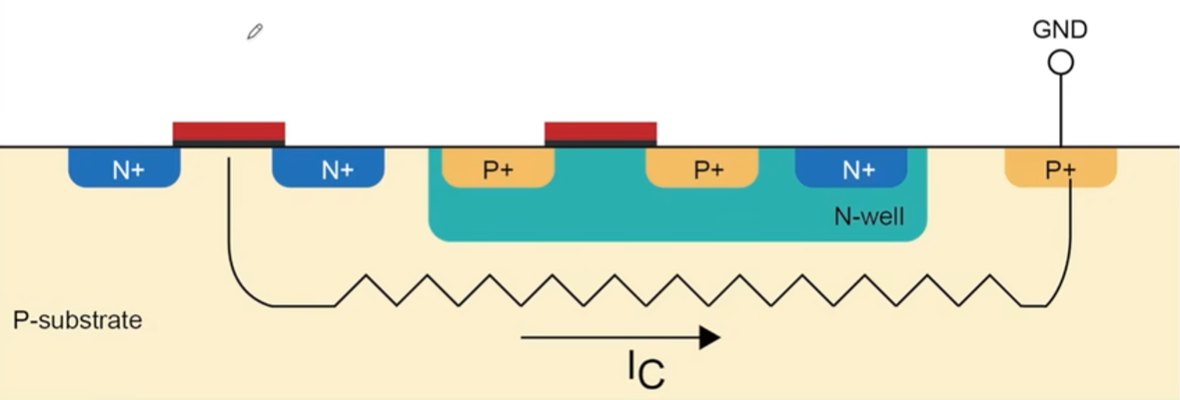

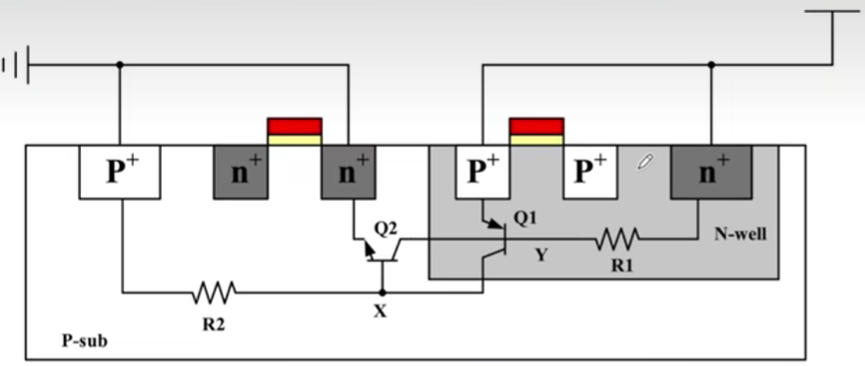

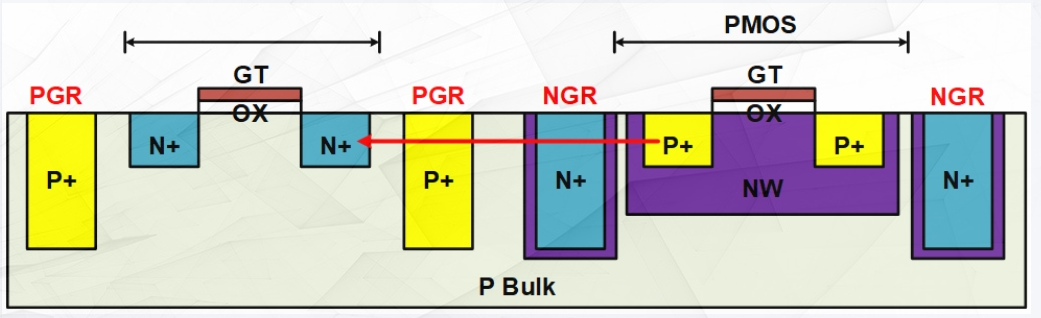

3.闩锁效应

对于一个反相器而言跳动的电压会使内部自发构成的三极管开启,释放极大的电流。

有两种解决方式:降低R1,R2,或者降低三极管放大倍数(这个由工艺决定)

版图上来讲一般添加保护环。

即在有源区周围围一圈“衬底”,相当于降低了R。

4.电迁移

金属线里电流太大,引起金属线断裂或者金属脱离造成短路。

pdk里会标注走线电流密度。一般用top metal来走电源。多画几个通孔的原因之一也是防止通孔承受不住。由于pdk对金属层的厚度做了约束,工艺上不可改变,可以将一层走线拆成两层金属并联来走,变相增加电流密度。对于趋肤效应,同样可以将宽走线拆成并联。

5.金属应力

由于热效应,金属会收缩变形。通过给金属打孔(slot)的方式,提供其收缩的裕度。DRC里会提供。

三、基本器件

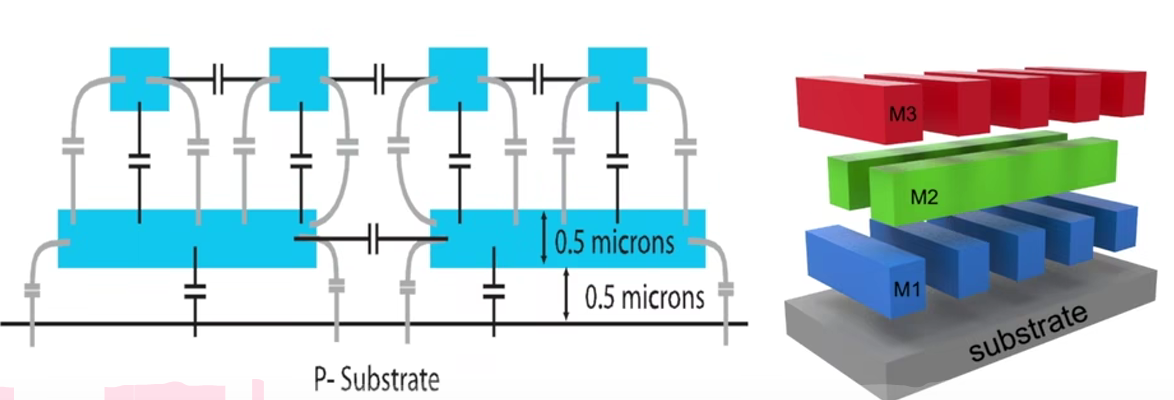

1.mos

通孔要均匀放置,不然由于通孔电阻比较低,沟道电流几乎都沿着最近处流动。

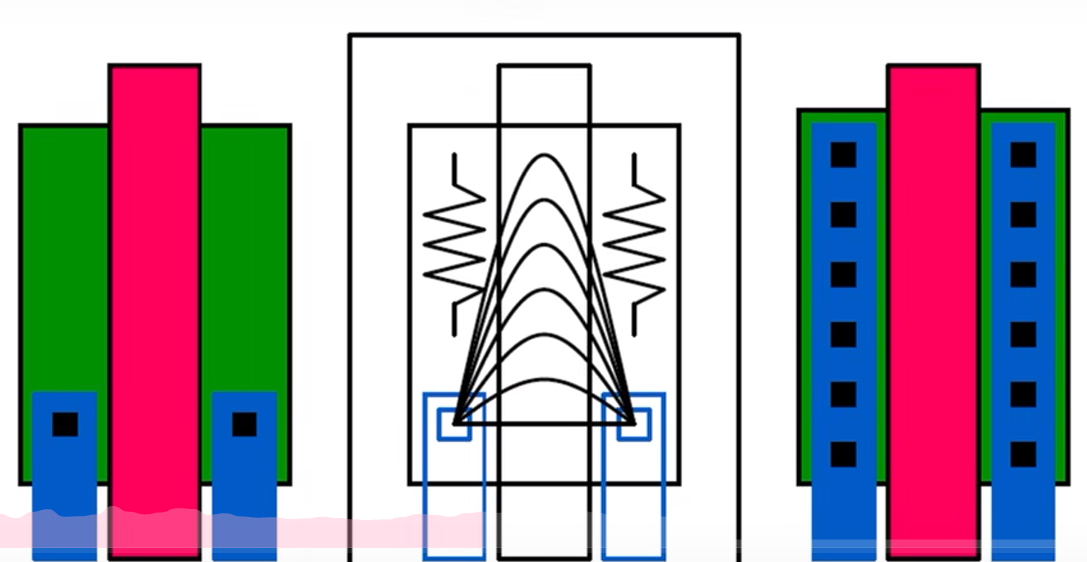

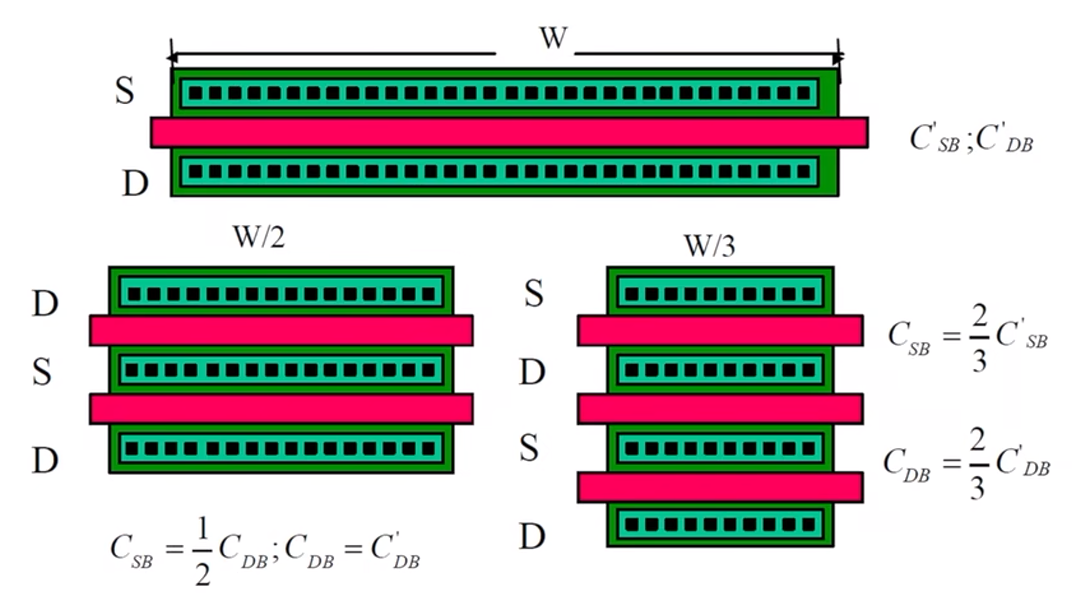

对于长的W,可采取叉指结构降低栅电容和源衬、漏衬电容,以及额外的寄生电阻。

如上图源漏交替的形式。但f太多会造成应力效应。

也可以采取设置M的方式,即切成多段,平行关系,可以避免STI,但寄生降低效果差且会重复调用很多dummy来避免非理想因素,占用更多面积。

这儿有一个有意思的题外话。可以发现现在采用的单阱工艺大多都是p衬底,pmos做里面。这主要是下面几个原因。一是nmos速度快,二是p衬底要接地,接地这个事在集成电路里相比接电源容易且稳定地多。

但事实上,pmos是要比nmos出现的早的。这是因为早期工艺对于有源区采取扩散而不是现在的注入工艺,硼等p型掺杂材料要比磷等n型掺杂材料扩散速度快,可以更容易制作pmos。另一方面,早期工艺精度较低,对于nmos需要正的阈值电压,但因为杂质掺杂效果差,阈值电压很容易变得低,因此采用pmos后阈值电压直接负的了,可以缓解这个问题。

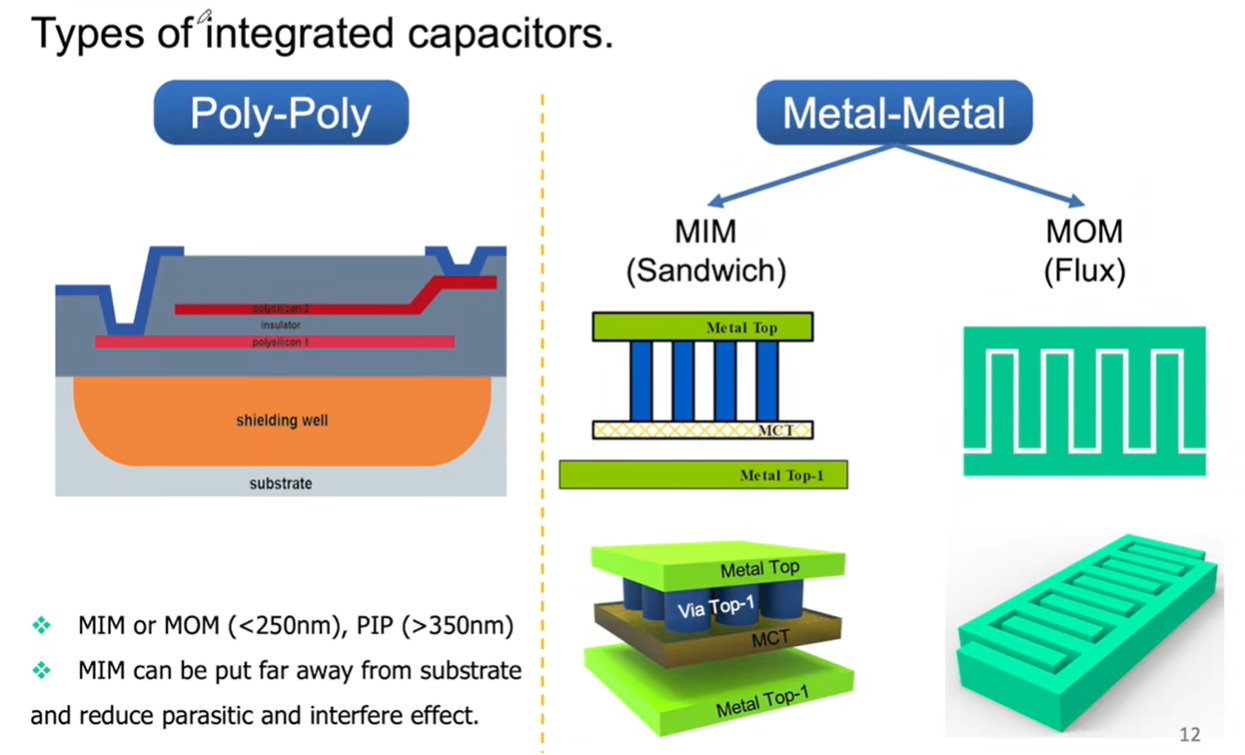

2.电容

电容分为多晶硅-绝缘体-多晶硅,金属-绝缘体-金属和金属-氧化物-金属三种。

对于pip,需要pdk要2p以上。

对于MIM,工艺上会额外提供一层金属MCT,让上层金属、通孔和MCT构成电容的上极板,降低d从而增加单位面积电容。

对于MOM,在一层金属上采取叉指结构,增加等效面积。

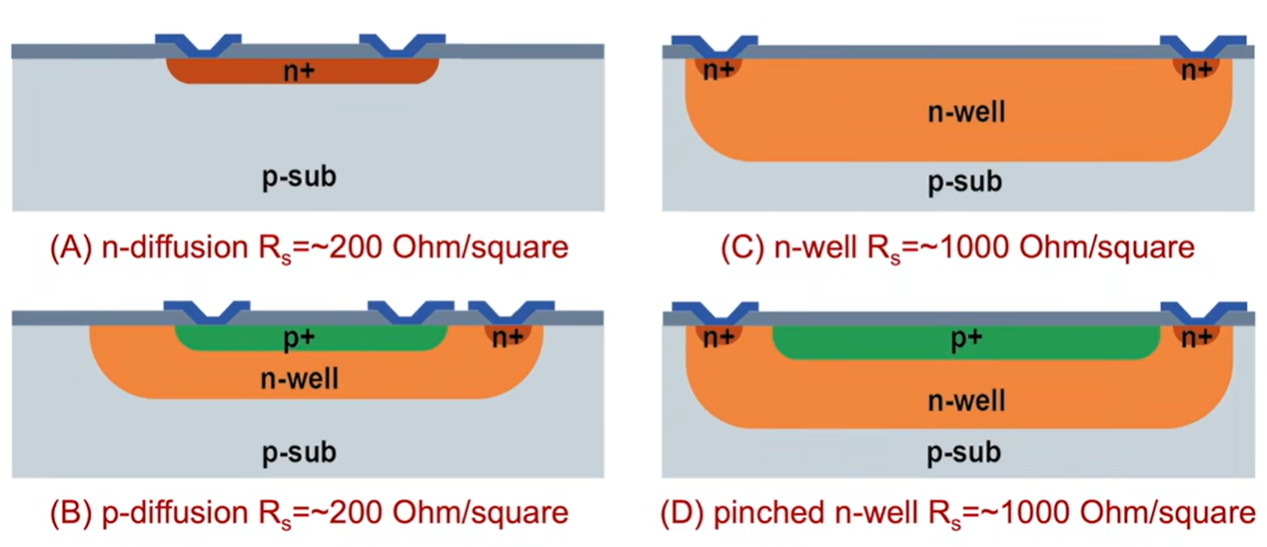

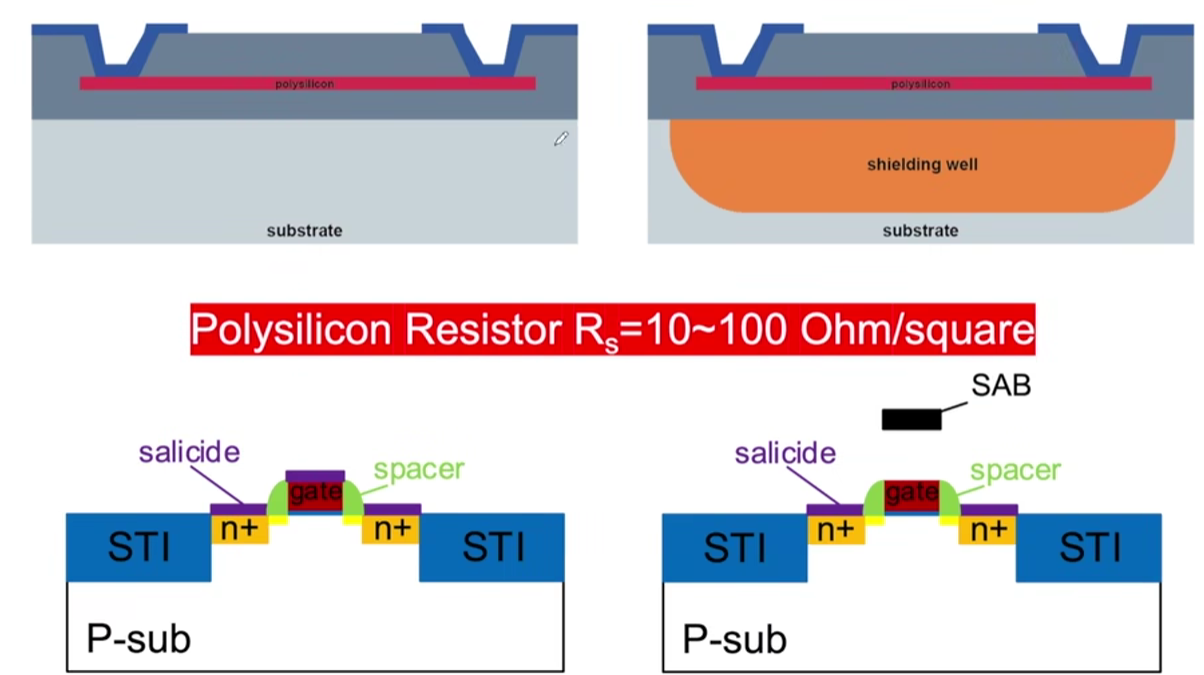

3.电阻

常见的电阻有以上几种,n注入的n+电阻,在n阱里p注入的p+电阻,由n阱构成的电阻以及添加p注入的钳位n阱电阻。对于c和d,由于二氧化硅和n阱之间存在晶格断裂造成的悬挂键,会带来噪声。而通过添加p+并将它接地,可以钳位到0,且p+和n-well都是sio2,晶格连续。

另外还有采用poly做电阻的,它的阻值就更低了。如果想增大阻值,可以用SAB(salicide block)屏蔽掉salicide的沉积,例如电阻rpposab。

经常会看见三端电阻,对于n阱电阻,多出来的一端接地,从而减小噪声。

五、匹配

匹配的概念困扰了lz很久

非理想因素

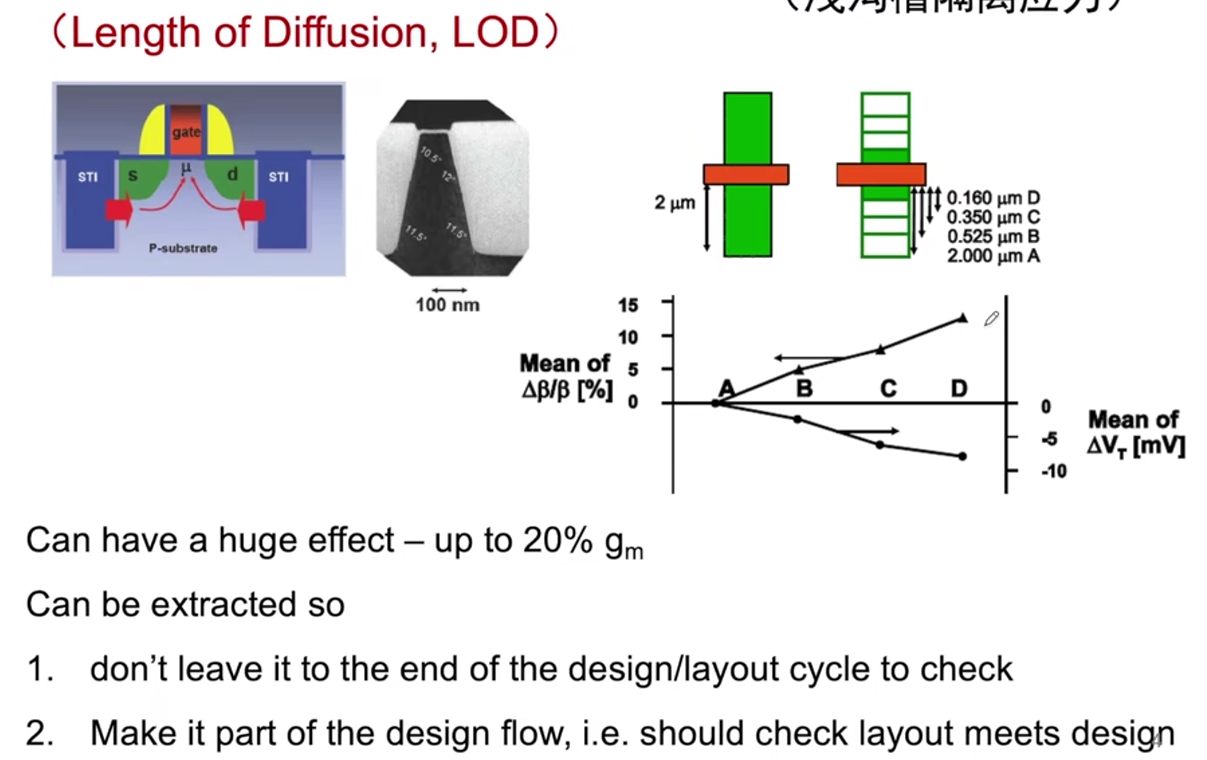

1.浅沟槽隔离带来的应力

由于浅沟槽隔离采用STI为SiO2,而衬底是Si,两种热系数不同,STI会更易膨胀,挤压周围;甚至影响沟道的扩散长度,效果随距离缩短。因此可以增加有源区长度来解决这个问题。但增加多少似乎没有一个定量的要求。一般通过在源漏两端添加dummy来缓解,且dummy需要和被保护管共有源区才有效。

2.WPE阱偏置效应

阱边缘和远离边缘的晶体管阈值电压会不一样。对于阈值电压和体效应要求较高的设计,可以将器件到阱四个方向的距离都加大,一般2微米足够。相同电位的阱可以放一起合并来减少阱数量。对于对称性要求比较高的电路(如电流镜、差分放大等),设计者应该尽量采取单元模块调用的设计方法。先作一个单元模块具有一定长度和宽度的管子,其它的管子都以这单元模块为单元进行重复调用,组成新的管子。

3.PPE多晶硅邻近效应

面积大的多晶硅刻蚀慢。这个效应遇到的不是很多。也通过dummy缓解

4.metal over transistor

在退火时,会注入氢气带走氧,但被金属盖住的晶体管会影响氢气的进入。画金属层尽量少遮挡下层器件。

5.非对称

沿110晶面生长的硅会存在晶格间隙,垂直注入会打的很深,这样阈值电压会变低。一般倾斜7°注入。这就带来左右两侧非对称的离子注入。

6.侧边刻蚀

刻蚀的时候被刻蚀区边缘也会受刻蚀,因为尺寸偏差。因此例如电流镜的对管,W,L尽量相同,去修改m和f。

7.随机失配

这个没什么好说的。。。

解决方法

这里简单介绍,实例中分析。

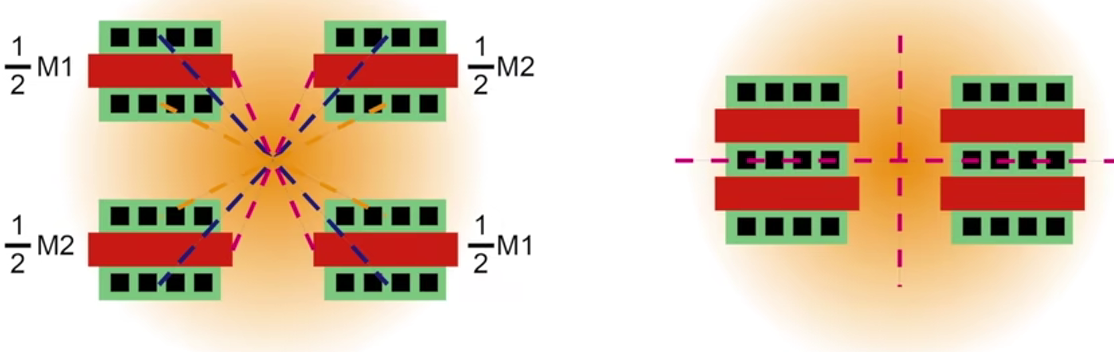

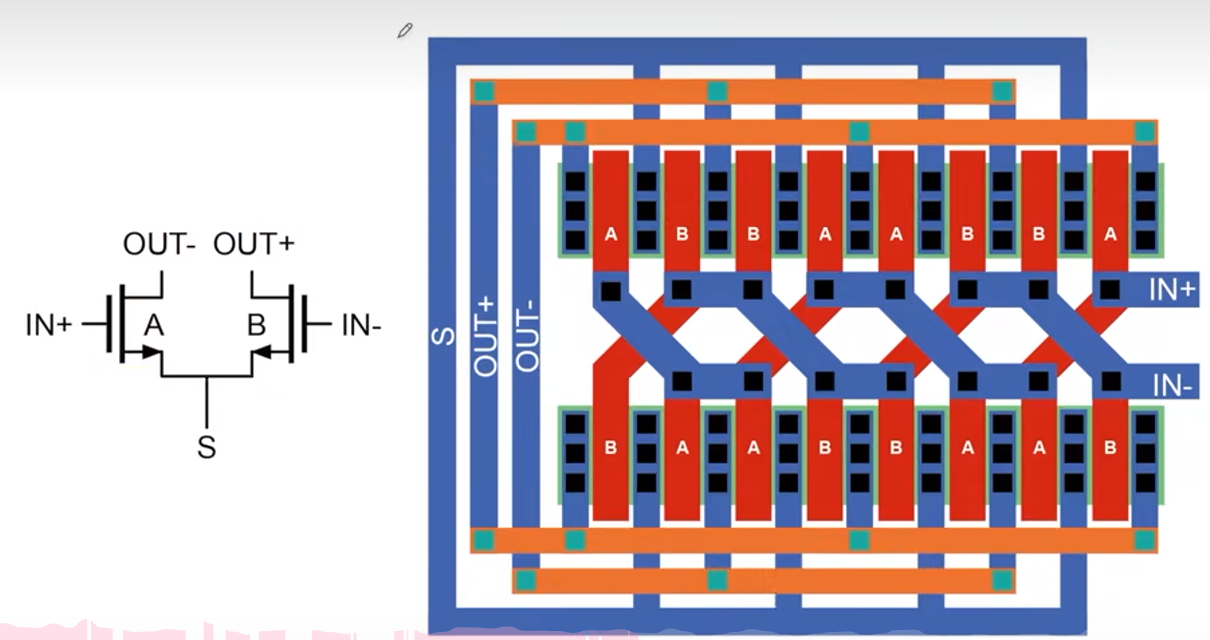

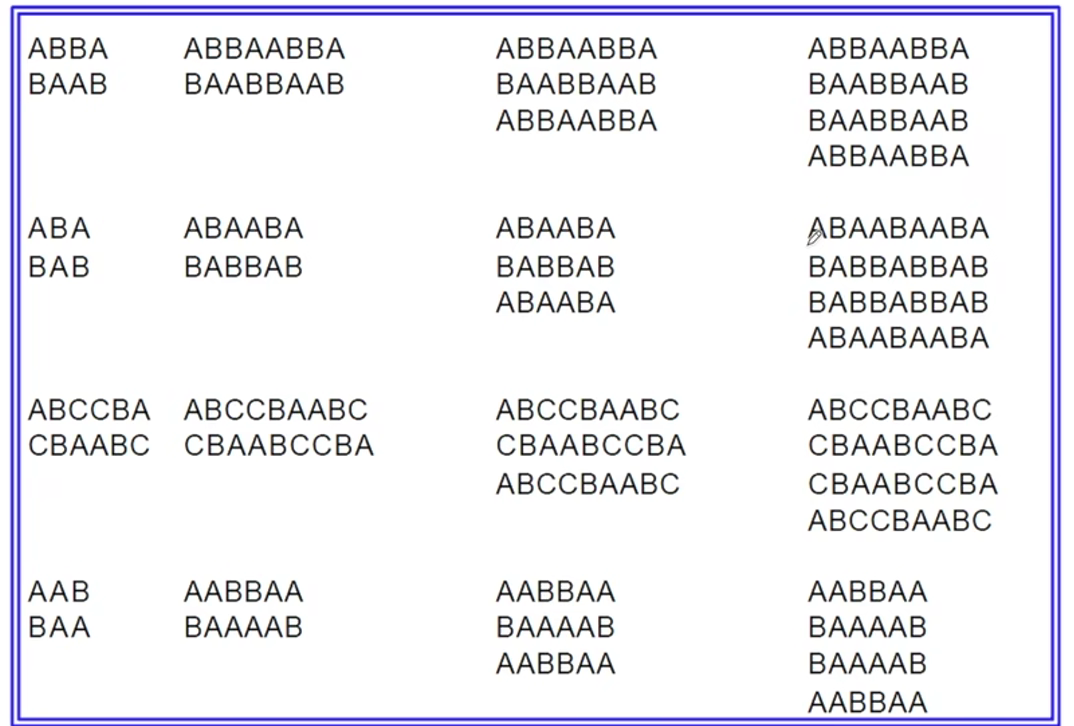

常用的方式有上面说的加dummy,根据情况采用叉指或multi,以及最重要的质心放置,即将器件质心落到同一点,例如电流镜中复制管的multi可采用4或者8围着中间的管子形成方形。=但一般画版图时会先统一m或f

上图是一对差分管采用finger=8时的共质心摆放方式,而且注意到部分栅极的连接采用poly,可以省去一层金属层。

上图是常用共质心摆放方法。

此外下,尽量采用单元器件,然后复制它,而不是直接成倍地增加W或L,以避免侧边刻蚀的影响

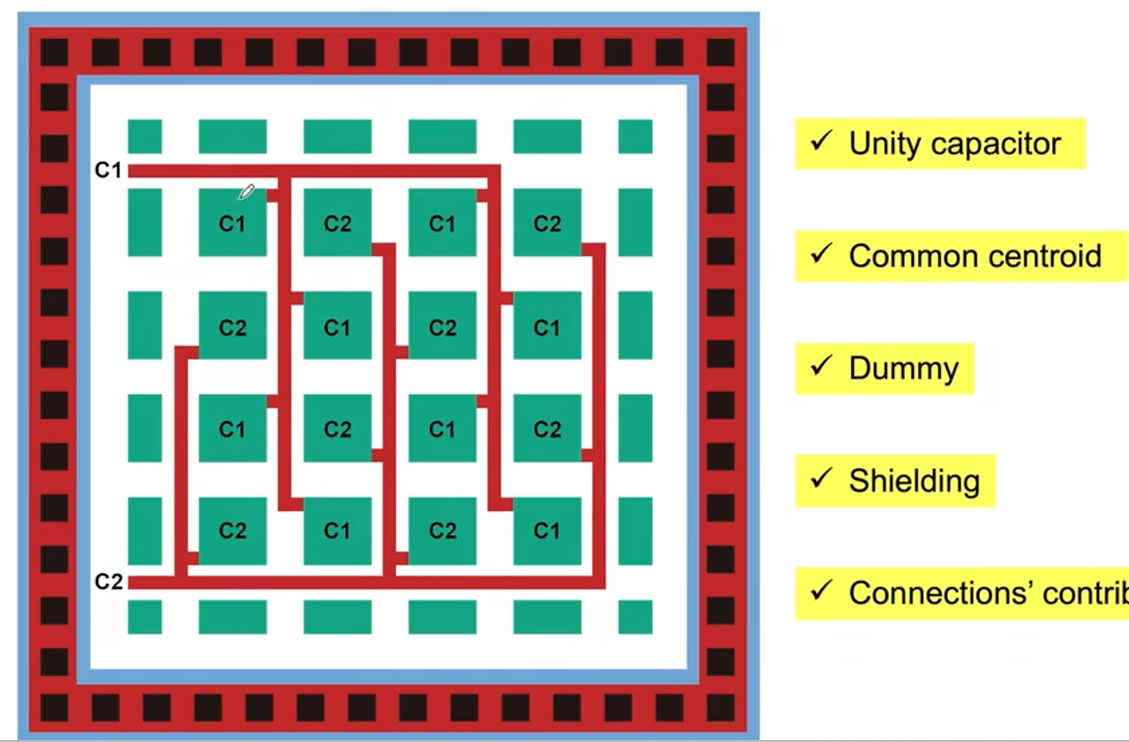

电容的匹配

电容的匹配和mos类似

值得注意的是,dummy电容并不需要和单元电容等大。外面围了一圈guard ring接地屏蔽衬底噪声。此外电容尽量远离功率器件。使用较大的单元电容可以降低边缘效应和失配。

电阻匹配

类似mos

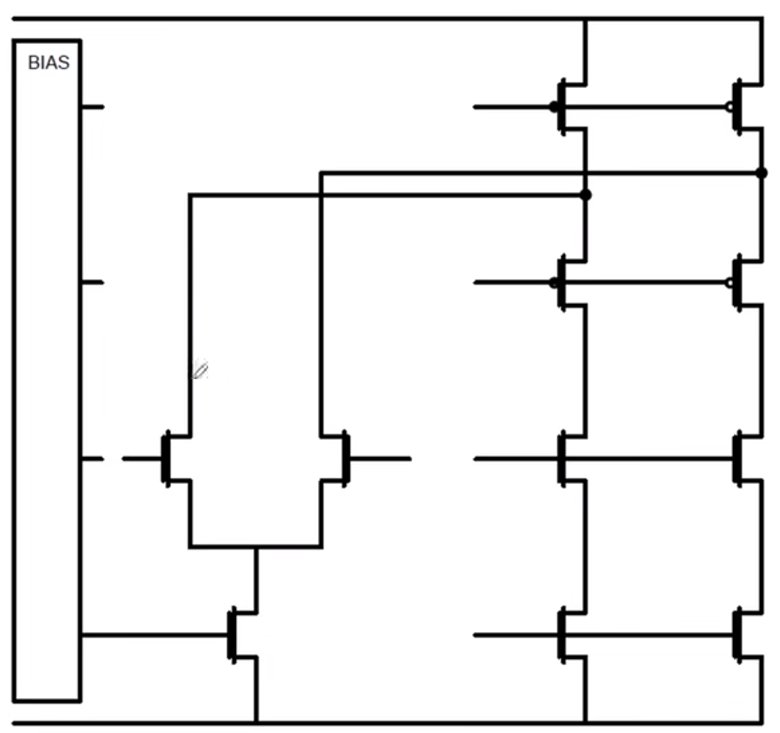

以折叠共源共栅为例

对于.18以上工艺,可采用晶体管级symmetry,即所有器件都采用共质心摆放,然后每对管为一层叠放。但这样连线复杂

对于.18以下,采用顶层symmetry,左右对称,偏置放中间。

也可以混用,关键管子采用共质心,

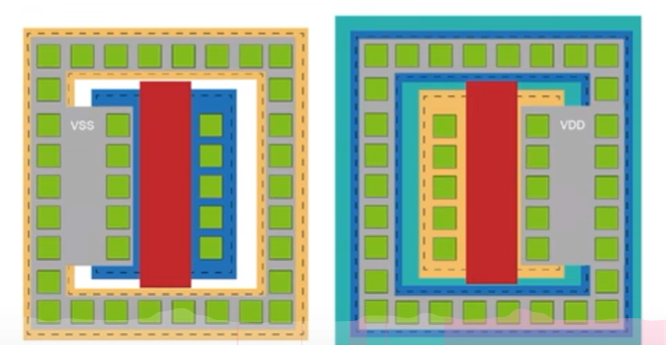

六、噪声

1.串扰

由于寄生电容的存在,时钟信号跳变会引起电压抖动,即毛刺

2.近场电磁

连线发出的磁场干扰周围连线引起电场变化

3.衬底噪声

衬底本身带电阻引起对别的器件的电压变化

解决方式

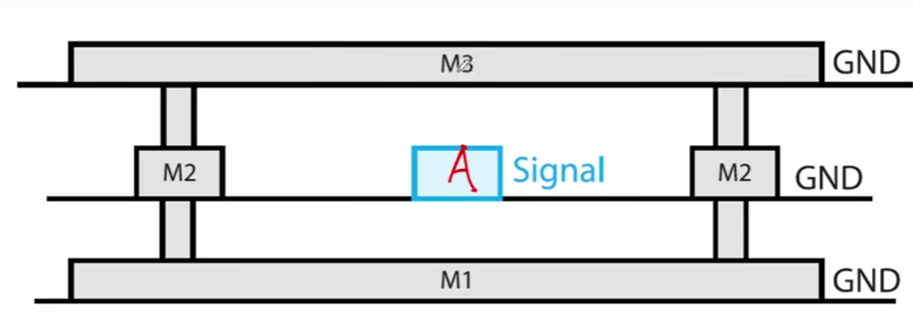

同轴线屏蔽

三层金属构成个环,类似同轴线。

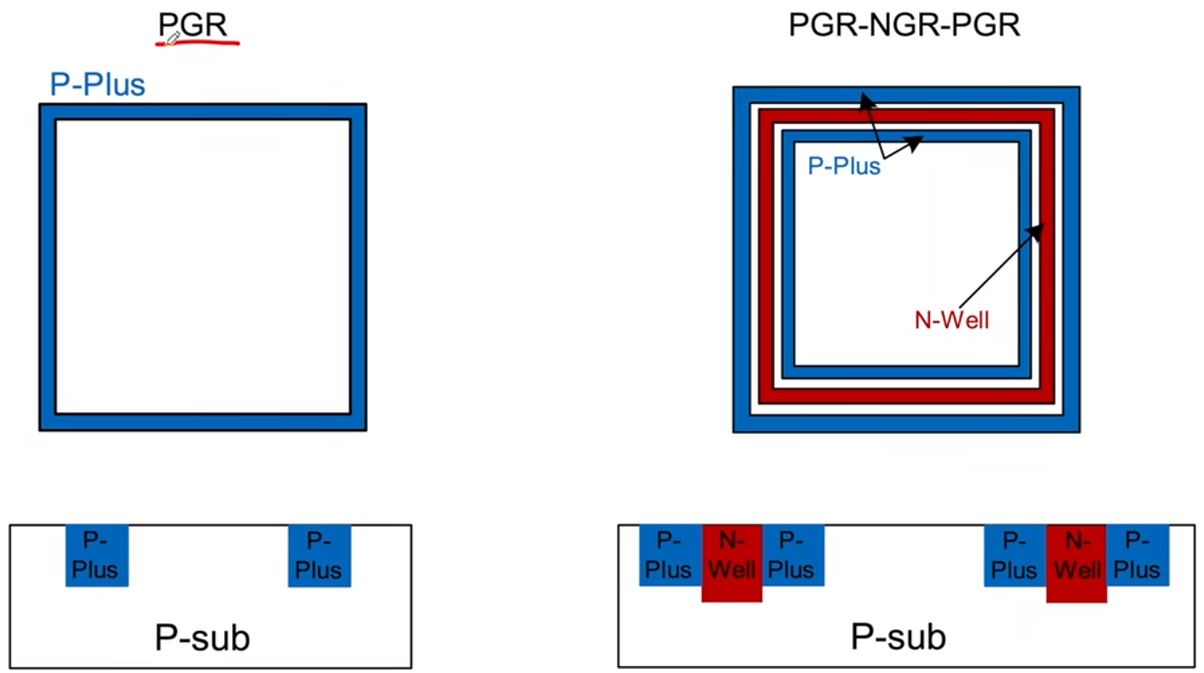

保护环:

设立一个接地的环,外部噪声会优先流向这个“口”。右图利用n阱和p+构成反偏pn结,将噪声“弹出去”。在n阱工艺中剖面如下。

最后对于有源区和P/N PULS的区别,如果只学过半物,可能容易跟版图里的说法混淆,这里从eetop找到一个很妙的解释:

1、什么是场氧?

场氧是指硅衬底上的SiO2氧化层,由于它比较厚也叫厚氧,可以对离子扩散、注入起阻挡作用。

2、什么是有源区?diffusion?

有源区是场氧(厚氧)的开槽,它上面也会有一层薄氧(thin oxide),可以用来形成多晶硅下的栅氧,在多晶硅栅MOS工艺流程中是先形成poly栅再进行源漏掺杂的(该操作可以使源漏和poly 沟道自对准),实际进行掺杂的区域我们叫它diffusion(Ndiffusion/Pdiffion),很显然有源区并不等于diffusion,而是包含关系。

3、什么是PP/NN?

PP是指P型注入/扩散区,又称pplus、p-implant;NN指N型注入/扩散区,又称nplus、n-implant。

PP和NN其实是在硅片衬底上划定的一个区域,用来限定离子扩散/注入的操作范围,为了使有源区的边边角角完全完成掺杂,那么这个限定的操作范围就必须比有源区大,包含全部有源区,这就是版图中pp要比diffusion区域大的原因,pp是同时覆盖有源区和部分场氧的。这么说,假设你只想在硅衬底上做1个PMOS的话,确定有源区后你甚至可以把pp铺满整块硅片(就是有点浪费掺杂离子源),但就是不能比有源区小!

来打个比方,假设你家院子全是水泥地,这可以比作场氧,你想在上面敲掉一块水泥把下面的土漏出来用来种菜,这种菜的区域就是有源区,这种上的菜就是掺杂,种不同种类的菜就是不同的掺杂类型。那你撒种子的时候为了保证每一寸土壤都被种子覆盖,种子就难免会撒到水泥地上,你撒种子的这个范围就是pp/nn的范围,当然你可以把种子撒满你的院子,但只有土壤区域会长出菜苗...

综上所述,你提问中补的这一小块pp就是为了满足fab drc要求的pp包diffusion最小范围,fab已经过多次验证应该不会有什么问题,但是为了使diffusion掺杂更加完美、更加保险,你可以把pp适当的画的更大,包的更多。

3901

3901

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?