DC综合软件的使用有两种方法,一种是在图像界面下操作,另一种写一个脚本文件,对于大多数人,还是习惯图形界面点点点,但是亲测,发现真的很烦,因为要设置一堆东西,如果你在综合后出现问题,你修改你的代码,然后你还有重新设置一遍,结果就是每次你都要重新设置一边,综合次数多了,你会发现真的太烦了,浪费时间,所以写脚本文件很有用。

下面讲一下怎么写脚本文件

首先建一个文件夹,把你要综合的文件放进去,新建一个文件,以.scr为后缀,比如fir.scr

文件内容为:

1.首先时定义路径:

定义库文件存在的位置,命令是set my_lib_path "库文件位置“,比如

set my_lib_path "/home/smic180/digital/sc/synopsys/ /home/smic180/digital/io/synopsys/ /home/smic180/digital/sc/symbols/synopsys/"

定义搜索路径命令:set search_path "$search_path+$路径",比如set search_path "$search_path $my_lib_path "

定义一些库文件命令:

set target_library "typical.db"

set synthetic_library "dw_foundation.sldb"

set link_library "* typical.db * SP018N_V1p0_typ.db $synthetic_library"

set symbol_library "smic.sdb"

这个库文件命令里面的文件对应你自己电脑里面的库文件,所以要对应改成自己的电脑文件。

然后,我们在综合时会有一些警告,我们去除一些不重要的警告,命令:

suppress_message VER-130

suppress_message VER-129

suppress_message VER-318

suppress_message ELAB-311

suppress_message VER-936

然后是读入文件命令:

read_file -format verilog {/home/IC/Desktop/fir/fir/fir.v},命令最后是verilog文件路径,改成自己的

接着把文件设置为顶层命令:current_design fir

然后LINK命令:link

之后是设置时钟,输入,输出等等

set clk [get_ports clk] 设置时钟,我的verilog时钟名字是clk,需要改成你自己的

set reset [get_ports reset] 设置复位,我的verilog复位名字是reset,需要改成你自己的

set general_inputs [list filter_in] 设置输入,我的verilog输入名字是filter_in,需要改成你自己的

set outputs [get_ports filter_out] 设置输出,我的verilog输出名字是filter_out,需要改成你自己的

然后是设置时钟约束,我们设置50Mhz时钟

#1 set constraints for clock signals

create_clock -n clock $clk -period 20 -waveform {0 10} 50Mhz为20ns,所以前面写20,我们在前10ns是高电平,后10ns是低电平,所以是{0 10}

set_dont_touch_network [get_clocks clock]

set_drive 0 $clk

set_ideal_network [get_ports clk]

然后设置复位约束

#2 set constraints for reset signals

set_dont_touch_network $reset

set_drive 0 $reset

set_ideal_network [get_ports reset]

然后设置输入输出约束

#3 set input delay

set_input_delay -clock clock 12 $general_inputs

#4 set output delay

set_output_delay -clock clock 12 $outputs

编译命令:

compile_design

compile -map_effort medium

把数据写入文件和报告面积,时间,功耗命令:

write *.db and *.v

#write -f db -hier -output ./fir.db fir

#write -f verilog -hier -output ./firnetlist.v fir

write_sdf -version 1.0 ./fir.sdf

write_sdc fir.sdc

write -f ddc -hierarchy -output fir.ddc

write -hierarchy -format verilog -output firnetlist.v

#1

uplevel #0 { report_area }

#2

uplevel #0 { report_constraint -all_violators -significant_digits 2 -nosplit }

#3

uplevel #0 { report_timing -path full -delay max -nworst 1 -max_paths 1 -significant_digits 2 -sort_by group }

#4

uplevel #0 { report_power -analysis_effort low }

整个完整的fir.v文件:

module fir

(

clk,

reset,

filter_in,

filter_out

);

input clk;

input reset;

input signed [7:0] filter_in; //sfix8

output signed [19:0] filter_out; //sfix21_En12

//Module Architecture: fir

// Local Functions

// Type Definitions

// Constants

parameter signed [10:0] coeff6 = 11’d6; //sfix10_En12

parameter signed [10:0] coeff5 = 11’d5; //sfix10_En12

parameter signed [10:0] coeff3 = 11’d3; //sfix10_En12

parameter signed [10:0] coeff1_ = -11’d1; //sfix10_En12

parameter signed [10:0] coeff9_ = -11’d9; //sfix10_En12

parameter signed [10:0] coeff19_ = -11’d19; //sfix10_En12

parameter signed [10:0] coeff33_ = -11’d33; //sfix10_En12

parameter signed [10:0] coeff49_ = -11’d49; //sfix10_En12

parameter signed [10:0] coeff66_ = -11’d66; //sfix10_En12

parameter signed [10:0] coeff84_ = -11’d84; //sfix10_En12

parameter signed [10:0] coeff99_ = -11’d99; //sfix10_En12

parameter signed [10:0] coeff109_ = -11’d109; //sfix10_En12

parameter signed [10:0] coeff112_ = -11’d112; //sfix10_En12

parameter signed [10:0] coeff105_ = -11’d105; //sfix10_En12

parameter signed [10:0] coeff72 = 11’d72; //sfix10_En12

parameter signed [10:0] coeff157 = 11’d157; //sfix10_En12

parameter signed [10:0] coeff256 = 11’d256; //sfix10_En12

parameter signed [10:0] coeff365 = 11’d365; //sfix10_En12

parameter signed [10:0] coeff482 = 11’d482; //sfix10_En12

parameter signed [10:0] coeff599 = 11’d599; //sfix10_En12

parameter signed [10:0] coeff712 = 11’d712; //sfix10_En12

parameter signed [10:0] coeff814 = 11’d814; //sfix10_En12

parameter signed [10:0] coeff901 = 11’d901; //sfix10_En12

parameter signed [10:0] coeff966 = 11’d966; //sfix10_En12

parameter signed [10:0] coeff1007 = 11’d1007; //sfix10_En12

parameter signed [10:0] coeff1021 = 11’d1021; //sfix10_En12

reg signed [19:0] r0, r1, r2, r3, r4, r5, r6, r7;

reg signed [19:0] r8, r9, r10, r11, r12, r13, r14, r15;

reg signed [19:0] r16, r17, r18, r19, r20, r21, r22, r23;

reg signed [19:0] r24, r25, r26, r27, r28, r29, r30, r31;

reg signed [19:0] r32, r33, r34, r35, r36, r37, r38, r39;

reg signed [19:0] r40, r41, r42, r43, r44, r45, r46, r47;

reg signed [19:0] r48, r49, r50, r51, r52, r53, r54, r55;

reg signed [19:0] r56, r57, r58, r59, r60;

reg signed [19:0]x6 ;

reg signed [19:0]x5 ;

reg signed [19:0]x3 ;

reg signed [19:0]x1_ ;

reg signed [19:0]x9_ ;

reg signed [19:0]x19_ ;

reg signed [19:0]x33_ ;

reg signed [19:0]x49_ ;

reg signed [19:0]x66_ ;

reg signed [19:0]x84_ ;

reg signed [19:0]x99_ ;

reg signed [19:0]x109_;

reg signed [19:0]x112_;

reg signed [19:0]x105_;

reg signed [19:0]x72 ;

reg signed [19:0]x157 ;

reg signed [19:0]x256 ;

reg signed [19:0]x365 ;

reg signed [19:0]x482 ;

reg signed [19:0]x599 ;

reg signed [19:0]x712 ;

reg signed [19:0]x814 ;

reg signed [19:0]x901 ;

reg signed [19:0]x966 ;

reg signed [19:0]x1007;

reg signed [19:0]x1021;

always @(posedge clk or negedge reset)

if (reset == 1’b0)

begin

x6 <=20’b0;

x5 <=20’b0;

x3 <=20’b0;

x1_ <=20’b0;

x9_ <=20’b0;

x19_ <=20’b0;

x33_ <=20’b0;

x49_ <=20’b0;

x66_ <=20’b0;

x84_ <=20’b0;

x99_ <=20’b0;

x109_ <=20’b0;

x112_ <=20’b0;

x105_ <=20’b0;

x72 <=20’b0;

x157 <=20’b0;

x256 <=20’b0;

x365 <=20’b0;

x482 <=20’b0;

x599 <=20’b0;

x712 <=20’b0;

x814 <=20’b0;

x901 <=20’b0;

x966 <=20’b0;

x1007 <=20’b0;

x1021 <=20’b0;

end

else

begin

x6 <= filter_in * coeff6 ;

x5 <= filter_in * coeff5 ;

x3 <= filter_in * coeff3 ;

x1_ <= filter_in * coeff1_ ;

x9_ <= filter_in * coeff9_ ;

x19_ <= filter_in * coeff19_ ;

x33_ <= filter_in * coeff33_ ;

x49_ <= filter_in * coeff49_ ;

x66_ <= filter_in * coeff66_ ;

x84_ <= filter_in * coeff84_ ;

x99_ <= filter_in * coeff99_ ;

x109_ <= filter_in * coeff109_;

x112_ <= filter_in * coeff112_;

x105_ <= filter_in * coeff105_;

x72 <= filter_in * coeff72 ;

x157 <= filter_in * coeff157 ;

x256 <= filter_in * coeff256 ;

x365 <= filter_in * coeff365 ;

x482 <= filter_in * coeff482 ;

x599 <= filter_in * coeff599 ;

x712 <= filter_in * coeff712 ;

x814 <= filter_in * coeff814 ;

x901 <= filter_in * coeff901 ;

x966 <= filter_in * coeff966 ;

x1007 <= filter_in * coeff1007;

x1021 <= filter_in * coeff1021;

end

always @(posedge clk or negedge reset)

if (reset == 1’b0)

begin

r0 <= 20’b0;

r1 <= 20’b0;

r2 <= 20’b0;

r3 <= 20’b0;

r4 <= 20’b0;

r5 <= 20’b0;

r6 <= 20’b0;

r7 <= 20’b0;

r8 <= 20’b0;

r9 <= 20’b0;

r10 <= 20’b0;

r11 <= 20’b0;

r12 <= 20’b0;

r13 <= 20’b0;

r14 <= 20’b0;

r15 <= 20’b0;

r16 <= 20’b0;

r17 <= 20’b0;

r18 <= 20’b0;

r19 <= 20’b0;

r20 <= 20’b0;

r21 <= 20’b0;

r22 <= 20’b0;

r23 <= 20’b0;

r24 <= 20’b0;

r25 <= 20’b0;

r26 <= 20’b0;

r27 <= 20’b0;

r28 <= 20’b0;

r29 <= 20’b0;

r30 <= 20’b0;

r31 <= 20’b0;

r32 <= 20’b0;

r33 <= 20’b0;

r34 <= 20’b0;

r35 <= 20’b0;

r36 <= 20’b0;

r37 <= 20’b0;

r38 <= 20’b0;

r39 <= 20’b0;

r40 <= 20’b0;

r41 <= 20’b0;

r42 <= 20’b0;

r43 <= 20’b0;

r44 <= 20’b0;

r45 <= 20’b0;

r46 <= 20’b0;

r47 <= 20’b0;

r48 <= 20’b0;

r49 <= 20’b0;

r50 <= 20’b0;

r51 <= 20’b0;

r52 <= 20’b0;

r53 <= 20’b0;

r54 <= 20’b0;

r55 <= 20’b0;

r56 <= 20’b0;

r57 <= 20’b0;

r58 <= 20’b0;

r59 <= 20’b0;

r60 <= 20’b0;

end

else

begin

r0 <= x6 ;

r1 <= r0 + x5 ;

r2 <= r1 + x6 ;

r3 <= r2 + x5 ;

r4 <= r3 + x3 ;

r5 <= r4 + x1_ ;

r6 <= r5 + x9_ ;

r7 <= r6 + x19_ ;

r8 <= r7 + x33_ ;

r9 <= r8 + x49_ ;

r10 <= r9 + x66_ ;

r11 <= r10 + x84_ ;

r12 <= r11 + x99_ ;

r13 <= r12 + x109_;

r14 <= r13 + x112_;

r15 <= r14 + x105_;

r16 <= r15 + x84_ ;

r17 <= r16 + x49_ ;

r18 <= r17 + x3 ;

r19 <= r18 + x72 ;

r20 <= r19 + x157 ;

r21 <= r20 + x256 ;

r22 <= r21 + x365 ;

r23 <= r22 + x482 ;

r24 <= r23 + x599 ;

r25 <= r24 + x712 ;

r26 <= r25 + x814 ;

r27 <= r26 + x901 ;

r28 <= r27 + x966 ;

r29 <= r28 + x1007;

r30 <= r29 + x1021;

r31 <= r30 + x1007 ;

r32 <= r31 + x966 ;

r33 <= r32 + x901 ;

r34 <= r33 + x814 ;

r35 <= r34 + x712 ;

r36 <= r35 + x599 ;

r37 <= r36 + x482 ;

r38 <= r37 + x365 ;

r39 <= r38 + x256 ;

r40 <= r39 + x157 ;

r41 <= r40 + x72 ;

r42 <= r41 + x3 ;

r43 <= r42 + x49_ ;

r44 <= r43 + x84_ ;

r45 <= r44 + x105_;

r46 <= r45 + x112_;

r47 <= r46 + x109_;

r48 <= r47 + x99_;

r49 <= r48 + x84_;

r50 <= r49 + x66_;

r51 <= r50 + x49_;

r52 <= r51 + x33_;

r53 <= r52 + x19_;

r54 <= r53 + x9_;

r55 <= r54 + x1_;

r56 <= r55 + x3;

r57 <= r56 + x5;

r58 <= r57 + x6;

r59 <= r58 + x5;

r60 <= r59 + x6;

end

assign filter_out = r60;

endmodule

脚本文件:

sh date

set company {EE252}

set designer {Tutorial}

set my_lib_path “/home/smic180/digital/sc/synopsys/ /home/smic180/digital/io/synopsys/ /home/smic180/digital/sc/symbols/synopsys/”

set search_path "$search_path $my_lib_path "

set target_library “typical.db”

set synthetic_library “dw_foundation.sldb”

set link_library “* typical.db * SP018N_V1p0_typ.db $synthetic_library”

set symbol_library “smic.sdb”

#void warning Info #

suppress_message VER-130

suppress_message VER-129

suppress_message VER-318

suppress_message ELAB-311

suppress_message VER-936

#suppress_message TIM-134

#suppress_message DDB-24

#suppress_message VO-4

#suppress_message VO-11

#read&link&Check design#

#read_file -format verilog ./fir.v

read_file -format verilog {/home/IC/Desktop/fir/fir/fir.v}

current_design fir

link

#Loading db file ‘/opt/Synopsys/Synplify2015/libraries/syn/generic.sdb’

define IO port name

set clk [get_ports clk]

set reset [get_ports reset]

set general_inputs [list filter_in]

set outputs [get_ports filter_out]

set verilogout_no_tri true;

set_fix_multiple_port_nets -all -buffer_constants;

set_constraints

#1 set constraints for clock signals

create_clock -n clock $clk -period 20 -waveform {0 10}

set_dont_touch_network [get_clocks clock]

set_drive 0 $clk

set_ideal_network [get_ports clk]

#2 set constraints for reset signals

set_dont_touch_network $reset

set_drive 0 $reset

set_ideal_network [get_ports reset]

#3 set input delay

set_input_delay -clock clock 12 $general_inputs

#4 set output delay

set_output_delay -clock clock 12 $outputs

#5 set design rule constraints

#set_max_fanout 1743 $general_inputs

#set_max_transition 0.5 [get_designs “fir”]

#6 set area constraint

#set_max_area 0

compile_design

compile -map_effort medium

write *.db and *.v

#write -f db -hier -output ./fir.db fir

#write -f verilog -hier -output ./firnetlist.v fir

write_sdf -version 1.0 ./fir.sdf

write_sdc fir.sdc

write -f ddc -hierarchy -output fir.ddc

write -hierarchy -format verilog -output firnetlist.v

#1

uplevel #0 { report_area }

#2

uplevel #0 { report_constraint -all_violators -significant_digits 2 -nosplit }

#3

uplevel #0 { report_timing -path full -delay max -nworst 1 -max_paths 1 -significant_digits 2 -sort_by group }

#4

uplevel #0 { report_power -analysis_effort low }

sh date

怎么运行呢?

首先运行DC软件命令模式,在linux下,命令是dc_shell

运行完,命令路径进入de_shell,输入source fir.scr,就是你之前的脚本文件如图:

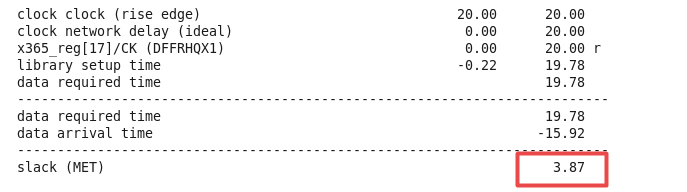

得到结果:

面积

时间

功耗

同时得到一些文件,会在我们之后的工作用到,firnetlist是网表文件

6430

6430

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?