DC的所有理论知识已经简单的概述完了,包括 DC简介概念流程、逻辑推断、DC脚本命令。最后给出DC的两个示例。

下面是大的目录:

一、示例1-同步设计-fifo1

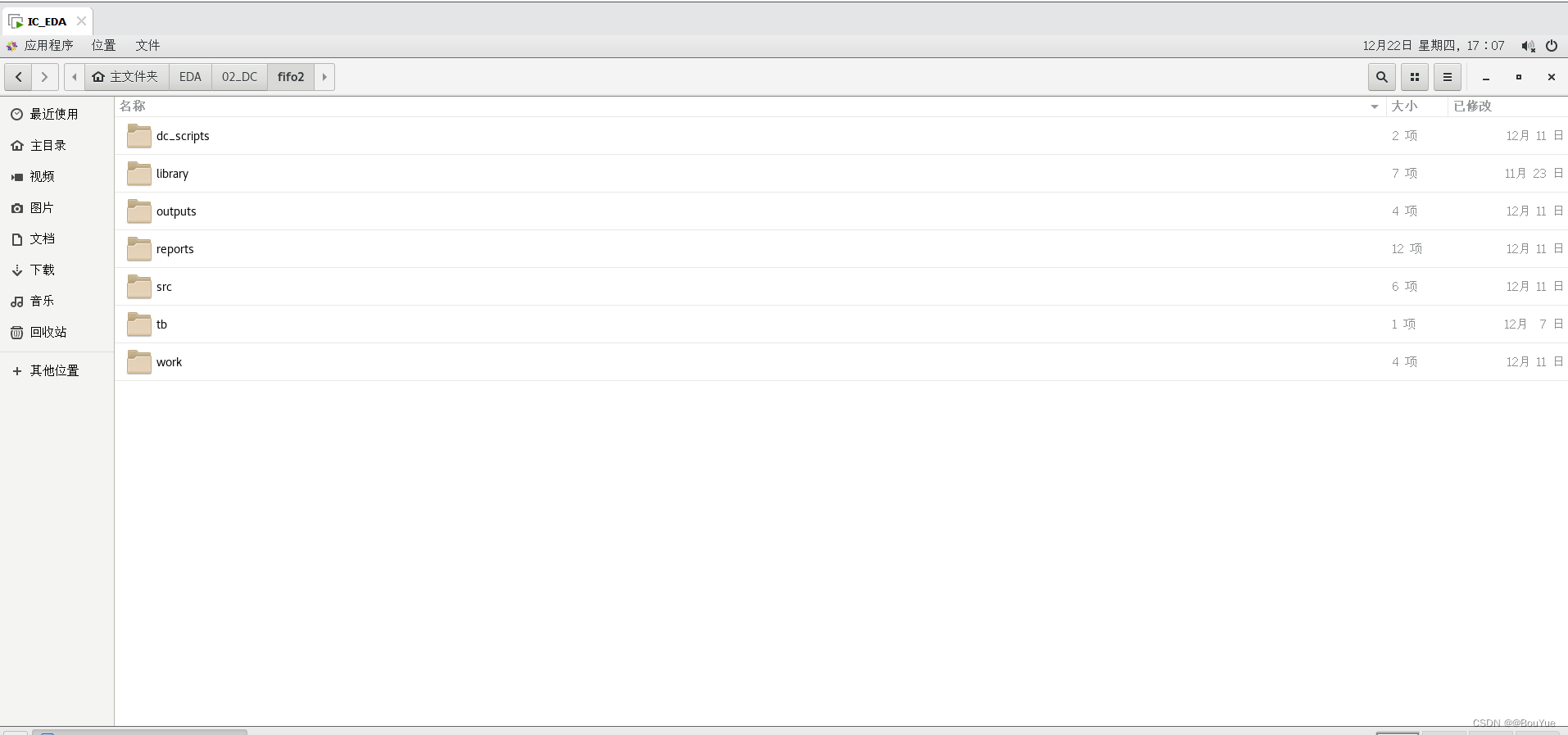

下面是创建的工作目录:

其中dc_scripts存放脚本;library存放库文件;output存放输出文件;reports存放检查设计的报告;src存放设计.v文件;tb存放测试代码;work工作目录。

其中dc_scripts存放脚本;library存放库文件;output存放输出文件;reports存放检查设计的报告;src存放设计.v文件;tb存放测试代码;work工作目录。

设计代码:详情看链接: link

module VR_FIFO (//外部Valid_Ready输入输出端口

input clk,

input rst_n,

input [7:0] data_in,

input in_val,

input out_rdy,

output in_rdy,

output out_val,

output reg [7:0] data_out

);

//内部FIFO的输入输出端口,以下三组变量是FIFP的输入输出端口,故而要在内部定义。

reg wr_en ;

reg rd_en ; //FIFO 读写使能

wire empty ;

wire full ; //FIFO 空满信号

reg [4:0] fifo_cnt ; //FIFO 计数器

//FIFO内部定义

reg [7:0] fifo_buffer[15 : 0]; //用二维数组实现RAM

reg [3:0] wr_addr; //写地址

reg [3:0] rd_addr; //读地址

//写使能,当前reg准备好接收且输入数据有效,即可 使能 写信号

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

wr_en <= 1'b0;

else if(in_val && in_rdy)

wr_en <= 1'b1;

else

wr_en <= 1'b0;

end

//读使能,当后reg准备好接收且当前reg输出数据有效,即可 使能 读信号

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

rd_en <= 1'b0;

else if(out_val && out_rdy)

rd_en <= 1'b1;

else

rd_en <= 1'b0;

end

//向FIFO写数据操作,并且更新写地址

always @ (posedge clk or negedge rst_n)

begin

if (!rst_n)

wr_addr <= 0;

else if (!full && wr_en)

begin //写使能有效且没有写满

wr_addr <= wr_addr + 1'd1;

fifo_buffer[wr_addr] <= data_in;

end

end

//从FIFO读数据操作,并且更新读地址

always @ (posedge clk or negedge rst_n)

begin

if (!rst_n)

rd_addr <= 0;

else if (!empty && rd_en)begin //读使能有效且没有读空

rd_addr <= rd_addr + 1'd1;

data_out <= fifo_buffer[rd_addr];

end

end

//更新计数器,来判断空满信号

always @ (posedge clk or negedge rst_n)

begin

if (!rst_n)

fifo_cnt <= 0;

else begin

case({wr_en,rd_en})

2'b00: fifo_cnt <= fifo_cnt; //不读不写

2'b01:

begin //仅仅读

if(fifo_cnt != 0) //fifo没有被读空

fifo_cnt <= fifo_cnt - 1'b1; //fifo个数-1

end

2'b10: //仅仅写

begin

if(fifo_cnt != 5'd16) //fifo没有被写满

fifo_cnt <= fifo_cnt + 1'b1; //fifo个数+1

end

2'b11: fifo_cnt <= fifo_cnt; //读写同时

default:;

endcase

end

end

//依据计数器状态更新指示信号

//依据不同阈值还可以设计半空、半满 、几乎空、几乎满

assign full = (fifo_cnt == 5'd16) ? 1'b1 : 1'b0; //满信号

assign empty = (fifo_cnt == 0) ? 1'b1 : 1'b0; //空信号

assign in_rdy = (!full);

assign out_val = (!empty);

endmodule

下面看脚本:

#############################SET_UP##################################

#1_set_search_path

set search_path "/home/ICer/EDA/02_DC/fifo1/library"

# set search_path " . \

/home/ICer/EDA/02_DC/fifo1/library \

/home/synopsys/syn/O-2018.06-SP1/libraries/syn \

$search_path "

set access_internal_pins true

#2_set_source_folder

set src_path "../src/"

#3_set_top_file

set top_level VR_FIFO

#4_set_output_path

set report_path "../reports";#输出报告

set output_path "../outputs";#输出文件

set sh_output_log_file "output.log"

#5_read_verilog_code

read_verilog $src_path/VR_FIFO.v

#6_set_main_design

current_design $top_level

link ; #工艺库链接

uniquify

#7_set_design_name

set design_name [get_object_name [current_design]]

#8_set_library_link

set_app_var link_library /$search_path/smic18_ss.db

set_app_var target_library /$search_path/smic18_ss.db

##############WORK_CONDITIONS##################################

#1_set_operate_conditions

set_operating_conditions worst

#2_set_wire_load_model

set_wire_load_model -name reference_area_20000

#3_set_load_mode

set_wire_load_mode segmented

#4_set_input_drive

set_driving_cell -library smic18_ss -lib_cell INVHD2XSPG [all_inputs] ;#else_input

set_drive [expr [drive_of smic18_ss/INVHD1X/Z]*8] [get_ports clk] ;#clk_&_rst_n

#################################################################################

# 11_1_input_drive_from_3_to_1 #

# set_drive [drive_of smic18_ss/INVHD1X/Z] [list clk rst_n] #

# set_drive [expr [drive_of smic18_ss/INVHD1X/Z]*8] [get_ports clk] #

# set_drive 0 [list clk rst_n] #

# #

# 11_2_input_driving_cell #

# set_driving_cell -library smic18_ss -lib_cell INVHD2XSPG [all_inputs] #

#tips: one_wrimnig #

# Design rule attributes from the driving cell will be set on the port. #

#################################################################################

#5_set_output_load

set LOAD_OF_A [load_of smic18_ss/NAND2HD2X/A]

set_load [expr $LOAD_OF_A*10] [all_outputs]

#6_set_rule_constraints

#6_1_transition_time

set_max_transition 1.0 [all_designs]

#6_2_fanout_load

set_max_fanout 8 [get_designs VR_FIFO]

#6_3_max_capacitance

set LOAD_OF_A [load_of smic18_ss/NAND2HD2X/A]

set_max_capacitance [expr $LOAD_OF_A*10] [all_designs]

###########################timing_constraint####################################

#1_define_clock

create_clock -name clk -period 10 [get_ports clk]

#2_source_latency&source_to_clock

set_clock_latency -source 3 [get_clocks clk]

#3_network_latency&clock_to_reg

set_clock_latency 1 [get_clocks clk]

#4_clock_uncertainty

set_clock_uncertainty -setup 1.5 [get_ports clk]

#5_clock_transtin

set_clock_transition 0.3 [get_clocks clk]

#6_dont_touch

set_dont_touch_network [get_clocks clk]

#1_input_delay

set_input_delay -max 5.5 -clock [get_clocks clk] [get_ports data_in]

set_input_delay -max 5.5 -clock [get_clocks clk] [get_ports in_val ]

set_input_delay -max 5.5 -clock [get_clocks clk] [get_ports out_rdy]

#2_output_delay

set_output_delay -max 6.6 -clock [get_clocks clk] [all_outputs]

###########################area_constraint####################################

# 对于时序优先的设计,通常设置其最大面积为0,

# 意指在时序收敛的前提下尽可能的优化面积.

set_max_area 0.0

#11、编译运行

compile

#12、输出文件

write_sdf -version 2.1 ./$output_path/${design_name}_VR_FIFO.sdf; #时序描述

write -f ddc -hier -output ./$output_path/${design_name}_VR_FIFO.ddc; #ddc文件

write -f verilog -hier -output ./$output_path/${design_name}_VR_FIFO.v ; #网表文件

write_sdc ./$output_path/${design_name}_VR_FIFO.sdc; #约束文件

#13、输出报告

report_constraint -all_violators -verbose > ./$report_path/constraint.rpt

report_qor > ./$report_path/qor.rpt

report_power > ./$report_path/power.rpt

report_area > ./$report_path/area.rpt

report_cell > ./$report_path/cell.rpt

report_clock > ./$report_path/clk.rpt

report_hierarchy > ./$report_path/hierarchy.rpt

report_design > ./$report_path/design.rpt

report_reference > ./$report_path/reference.rpt

report_timing > ./$report_path/timing.rpt

#14、设计检查

check_design > ./$report_path/check_design_post_compile.rpt

check_timing > ./$report_path/check_timing_post_compile.rpt

之前的内容把脚本如何写介绍了,不懂得可以查看前面章节。

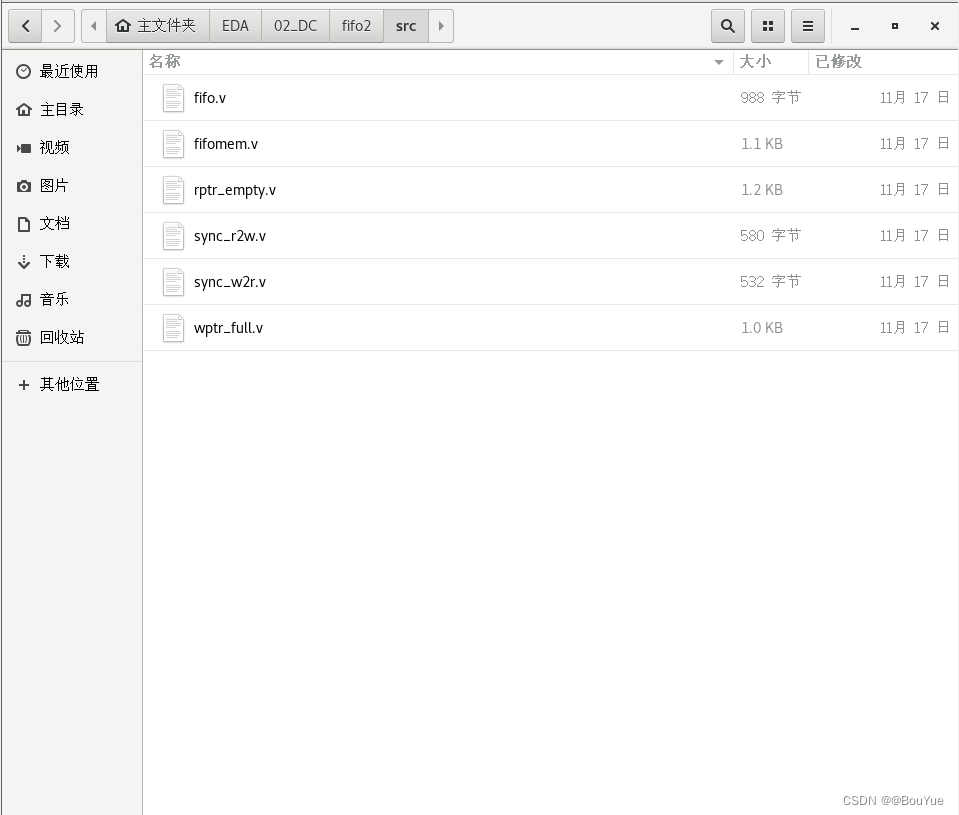

二、示例2-异步设计-fifo2

工作目录一致。设计文件如下:

工作目录一致。设计文件如下:

是一个异步fifo。代码太多,就不单独占出来了,有需要私信我发。

是一个异步fifo。代码太多,就不单独占出来了,有需要私信我发。

同样看脚本:

#1_set_search_path

set search_path "/home/ICer/EDA/02_DC/fifo1/library"

# set search_path " . \

/home/ICer/EDA/02_DC/fifo1/library \

/home/synopsys/syn/O-2018.06-SP1/libraries/syn \

$search_path "

set access_internal_pins true

#2_set_source_folder

set src_path "../src/"

#3_set_top_file

set top_level fifo

#4_set_output_path

set report_path "../reports";#输出报告

set output_path "../outputs";#输出文件

#5_read_verilog_code

read_verilog $src_path/fifo.v

read_verilog $src_path/fifomem.v

read_verilog $src_path/rptr_empty.v

read_verilog $src_path/sync_r2w.v

read_verilog $src_path/sync_w2r.v

read_verilog $src_path/wptr_full.v

#6_set_main_design

current_design $top_level

link ; #工艺库链接

uniquify

#7_set_design_name

set design_name [get_object_name [current_design]]

#8_set_library_link

set_app_var link_library /$search_path/smic18_ss.db

set_app_var target_library /$search_path/smic18_ss.db

##############WORK_CONDITIONS##################################

#1_set_operate_conditions

set_operating_conditions worst

#2_set_wire_load_model

set_wire_load_model -name reference_area_20000

#3_set_load_mode

set_wire_load_mode segmented

#4_set_input_drive

set_drive [expr [drive_of smic18_ss/INVHD1X/Z]*8] [list wclk wrst wr_en]

set_drive [expr [drive_of smic18_ss/INVHD1X/Z]*8] [list rclk rrst rd_en]

set_driving_cell -library smic18_ss -lib_cell INVHD2XSPG [get_ports wdata]

#################################################################################

# 11_1_input_drive_from_3_to_1 #

# set_drive [drive_of smic18_ss/INVHD1X/Z] [list clk rst_n] #

# set_drive [expr [drive_of smic18_ss/INVHD1X/Z]*8] [get_ports clk] #

# set_drive 0 [list clk rst_n] #

# #

# 11_2_input_driving_cell #

# set_driving_cell -library smic18_ss -lib_cell INVHD2XSPG [all_inputs] #

#tips: one_wrimnig #

# Design rule attributes from the driving cell will be set on the port. #

#################################################################################

#5_set_output_load

set LOAD_OF_A [load_of smic18_ss/NAND2HD2X/A]

set_load [expr $LOAD_OF_A*10] [all_outputs]

#6_set_rule_constraints

#6_1_transition_time

set_max_transition 1.0 [all_designs]

#6_2_fanout_load

set_max_fanout 8 [get_designs fifo]

#6_3_max_capacitance

set LOAD_OF_A [load_of smic18_ss/NAND2HD2X/A]

set_max_capacitance [expr $LOAD_OF_A*10] [all_designs]

#1_define_clock

create_clock -name wclk -period 10 [get_ports wclk]

create_clock -name rclk -period 20 [get_ports rclk]

#2_source_latency&source_to_clock

set_clock_latency -source 3 [get_clocks wclk]

set_clock_larency -source 3 [get_clocks rclk]

#4_clock_uncertainty

set_clock_uncertainty -setup 1.5 [list wclk rclk]

#5_clock_transtin

set_clock_transition 0.3 [get_clocks rclk]

set_clock_transition 0.3 [get_clocks wclk]

#6_dont_touch

set_dont_touch_network [list wclk rclk]

#1_input_delay

set_input_delay -max 5.5 -clock [get_clocks wclk] [get_ports wdata]

#2_output_delay

set_output_delay -max 6.6 -clock [get_clocks rclk] [get_ports rdata]

set_output_delay -max 3.3 -clock [get_clocks wclk] [get_ports wfull]

set_output_delay -max 6.6 -clock [get_clocks rclk] [get_ports rempty]

#3_false_paths

set_false_path -from [get_clocks wclk] -to [get_clocks rclk]

set_false_path -from [get_clocks rclk] -to [get_clocks wclk]

###########################area_constraint####################################

# 对于时序优先的设计,通常设置其最大面积为0,

# 意指在时序收敛的前提下尽可能的优化面积.

set_max_area 0.0

#11、编译运行

compile

#12、输出文件

write_sdf -version 2.1 ./$output_path/${design_name}_VR_FIFO.sdf; #时序描述

write -f ddc -hier -output ./$output_path/${design_name}_VR_FIFO.ddc; #ddc文件

write -f verilog -hier -output ./$output_path/${design_name}_VR_FIFO.v ; #网表文件

write_sdc ./$output_path/${design_name}_VR_FIFO.sdc; #约束文件

#13、输出报告

report_constraint -all_violators -verbose > ./$report_path/constraint.rpt

report_qor > ./$report_path/qor.rpt

report_power > ./$report_path/power.rpt

report_area > ./$report_path/area.rpt

report_cell > ./$report_path/cell.rpt

report_clock > ./$report_path/clk.rpt

report_hierarchy > ./$report_path/hierarchy.rpt

report_design > ./$report_path/design.rpt

report_reference > ./$report_path/reference.rpt

report_timing > ./$report_path/timing.rpt

#14、设计检查

check_design > ./$report_path/check_design_post_compile.rpt

check_timing > ./$report_path/check_timing_post_compile.rpt

ok,这两个例子是我学习的过程中拿来练手的脚本都能用,具体怎么用下面看,举个例子。

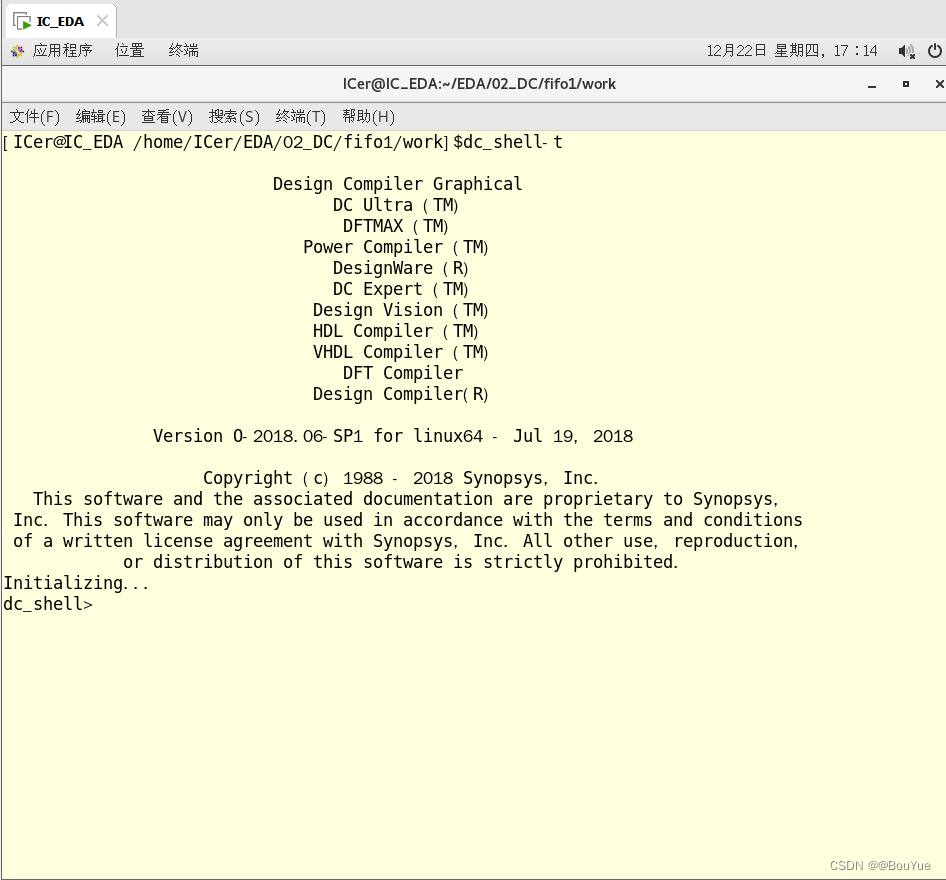

三、具体操作,fifo1为例。

1、work目录下打开终端。

2、输入dc_shell-t,打开DC。

3、输入命令:

dc_shell> source -e -v ../dc_scripts/test_dc.tcl

4、执行脚本,出结果。

3690

3690

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?