流水灯

module led(

input sys_clk,

input sys_rst_n,

output [3:0]led_out,

output led_flag

);

reg [6:0]cnt; //cnt触发器的位数为log_2 max_cnt;

reg [3:0]q;

parameter max_cnt = 99;

always @(posedge sys_clk or negedge sys_rst_n ) begin

if(!sys_rst_n)begin

q <= 4’b1110;end

else if(cnt == max_cnt)begin

q <= {q[2:0],q[3]};

end

else begin

q <= q;end

end

always @(posedge sys_clk or negedge sys_rst_n) begin

if(!sys_rst_n)begin

cnt <= 25’d0;end

else if(cnt == max_cnt)begin

cnt<= 25’d0;end

else begin

cnt <= cnt + 1’b1;

end

end

assign led_out = q;

assign led_flag = (cnt==max_cnt)? 1’b1:1’b0;

endmodule

testbench

include "led.v" timescale 1ns / 1ps

module tb_led;

// led Parameters

parameter PERIOD = 20;

// led Inputs

reg sys_clk = 0 ;

reg sys_rst_n = 0 ;

// led Outputs

wire [3:0] led_out ;

initial

begin

forever #(PERIOD/2) sys_clk=~sys_clk;

end

initial

begin

#(PERIOD*2) sys_rst_n = 1;

end

led u_led (

.sys_clk ( sys_clk ),

.sys_rst_n ( sys_rst_n ),

.led_out ( led_out [3:0] ),

.led_flag ( led_flag )

);

initial

begin

$dumpfile(“led.vcd”);

$dumpvars;

#10000

$finish;

end

endmodule

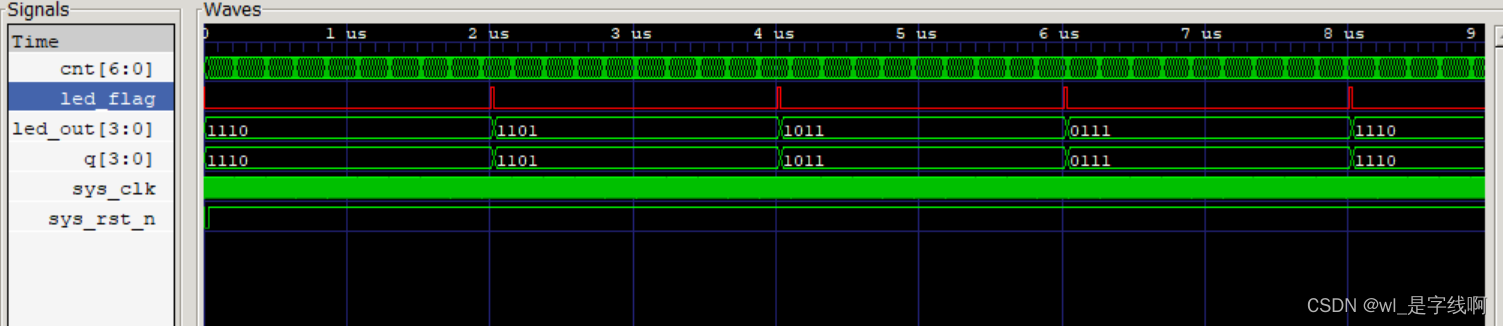

仿真波形

7350

7350

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?