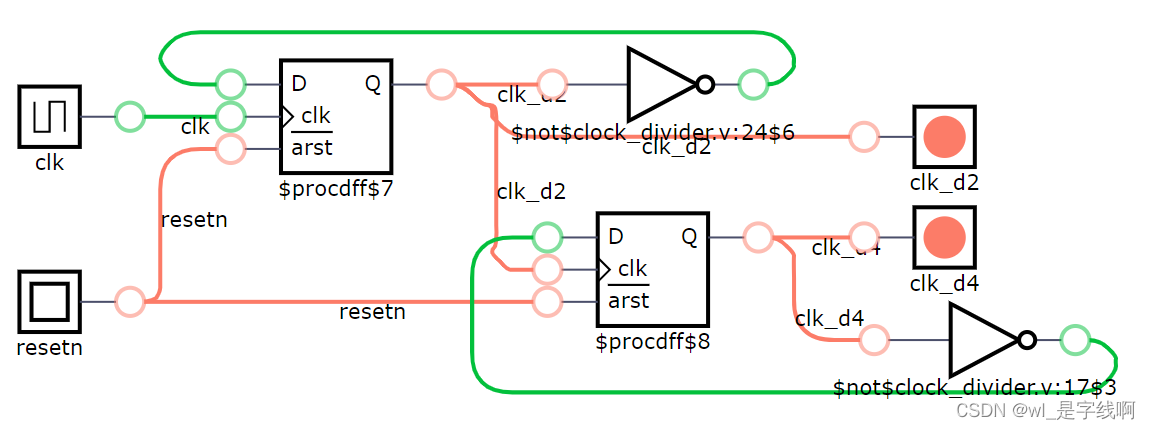

verilog设计

module divider(

input wire clk,

input resetn,

output reg clk_d2,

output reg clk_d4

);

always@(posedge clk_d2 or negedge resetn)begin //4分频电路

if(~resetn)

clk_d4 <= 0;

else

clk_d4 <= ~clk_d4;

end

always@(posedge clk or negedge resetn)begin //2分频

if(~resetn)

clk_d2 <= 0;

else

clk_d2 <= ~clk_d2;

end

endmodule

testbench

include "clock_divider.v" timescale 1ns / 1ps

module tb_divider;

// divider Parameters

parameter PERIOD = 10;

// divider Inputs

reg clk = 0 ;

reg resetn = 0 ;

// divider Outputs

wire clk_d2 ;

wire clk_d4 ;

initial

begin

forever #(PERIOD/2) clk=~clk;

end

initial

begin

#(PERIOD*2) resetn = 1;

end

divider u_divider (

.clk ( clk ),

.resetn ( resetn ),

.clk_d2 ( clk_d2 ),

.clk_d4 ( clk_d4 )

);

initial

begin

$dumpfile(“di.vcd”);

$dumpvars;

#1000

$finish;

end

endmodule

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?