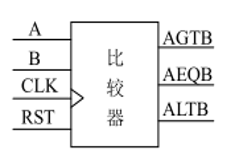

比较器

原理

注:这里的比较器引入了时钟,更丰富。

引脚说明:

A、B:输入信号,位宽为2

CLK:时钟输入

RST:为0时比较器正常工作,为1时复位

AGTB :当 A>B 时,其值为 1,否则为 0

AEQB :当 A=B 时,其值为 1,否则为 0

ALTB : 当 A<B 时,其值为 1,否则为 0

代码

module lab(

input [1:0]A,B,

input clk,

input RST,

output reg AGTB,AEQB,ALTB=0

);

always@(posedge clk or negedge RST )

begin

if(~RST)

begin

AGTB<=0; //时序逻辑用阻塞赋值,always块中被赋值的要为reg型

AEQB<=0;

ALTB<=0;

end

else if(A>B)

begin

AGTB<=1;

AEQB<=0;

ALTB<=0;

end

else if(A==B)

begin

AGTB<=0;

AEQB<=1;

ALTB<=0;

end

else

begin

AGTB<=0;

AEQB<=0;

ALTB<=1;

end

end

endmodule

仿真

module Test();

//input

reg [1:0]A,B;

reg clk;

reg RST;

//output

wire AGTB,AEQB,ALTB;

initial

begin

clk=0;

RST=1;

A=0;

B=0;

#120

A=2'b00;

B=2'b11;

#100

A=2'b01;

B=2'b01;

#100

A=2'b10;

B=2'b01;

#100

RST=0;

#100

RST=1;

A=2'b11;

B=2'b10;

end

always #50 clk=~clk;

lab test(

.A(A),

.B(B),

.clk(clk),

.RST(RST),

.AGTB(AGTB),

.AEQB(AEQB),

.ALTB(ALTB)

);

endmodule

波形图

全加器

真值表

全加器其实就是考虑到进位的加法器。Cin为前进的进位输入,Cout为输出给后一级的进位。Sum为和。

代码

module lab(

input A,B,Cin,

output reg Cout,Sum

);

always @(A or B or Cin)

begin

{Cout,Sum}=A+B+Cin;

end

endmodule

仿真

module Test();

//input

reg A,B,Cin;

//output

wire Cout,Sum;

initial

begin

A=0;

B=0;

Cin=0;

end

always #20 Cin=~Cin;

always #40 B=~B;

always #80 A=~A;

lab test(

.A(A),

.B(B),

.Cin(Cin),

.Cout(Cout),

.Sum(Sum)

);

endmodule

波形图

RTL图:

结束语

目前写的示例,应该是最最基础的,大部分为简单组合逻辑设计。下一阶段计划开始学习时序逻辑,包括D触发器、计数器、任意整数分频器、状态机等等。虽然CSDN上学习硬件编程的人好像不多,我也想把这个过程记录下来,每天进步一小点!

4323

4323

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?