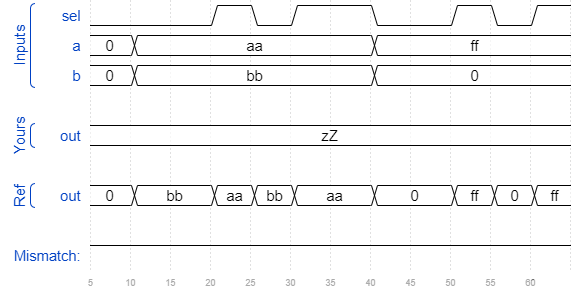

Bugs mux2

This 8-bit wide 2-to-1 multiplexer doesn't work. Fix the bug(s).

module top_module ( input sel, input [7:0] a, input [7:0] b, output out ); assign out = (~sel & a) | (sel & b); endmodule

8位数据选择器,sel=1输出a,sel=0输出b

该题两个错误,首先是输出out也应为8位,不然下面逻辑错误改过来out也只是会输出zZ

第二个错误为逻辑错误,&按位操作,需要将sel扩展到8位才可:

assign out =( {8{~sel}} & a ) | ( {8{sel}} & b );其中:& 不可替换为&&,因为这样out的值只会是0或1:

assign out = (~sel && a) | (sel && b);逻辑错误也可通过三目运算符进行判断:

assign out = sel ? a : b;Bugs nand3

This three-input NAND gate doesn't work. Fix the bug(s).

You must use the provided 5-input AND gate:

module andgate ( output out, input a, input b, input c, input d, input e );module top_module (input a, input b, input c, output out);// andgate inst1 ( a, b, c, out ); endmodule

需要用一个5输入的与门实现三输入的与非门。首先要补全输入,之前空置的d和e输入可用1'b1代替,再对模块的输出结果进行取反。需要注意的是给定模块的输出在最前面而不是最后一位参数。

module top_module (input a, input b, input c, output out);//

wire temp;

andgate inst1 (temp, a, b, c,1'b1,1'b1 );

assign out=~temp;

endmoduleBugs mux4

This 4-to-1 multiplexer doesn't work. Fix the bug(s).

You are provided with a bug-free 2-to-1 multiplexer:

module mux2 ( input sel, input [7:0] a, input [7:0] b, output [7:0] out );module top_module ( input [1:0] sel, input [7:0] a, input [7:0] b, input [7:0] c, input [7:0] d, output [7:0] out ); // wire mux0, mux1; mux2 mux0 ( sel[0], a, b, mux0 ); mux2 mux1 ( sel[1], c, d, mux1 ); mux2 mux2 ( sel[1], mux0, mux1, out ); endmodule

使用给定的2选1选择器实现4选1,经过测试后发现,2选1的输出为sel=0输出a,sel=1输出b

而4选1的sel与输出的对应关系为

| 0 | 1 | |

| 0 | a | b |

| 1 | c | d |

所以应选出有区分的组合ac,bd或ab,cd并进行后续判断

module top_module (

input [1:0] sel,

input [7:0] a,

input [7:0] b,

input [7:0] c,

input [7:0] d,

output [7:0] out ); //

wire [7:0]mux0, mux1;

mux2 a1 ( sel[1], a, c, mux0 );

mux2 a2 ( sel[1], b, d, mux1 );

mux2 a3 ( sel[0], mux0, mux1, out );

endmoduleBugs add-subz

The following adder-subtractor with zero flag doesn't work. Fix the bug(s).

module top_module ( input do_sub, input [7:0] a, input [7:0] b, output reg [7:0] out, output reg result_is_zero );// always @(*) begin case (do_sub) 0: out = a+b; 1: out = a-b; endcase if (~out) result_is_zero = 1; end endmodule

有两处错误,~out 取反也不能说名out是否为全0,可以通过如下方法:

(~(out&&1'b1))

(out==8'd0)此外,if语句的判断不满足完备性,应配else

// synthesis verilog_input_version verilog_2001

module top_module (

input do_sub,

input [7:0] a,

input [7:0] b,

output reg [7:0] out,

output reg result_is_zero

);//

always @(*) begin

case (do_sub)

0: out = a+b;

1: out = a-b;

endcase

if (~(out&&1'b1))

result_is_zero = 1;

else

result_is_zero=0;

end

endmoduleBugs case

This combinational circuit is supposed to recognize 8-bit keyboard scancodes for keys 0 through 9. It should indicate whether one of the 10 cases were recognized (valid), and if so, which key was detected. Fix the bug(s).

module top_module ( input [7:0] code, output reg [3:0] out, output reg valid=1 );// always @(*) case (code) 8'h45: out = 0; 8'h16: out = 1; 8'h1e: out = 2; 8'd26: out = 3; 8'h25: out = 4; 8'h2e: out = 5; 8'h36: out = 6; 8'h3d: out = 7; 8'h3e: out = 8; 6'h46: out = 9; default: valid = 0; endcase endmodule

具体思路:

“这道题的问题在于输出不能直接给初值,如果直接在输出给值无法传递和保持,若改成reg valid=1’b1,则会报错,因为输出不能重新被定义或声明,写成output reg valid=1’b1;没有语法错误,若写成output valid,reg valid=1’b1;则会出现上述问题,上述代码测试成功

————————————————

原文链接:https://blog.csdn.net/qq_42043804/article/details/112349367”

此外,原代码中out=3时code是8'd26,out=9时code是6'h46,其它都是8位16进制,这两个也太奇怪了,都改成8'h之后成功运行

module top_module (

input [7:0] code,

output reg [3:0] out,

output reg valid=1 );//

always @(*)begin

valid = 1;

case (code)

8'h45: out = 0;

8'h16: out = 1;

8'h1e: out = 2;

8'h26: out = 3;

8'h25: out = 4;

8'h2e: out = 5;

8'h36: out = 6;

8'h3d: out = 7;

8'h3e: out = 8;

8'h46: out = 9;

default: begin

valid = 0;

out=0;

end

endcase

end

endmodule

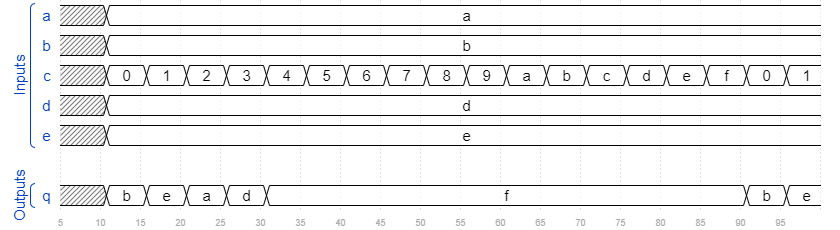

Sim/circuit5

输出在abde里面取, 根据c值的不同而不同,可以用case解决

module top_module (

input [3:0] a,

input [3:0] b,

input [3:0] c,

input [3:0] d,

input [3:0] e,

output [3:0] q );

always@(*) begin

case(c)

3'd0:q=b;

3'd1:q=e;

3'd2:q=a;

3'd3:q=d;

default:q=4'hf;

endcase

end

endmodule

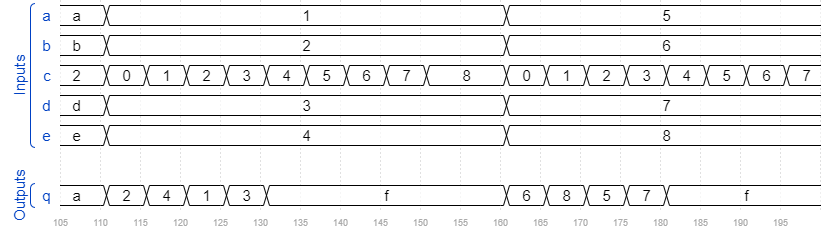

Sim/circuit6

波形图列出了输入的全部情况,所以可以用case解决,跟circuit5一样,不过出题的人真的是想这么做嘛?

module top_module (

input [2:0] a,

output [15:0] q );

always@(*)begin

case(a)

3'd0 : q <= 16'h1232;

3'd1 : q <= 16'haee0;

3'd2 : q <= 16'h27d4;

3'd3 : q <= 16'h5a0e;

3'd4 : q <= 16'h2066;

3'd5 : q <= 16'h64ce;

3'd6 : q <= 16'hc526;

3'd7 : q <= 16'h2f19;

endcase

end

endmodule

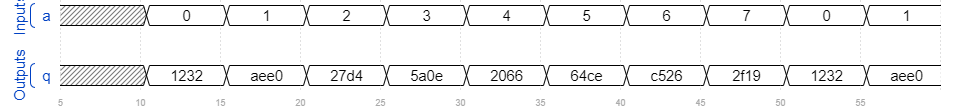

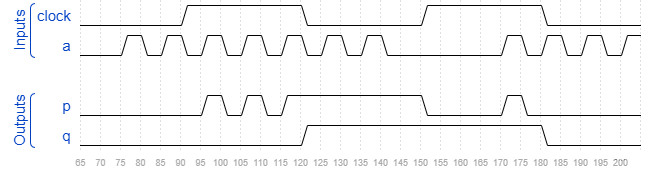

Sim/circuit8

p在clock为1时与a一致,否则则保持电平不变(可以让p<=p)

q在clock下降沿时改变,与p一致

module top_module (

input clock,

input a,

output p,

output q );

always@(*) begin

p=(clock)?a:p;

end

always@(negedge clock) begin

q<=p;

end

endmodule

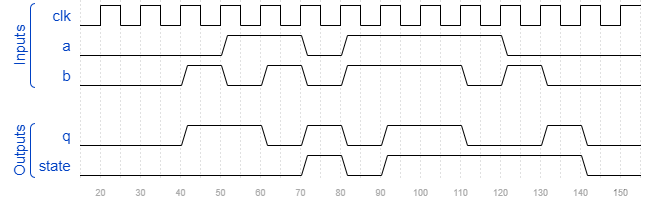

Sim/circuit10

This is a sequential circuit. The circuit consists of combinational logic and one bit of memory (i.e., one flip-flop). The output of the flip-flop has been made observable through the output state.

题目说有个触发器输出是state,则state应该是clk边沿触发,再看上升沿时刻ab值,可得state在上升沿时,若ab相等则与ab值等同,若不等则保持原来值

q则与a b state都关联

module top_module (

input clk,

input a,

input b,

output q,

output state );

always@(posedge clk) begin

state<=(a==b)?a:state;

end

always@(*) begin

q=(~state&((~a&b)|(a&~b)))| (state&((~a&~b)|(a&b)));

end

endmodule

2048

2048

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?