Mux256to1&Mux256to1v

256选1数据选择器题目:

Create a 1-bit wide, 256-to-1 multiplexer. The 256 inputs are all packed into a single 256-bit input vector. sel=0 should select in[0], sel=1 selects bits in[1], sel=2 selects bits in[2], etc.

Expected solution length: Around 1 line.

一行就能写出来,直接让sel作为in的索引

module top_module(

input [255:0] in,

input [7:0] sel,

output out );

assign out=in[sel];

endmodule256选1(数据位宽4)数据选择器题目:

Create a 4-bit wide, 256-to-1 multiplexer. The 256 4-bit inputs are all packed into a single 1024-bit input vector. sel=0 should select bits in[3:0], sel=1 selects bits in[7:4], sel=2 selects bits in[11:8], etc.

Expected solution length: Around 1–5 lines.

参照上面的,可以写成

assign out=in[(sel*4+3):sel*4];但是编译不通过,则可采取下面3种写法:

assign out = {in[sel * 4 + 3], in[sel * 4 + 2], in[sel * 4 + 1], in[sel * 4]}; assign out = in[sel*4+:4]; //从sel*4开始,选择比特序号大于sel*4的4位bit,相当于[sel*4+3:sel*4] assign out = in[sel*4+3-:4]; //从sel*4+3开始,选择比特序号小于sel*4+3的4位bit,相当于[sel*4+3:sel*4]————————————————

版权声明:本文为CSDN博主「杰之行」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/haojie_duan/article/details/113414855

Hadd

Create a half adder. A half adder adds two bits (with no carry-in) and produces a sum and carry-out.

Expected solution length: Around 2 lines.

设计一个半加器,没有下级输入的进位,只有进位输出和本位输出

可以直接把a+b赋给cout和sum,也可直接计算进位和本位:

module top_module(

input a, b,

output cout, sum );

//assign {cout,sum}=a+b;

// this is fine ,but the one below is better

assign cout = a & b;

assign sum = a ^ b;

endmodule

而全加器的进位和本位:

assign cout=a&b||b&cin||a&cin;

assign sum=a^b^cin;Exams/ece241 2014 q1c 数据溢出提示

Assume that you have two 8-bit 2's complement numbers, a[7:0] and b[7:0]. These numbers are added to produce s[7:0]. Also compute whether a (signed) overflow has occurred.

module top_module ( input [7:0] a, input [7:0] b, output [7:0] s, output overflow );A signed overflow occurs when adding two positive numbers produces a negative result, or adding two negative numbers produces a positive result. There are several methods to detect overflow: It could be computed by comparing the signs of the input and output numbers, or derived from the carry-out of bit n and n-1.

一个有符号数的最高位代表正负,最高位是0代表正数,最高位是1代表负数。

那什么时候会发生溢出(overflow)的情况?只有两个正数(负数)相加才会发生溢出,相减(即一正一负)是不会发生溢出的。

两个正数相加(符号位都为0),如果结果为负数,则发生溢出;两个负数相加(符号位都为1),如果结果为正数,则发生溢出,其他情况都为没有发生溢出。

module top_module (

input [7:0] a,

input [7:0] b,

output [7:0] s,

output overflow

); //

assign s = a + b;

assign overflow = a[7] & b[7] & ~s[7] | ~a[7] & ~b[7] & s[7];

endmodule

Adder100

Create a 100-bit binary adder. The adder adds two 100-bit numbers and a carry-in to produce a 100-bit sum and carry out.

Expected solution length: Around 1 line.

简单的加法器逻辑,直接得到最后的进位和本位:

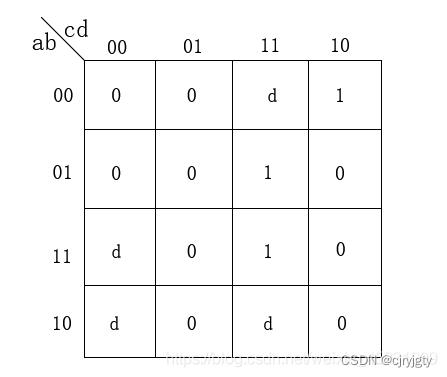

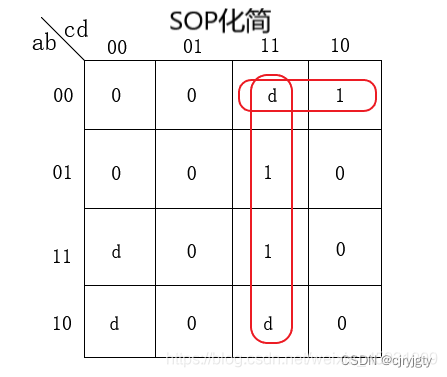

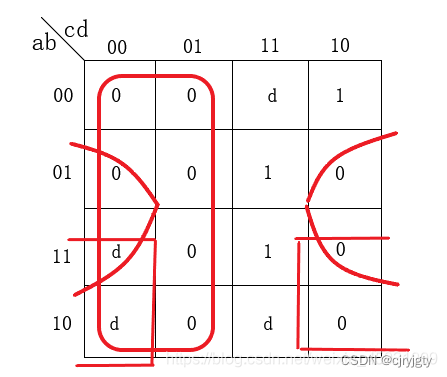

assign {cout,sum}=a+b+cin;Exams/ece241 2013 q2 关于卡诺图

A single-output digital system with four inputs (a,b,c,d) generates a logic-1 when 2, 7, or 15 appears on the inputs, and a logic-0 when 0, 1, 4, 5, 6, 9, 10, 13, or 14 appears. The input conditions for the numbers 3, 8, 11, and 12 never occur in this system. For example, 7 corresponds to a,b,c,d being set to 0,1,1,1, respectively.

Determine the output out_sop in minimum SOP form, and the output out_pos in minimum POS form.

- SOP form 即与或式,对应于卡诺图就是圈1即可

- POS form 即或与式, 对应于卡诺图就是圈0后,整体取反

module top_module (

input a,

input b,

input c,

input d,

output out_sop,

output out_pos

);

assign out_sop = (~a & ~b & c) | (c & d);

assign out_pos = ~((~c) | (b & ~d) | (a & ~d));

endmodule

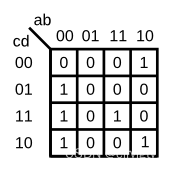

Exams/ece241 2014 q3

For the following Karnaugh map, give the circuit implementation using one 4-to-1 multiplexer and as many 2-to-1 multiplexers as required, but using as few as possible. You are not allowed to use any other logic gate and you must use a and b as the multiplexer selector inputs, as shown on the 4-to-1 multiplexer below.

You are implementing just the portion labelled top_module, such that the entire circuit (including the 4-to-1 mux) implements the K-map.

(The requirement to use only 2-to-1 multiplexers exists because the original exam question also wanted to test logic function simplification using K-maps and how to synthesize logic functions using only multiplexers. If you wish to treat this as purely a Verilog exercise, you may ignore this constraint and write the module any way you wish.)

不让用与或门了,让做成数据选择器的形式,ab不用管,只考虑输入cd的时候通过ab能得到怎样的输出,也就是只看卡诺图的列,可得:

①cd全0才输出0,②输出0,③cd全1才输出1,④ d=0才输出1

这种写法之前也没见过,需要注意

module top_module (

input c,

input d,

output [3:0] mux_in

);

assign mux_in[0] = c ? 1 :(d ? 1 : 0); //这就表示说cd全为假时,结果才为0

assign mux_in[1] = 1'b0 ; //恒为0

assign mux_in[2] = d ? 0 : 1; //这表示说~d时,结果才为1

assign mux_in[3] = c ? (d ? 1 : 0) : 0;//cd都为真时,取值为1

endmodule

53

53

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?