我还是初学者,以下很多判断和结论具有局限性,请大家批评指正,多多交流。

1 烧录程序报错: end of startup status:low

引脚电平约束错误

2 引脚绑定报错:Pin xx is an invalid placement site

IBUFDS i_ibufds_tx_ref_clk(

.I (tx_ref_clk_p),

.IB (tx_ref_clk_n),

.O (tx_ref_clk)

);

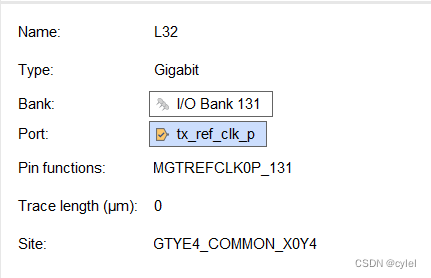

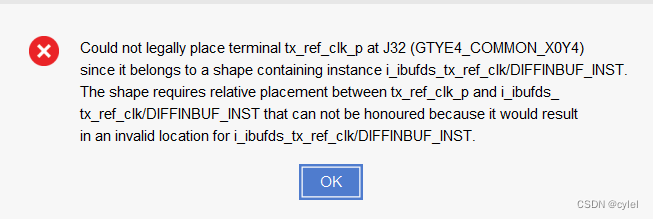

绑定tx_ref_clk_p到下图所示的引脚时,报告错误无法绑定。进一步研究错误发现报错如第二张图。

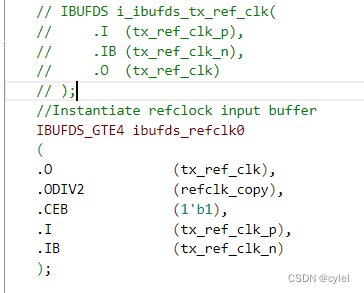

改成下面的方式解决了问题:(高速口进来的信号需要高速口专用的原语)

3 由于我有的板卡PL端没有时钟,需要PS端输出一个时钟给PL端。但按照之前使用只有FPGA的板卡来下载程序发现ILA报错,WARNING: [Labtools 27-3361] The debug hub core was not detected.

Resolution:

-

Make sure the clock connected to the debug hub (dbg_hub) core is a free running clock and is active.

-

Make sure the BSCAN_SWITCH_USER_MASK device property in Vivado Hardware Manager reflects the user scan chain setting in the design and refresh the device. To determine the user scan chain setting in the design, open the implemented design and use ‘get_property C_USER_SCAN_CHAIN [get_debug_cores dbg_hub]’.

For more details on setting the scan chain property, consult the Vivado Debug and Programming User Guide (UG908).

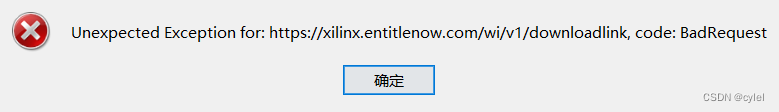

怀疑是PS端没有输出时钟->好像需要用SDK配置什么的->2023.1版本的Vivado file下面没有launch SDK->help下面add design tools 来下载Vitis->报错unexpected exception for: https://xilinx.entitlenow.com/wi/wi/v1/downloadlink

网上说的原因是1.登录XILINX的账号的信息没有填完整,需要补齐红色星号的信息。2.一些公司限制问题。

对我可能是第二个原因,学校可能有限制,换了一个邮箱登录账号后解决。

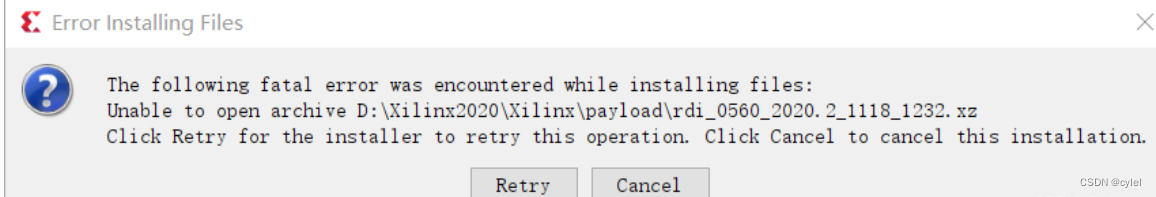

又报错

需要关闭杀毒软件(我关了360就好了),解决。

CP2103 USB to UART的端口在电脑设备管理器上识别不出。

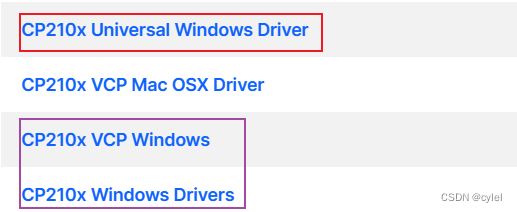

我的串口接口是一端usb一端micro usb,因为一般来说是驱动的问题,所以从官网https://www.silabs.com/developers/usb-to-uart-bridge-vcp-drivers?tab=downloads安装驱动。红色里面是win10 11,紫色里面是win7/8,我都装了一遍。还是识别不了,拔插线设备管理器都没反应。最后换了好多根线,终于有一根能识别出。

1900

1900

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?