目录

实际晶体的特点:

1. 晶体中的原子不是禁止的,而是在平衡位置做振动

2. 实际半导体并不纯净,而是或多或少含有若干杂质

3. 实际晶体并非完美,存在点缺陷,线缺陷,面缺陷

我们要把这些因素引入到半导体中来

硅和锗中的杂质能级

原因:

1. 原材料的纯度不够

2. 在器件与电路制造过程中引入的沾污

3.为了控制半导体材料的性能,人为引入的

引入的第一个方式,杂质的存在方式?

1. 替位式杂质和间隙式杂质

三五族元素在硅和锗重是替位元素,这是金刚石原子的原子密度

,一个金刚石结构的晶胞里面,如果把原子放大的话,这八个球占立方晶胞达到34%

杂质还可以位于这些空的间隙位置,通常要求个头比较小

杂质浓度的概念:单位体积中杂质原子的个数,单位()反映了,杂质含量的多少

2.施主杂质和施主能级

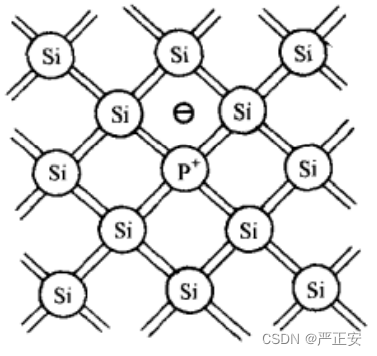

我们已Si重掺入五族元素,硅重掺入磷为例,Si是典型的共价晶体,与周围的形成饱和的共价键

磷是五族元素,1. 其中四个价电子可以与周围四个硅原子形成饱和共价键,那这样的话就多了一个价电子,2. 多了一个价电子,磷原子所在处多一个正电荷

和本征情况比一比,硅重掺入了磷之后,产生的差别:

1.产生了一个多余的价电子,一个正电中心,所以和不掺的情况对比起来看,多余的价电子是现在还不是自由的,正负电荷之间有库伦引力,被正电中心

离子所束缚,大家看在这样的示意图里面,横线表示共价键,这些电子也是被共价键所束缚,多余的电子被中心正离子束缚,这两种束缚不一样,电子挣脱共价键最低是禁带宽度,而挣脱库伦引力的能量,则是远小于共价键的束缚

很小的能量就可以让它挣脱束缚,挣脱了束缚的电子就成了所谓的自由电子(做共有化运动),正电中心P离子被四个共价键束缚,所以不能自由运动

多余的电子挣脱束缚,就相当于电离了

杂质电离:电子挣脱杂质原子的束缚,称为导电电子的过程

杂质电离能: 使电子挣脱杂质原子的束缚,成为导电电子所需要的能量 成为杂质电离能,记作,又称为施主杂质电离能

这么说相当于五族元素可以释放出电子,所以我们把五族元素称为施主元素,称作donor

那么施主杂质的电离能这个☞远弱于共价键的束缚,我们关心这个值有多大?

值,如果五族元素掺入锗重,大多比较接近在0.01ev左右,如果掺入硅中的话,大约是0.04~0.05ev左右

Si中掺入磷,磷在硅中的电离能0.044电子伏特,这个值远远小于禁带宽度(因为都是向导带提供电子,所以要和禁带宽度比)

施主电离并不会产生多余的空穴,这是与本征激发的一个区别

五族元素释放电子的过程,称为施主电离,施主杂质未电离的时候,是电中性的,电离以后,成为正电中心,分别称为中性态(束缚态)和施主离化态

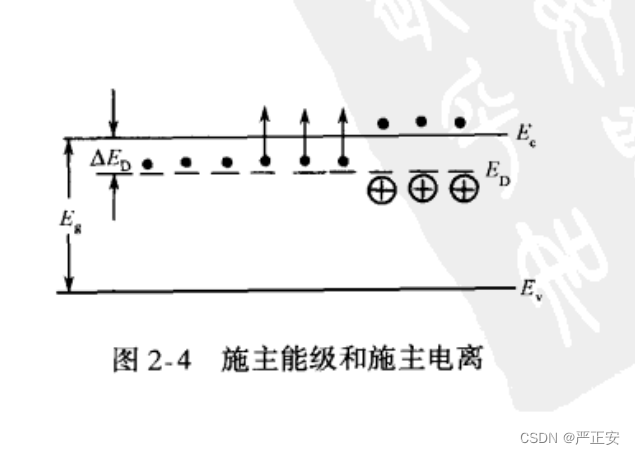

从能带结构上来看

如果掺入施主以后,多余的电子就变成了导电电子,导电电子在导带底附近,这是施主杂质多于电子被束缚时候的能量状态,我们称之为施主能级,通常情况下掺杂浓度比较低

单位体积中掺杂浓度低,杂质含量较少

展宽成能带要相互靠拢,杂质原子相距较远,所以形成了一些相同能量的孤立能级,而不是能带

Si中掺入磷以后,相当于就是在原来的基础上引入施主能级,所以,半导体中掺入五族元素后,称主要依靠电子导电的半导体为N-型半导体

3.受主杂质 受主能级

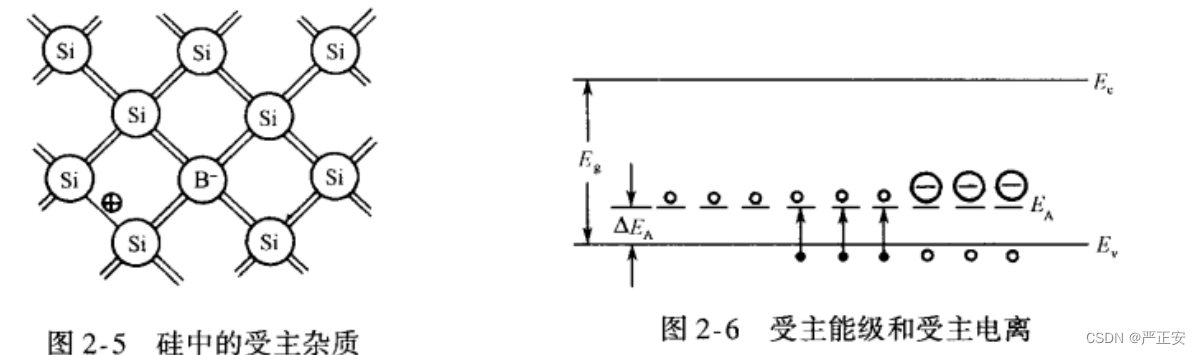

B在硅中的替位式杂质,B在硅中是替位杂质,我们就会缺少一个价电子,为了形成四个饱和的共价键,他会从其他地方获得一个电子,使它自身形成饱和共价键,这样子就变成了负电中心,这就是Si中掺入三族元素B的情况

Si中掺入B效果上看,形成了一个负电中心形成一个多余的空穴,多余的空穴也是被负电中心

所束缚住,被束缚住,就不能自由运动,就不能导电,这种束缚演员弱于共价键的束缚

也就是说我们只要很小的能量就可以让它挣脱束缚,称为导电空穴

负电中心是不能运动的,如果掺入三族元素的话,缺少电子,就可以束缚空穴,导电空穴增加了,但是电子并没有增加

受主杂质未电离的时候是电中性的,电离以后,称为负电中心,称为受主离化态,空穴挣脱束缚的过程称为受主电离,空穴挣脱受主杂质的束缚所需要的能量,这个称为受主杂质电离能,记作

受主杂质电离能,在Ge中大约是0.01ev,在硅当中大约是0.045~0.065ev之间,但是大家特别注意要把铟除外,铟在Si中的受主杂质电离能是0.16ev(非常大,大带来的问题是不容易电离)

半导体中掺入三族元素后(受主杂质),杂质电离使导电空穴增多,称主要依靠空穴到带你的半导体为P型半导体

小结:

1. 在硅和锗中掺入三族元素,是受主杂质,在禁带当中引入了比价带顶,高

的受主能级

中性态(又称束缚态),空穴释放出去,又叫受主离化态,向价带提供导电空穴。掺入五族元素,是施主杂质,它在半导体的禁带当中,引入了比导带底低了

的施主能级

,也有中性态和施主离化态,向导带提供导电电子

2.三族杂质的电离能和五族元素的电离能很小,只有零点零几个电子福特,也就是对于施主来说,施主杂质的施主能级,也就是距离导带底非常近,而对于受主杂质的受主能级来说,距离价带顶来说非常近,满足这样的条件,称为浅杂质能级(浅能级),对应的杂质就称为浅能级杂质

硅和锗中的三五族元素除了铟以外都是浅能级杂质,浅能级是与否要对应开来比

3.室温条件下,硅和锗中的三五族元素杂质几乎全部离化,这就是模拟电路里学的,掺入一个施主就有一个电子

4.潜能及杂质电离能的简单计算?-----类氢模型

我们以硅中掺入磷为例,磷多余的电子成为自由电子,这个情况很像氢原子核然后带一个核外电子

,当n取无穷大的时候,也就是挣脱了束缚,取1就相当于是基态

,那么这个情况和它很像,但是一个在真空中,另一个在Si中

所以要把换成

,,第二个晶体当中的个电子

5.杂质的补偿作用?

我们在同一块半导体总掺入施主和受主,如果我们既掺入施主,又掺入受主时,则施主杂质和受主杂质具有相互抵消的作用,称为杂质的补偿作用

为什么会有相互抵消的作用?

假设施主杂质浓度(单位体积中所含的个数)(

),受主杂质浓度

,对半导体的导电性之有贡献的载流子是电子,电子在导带中,导电的电子浓度

,价带的空穴浓度

,有了这些假设的条件我们就可以说明杂质的补偿作用是怎么产生的

(1)如果,电子优先填充受主能级,导带电子

,我们称

称为有效施主浓度

(2)如果 想法类似

(3)施主杂质浓度和受主杂质浓度几乎相等,我们把这种情况称为高度补偿,杂质多了,负电性不一样,会引入晶格畸变,由于杂质引入,迁移率会降低

如何形成N-P-N结构?

在高温下,给Si片,通入氧气,会生成二氧化硅,那么通入氧气生成二氧化硅,二氧化硅应该在上下左右面都有,二氧化硅为了保护这个面

生长完了二氧化硅的衬底上,我们涂胶(光刻胶),我们以负胶为例,涂在硅片表面,没有见到紫外线的话,是链状结构,链状结构扛不住有机溶剂的溶解,比如丙酮,就会溶解,如果光刻胶用紫外光照射以后,链状变成网状,无法溶解

下一步就是光刻的工艺,玻璃基板有一层膜,比如金属镉,集成电路设计一方面是电路设计,另一方面要做成板图,压在光刻胶表面,然后用平行紫外线光照射,把这样的样品放到丙酮溶液中去,网状结构无法溶解,光刻工艺完成以后

相当于就开了窗口,左右两部分就被光刻胶保护起来了,然后用氢氟酸腐蚀一下,这一部分没有用光刻胶保护,中间的二氧化硅就被腐蚀掉了,另外两部分光刻胶已经网状化了,然后放在浓硫酸里面,加热煮开,就把光刻胶膜碳化了,最后用去离子水冲洗干净

下来就是我们说的杂质补偿,在一千多度下,把三族元素淀积在中间,比如硼,淀积完了以后,就把硼源关上,高温下进行扩散(称为再分布),在在分布的同时,再通上氧气,继续生成二氧化硅,中间生长的快,二氧化硅又长平了,硼原子又去补偿,这样第一个P就出来了

我们重复刚才的过程,然后再用另外一块光刻板,有透光区域,也有不透光区域,然后再用紫外光曝光,这一部分不透光,在那走光刻板,丙酮里面显影,氢氟酸里面腐蚀二氧化硅,然后再在浓硫酸里面煮一煮,高温环境下通氧气,然后N就出来了

这样子的话三区两节就出来了

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?