在HDLbits中看见如下一道题:

创建一个 4 位宽、256 对 1 的多路复用器。 256 个 4 位输入全部打包成一个 1024 位输入向量。 sel=0 应该选择[3:0] 中的位,sel=1 选择[7:4] 中的位,sel=2 选择[11:8] 中的位等。

解题代码如下:

module top(

input [1023:0] in,

input [7:0] sel,

output [3:0] out);

assign out = in[sel*4 + 3 : sel*4 + 0];

endmodule

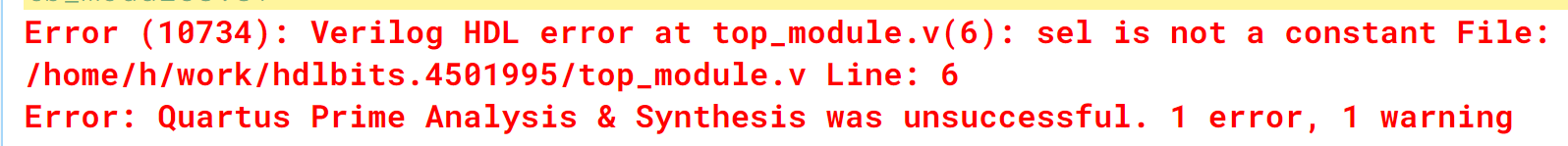

如上,当使用这种写法进行部分选择数组时,会报错。

通过查询资料发现错误原因如下:

在Verilog-1995中,可以选择向量的任一位输出,也可以选择向量的连续几位输出,不过此时连续几位的始末数值的index需要是常量。vect[msb_expr : lsb_expr]; //其中msb_expr和lsb_expr必须是常量表达式

在Verilog-2001的最新标准中,增加了通过索引index来实现对数组的部分选择。如下:

[base_expr +: width_expr]

和

[base_expr -: width_expr]

其中base_expr可以是变量,而width_expr必须是常量。+:表示由base_expr向上增长width_expr位,-:表示由base_expr向下递减width_expr位。

因此对上题可以用如下写法:

assign out = in[sel*4+:3]//当sel=0时,相当于in[0:3]

注:

冒号:两边不能同时有变量, 因此in[sel*4 + 3 : sel*4 + 0]这种写法会报错。

427

427

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?