logic [31:0] data [1024]; //is equivalent to logic [31:0] data [0:1023];

引用即为:assign data[2][31:0] = 32’b0;//意思是第2组data赋值为32’b0

声明:reg [31:0] data[i];

引用:data[i] [2]

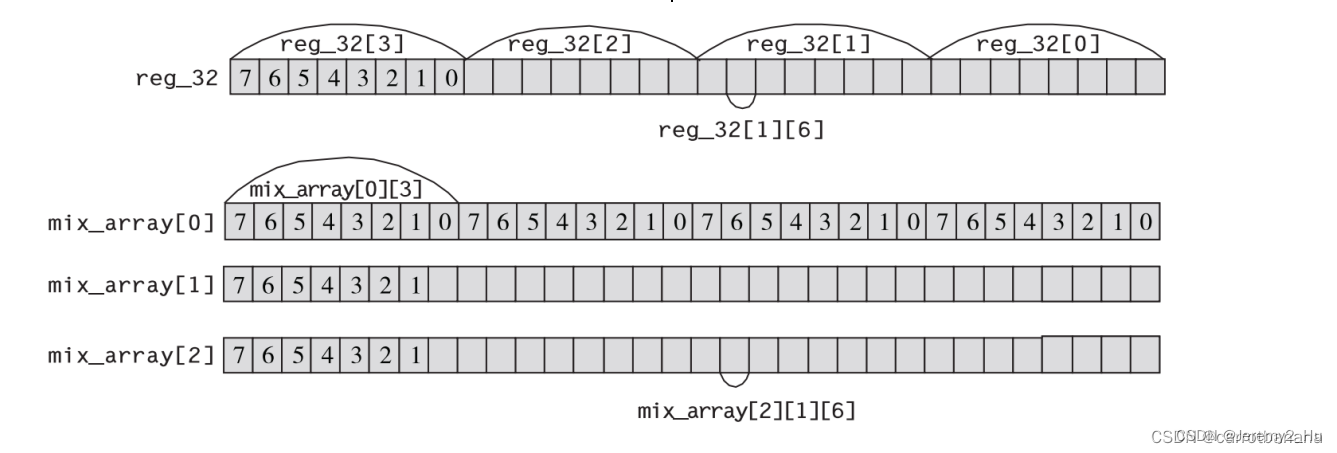

bit [3:0][7:0]reg_32; //压缩数组

bit [3:0][7:0]mix_array[3];//非压缩数组

参考链接:

https://blog.csdn.net/carrotbanana/article/details/124766630?ops_request_misc=&request_id=&biz_id=102&utm_term=sv%E5%8E%8B%E7%BC%A9%E6%95%B0%E6%8D%AE%E7%9A%84%E4%BD%BF%E7%94%A8&utm_medium=distribute.pc_search_result.none-task-blog-2allsobaiduweb~default-9-124766630.nonecase&spm=1018.2226.3001.4187

9299

9299

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?