Getting Started

Output one

问题:建立一个没有输入只有一个输出的电路。输出应该总是驱动1(或逻辑高)。

需要在[fixme]中输入相应的值

对应的格式:e.g. 位宽+‘+进制+数字:6’b11

Verilog语法

Wire

与物理线不同,Verilog中的线(和其他信号)是定向的。这意味着信息只在一个方向流动,从(通常是一个)源到汇点(源也经常被称为将值驱动到线路上的驱动器)。在Verilog的“连续赋值”(assign left_side = right_side;)中,右侧信号的值被驱动到左侧的线路上。这个赋值是“连续的”,因为即使右边的值发生了变化,赋值也一直在进行。连续分配不是一次性事件。

模块上的端口也有方向(通常是输入或输出)。输入端口是由模块外部的东西驱动的,而输出端口是由模块外部的东西驱动的。当从模块内部查看时,输入端口是驱动程序或源,而输出端口是接收器。

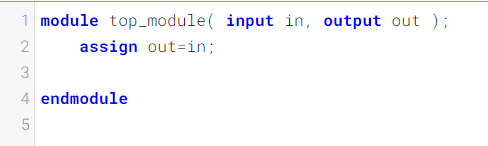

下面的图表说明了电路的每个部分是如何对应Verilog代码的每个位的。模块和端口声明创建了电路的黑色部分。您的任务是通过添加一个assign语句来连接到out来创建连接(绿色部分)。

英文;分号不要忘记写

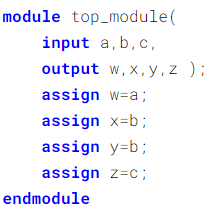

当您有多个赋值语句时,它们在代码中出现的顺序并不重要。与编程语言不同,赋值语句(“连续赋值”)描述的是事物之间的连接,而不是将一个值从一个事物复制到另一个事物的动作。

assign {w,x,y,z} = {a,b,b,c};

三种赋值语句:

assign:assign out=a&b

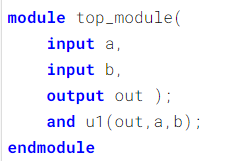

用实例元件,如例子中所示

用always语句

或非门

Out = !(a|b);

nor u1(out,a,b);

and与门的符号(上图)

nor或非门的符号(上图)

同或门XNOR

即a和b相同为真,不同为假

assign out = !(a^b);

assign out = (a^~b);

assign out = (!a^b);

Declaring wires

wire not_in; // Declare a wire named “not_in”

and or nor 只能用在实例元件中,作为开头

4479

4479

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?