前言

本文为我自己的学习笔记,属于Cadence Virtuoso系列的进阶部分,采用的软件版本是Cadence Virtuoso IC617。其他文章请点击上方,看我制作的Cadence Virtuoso专栏内容。

在前面的文章中,记录了gm/id设计方法,以及使用Cadence Virtuoso IC617仿真有关参数曲线,可以点击下面的链接查看。本文记录了,结合前面文章提到的gm/id设计方法去设计一个有源负载差动对(俗称五管OTA)。

原理

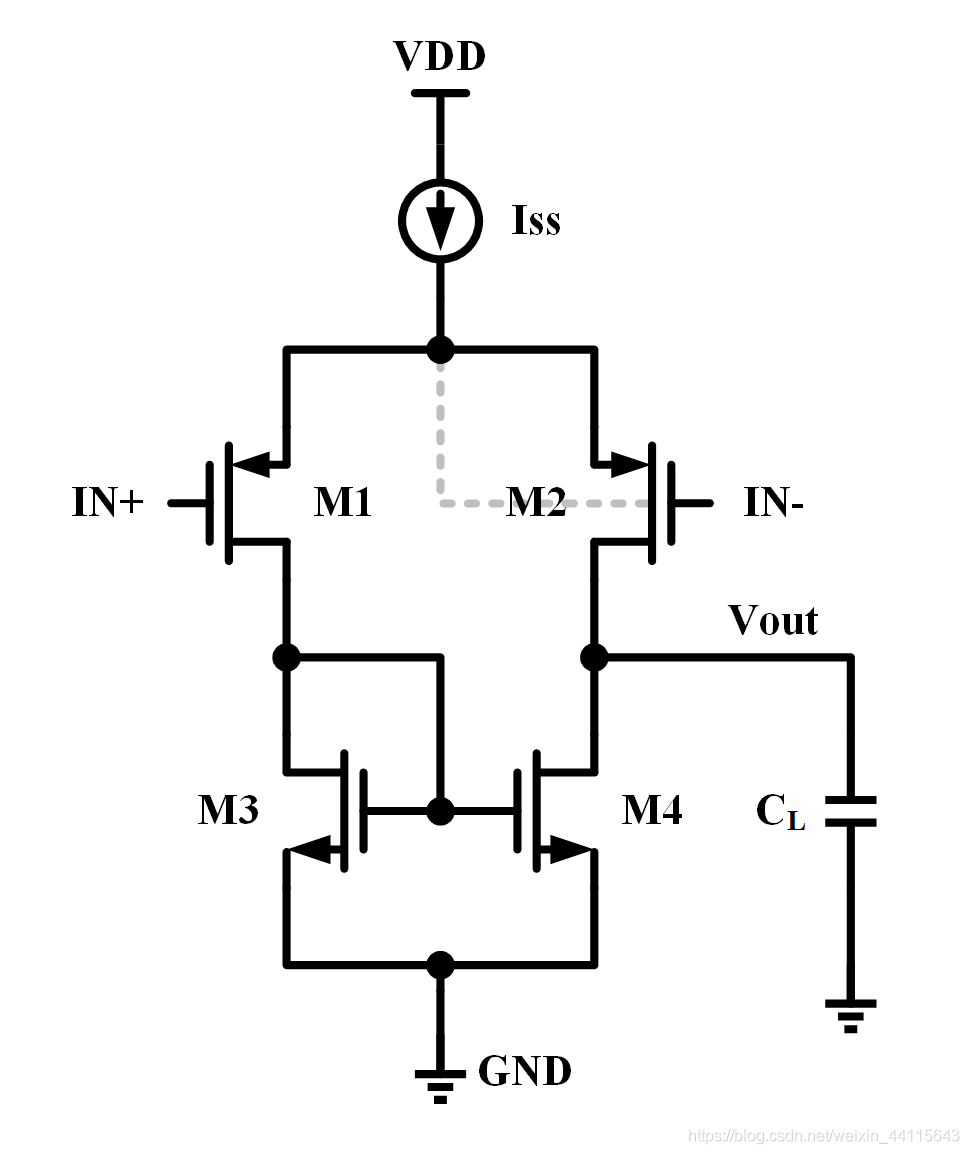

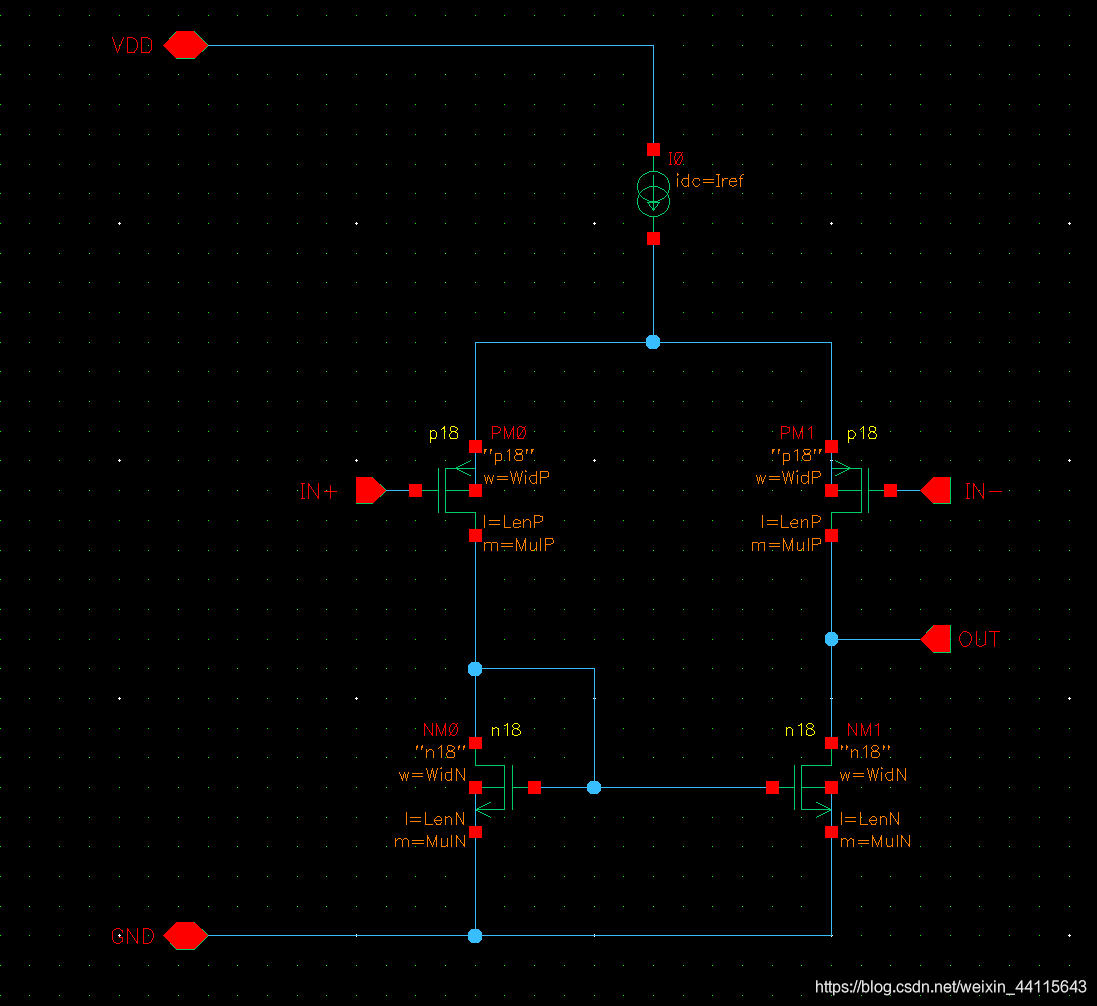

电路拓扑

改变一下电路拓扑,让P-MOS成为输入管,可以降低输入共模电平,以及降低噪声。同时,为了简化设计,此处把原来的M5使用一个理想电流源代替。注意,此处P-MOS的B端连接到S端。最终得出的尺寸会较大,这里设置 Multiplier=4 。

参数指标

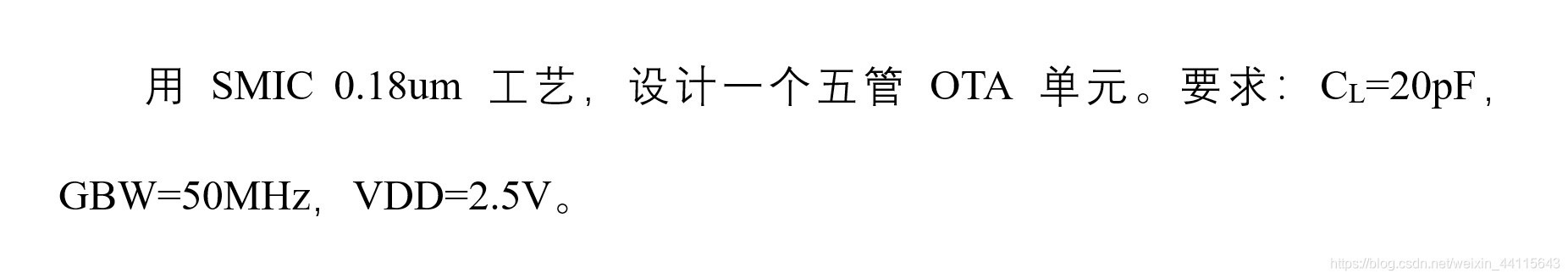

以一个例题举例,题目要求如下:

计算步骤

确定M1和M2尺寸

由前面提到的GBW公式,可以得到gm1和gm2。(此处只是举例计算,负载电容没有考虑取1.2CL,实际设计时应考虑电路寄生电容)

G B W = A V f T = g m 1 , 2 2 π C L ⇓ g m 1 , 2 = 6.28 m A / V GBW=A_Vf_T={ g_{m1,2} \over 2 \pi C_L } \\\dArr\\ g_{m1,2}=6.28 \enspace mA/V GBW=AVfT=2πCLgm1,2⇓gm1,2=6.28mA/V

对增益和带宽进行折中,取gm/id=12。

g m I D = 12 ⇓ I D = 0.523 m A {g_m \over I_D} =12 \\\dArr\\ I_D=0.523 \enspace mA IDgm=12⇓ID=0.523mA

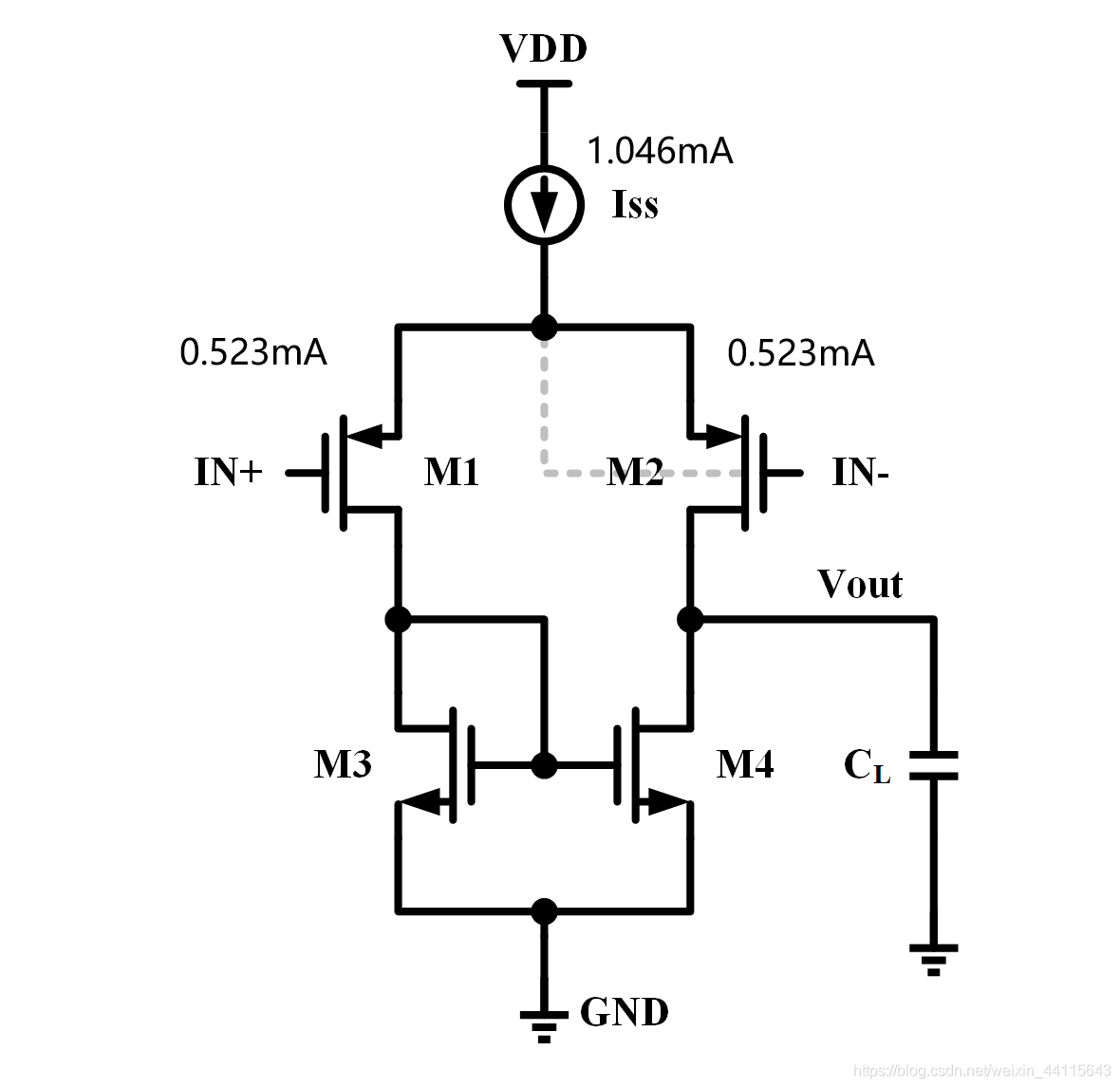

就确定了两边支路的电流,同时Iss即为两倍支路电流。

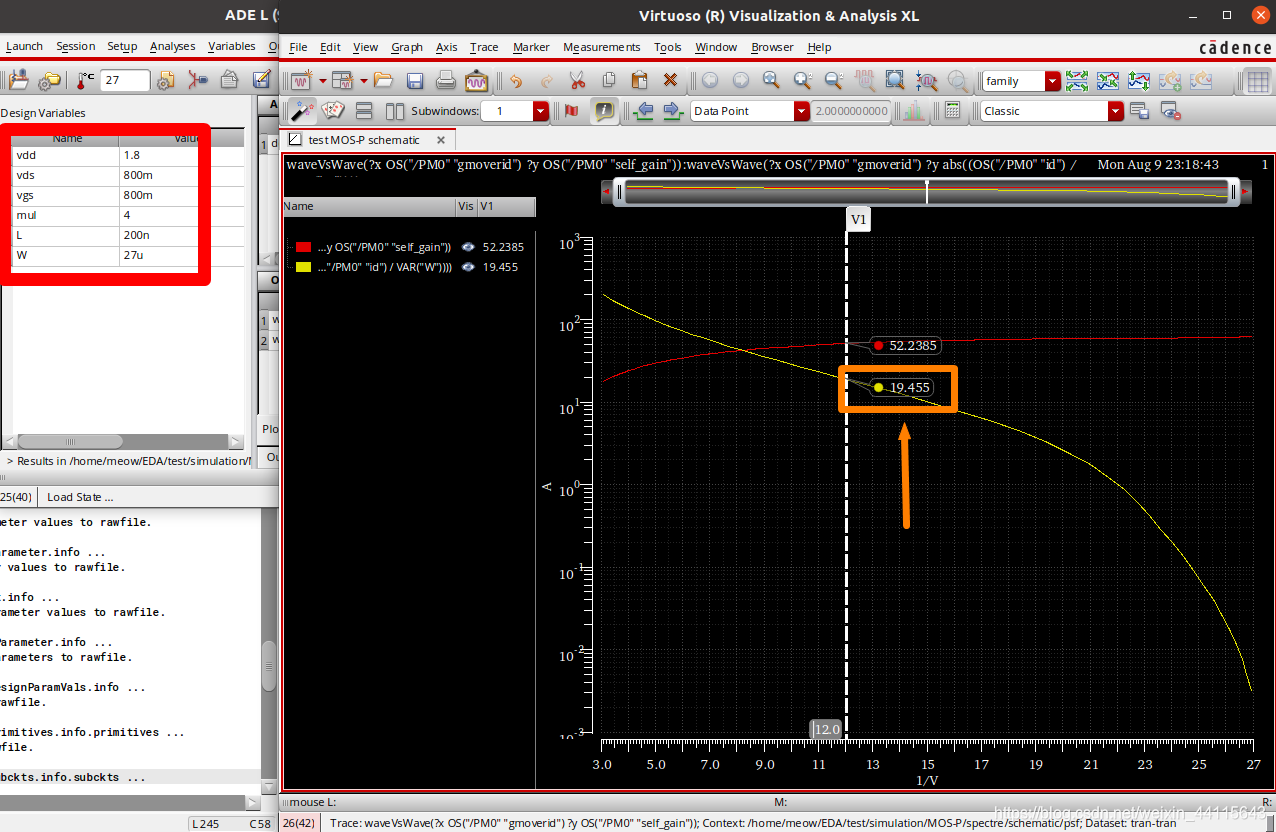

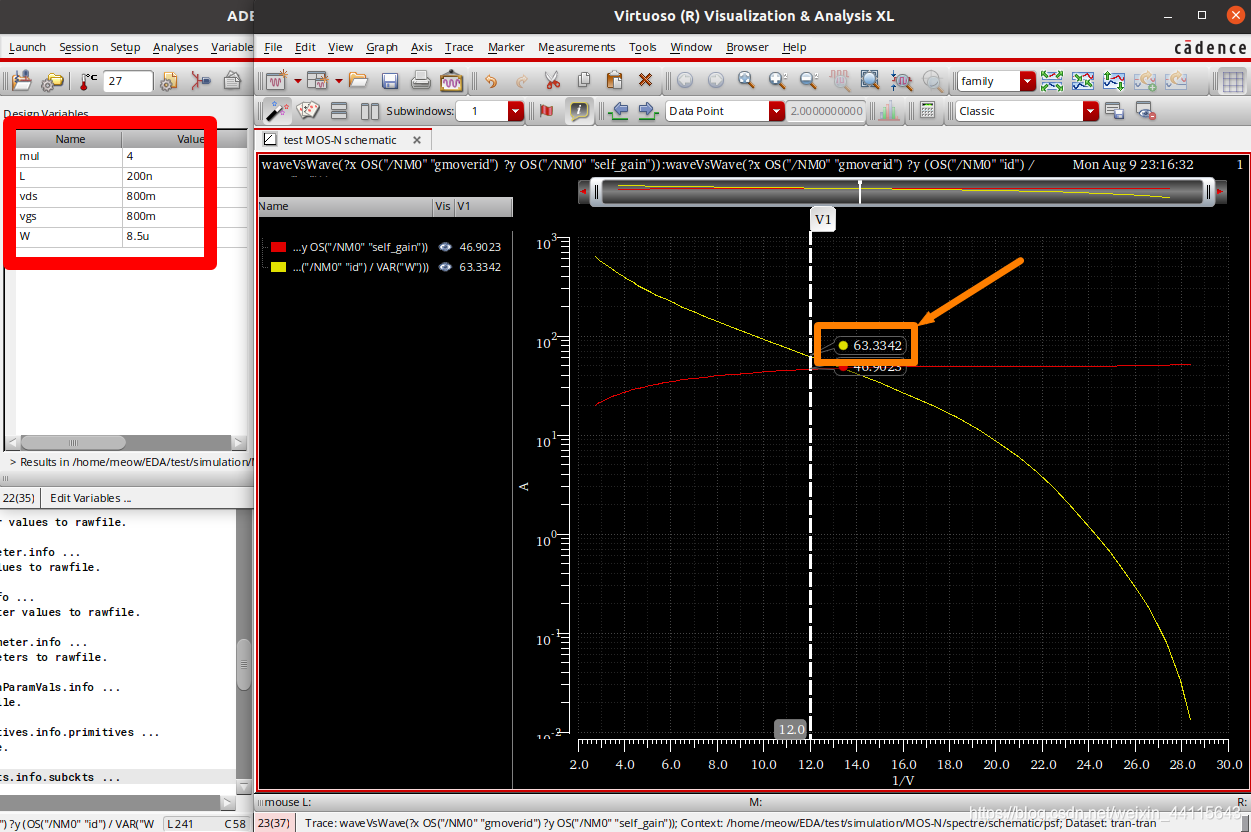

选取L=200nm,查阅曲线,得到id/W的数值为19.455。

就可以得到M1和M2的W。

I D W p 1 , 2 = 19.455 ⇓ W p 1 , 2 = 26.88 μ m { I_D \over W_{p1,2}} =19.455 \\\dArr\\ W_{p1,2}=26.88 \enspace \mu m Wp1,2ID=19.455⇓Wp1,2=26.88μm

确定M3和M4尺寸

前面已经得到了支路电流为0.523mA,确定gm/id后,可以直接算得W。

这里为了简便计算,依然让gm/id=12。选取L=200nm,查阅曲线,得到id/W的数值为63.3342。

就可以得到M3和M4的W。

I D W n 3 , 4 = 63.3342 ⇓ W p 1 , 2 = 8.26 μ m { I_D \over W_{n3,4}} =63.3342 \\\dArr\\ W_{p1,2}=8.26 \enspace \mu m Wn3,4ID=63.3342⇓Wp1,2=8.26μm

结果仿真

参数汇总

根据以上结果,汇总成下表。

| 1,2 | 3,4 | |

|---|---|---|

| W | 26.88u | 8.26u |

| L | 200n | 200n |

| Multiplier | 4 | 4 |

绘制器件

在Cadence Virtuoso IC617里绘制器件内部的原理图。其中,为了方便修改,将W,L,Multiplier这三个关键参数设置为变量。由于之前文章记录过详细过程,这里一笔带过。

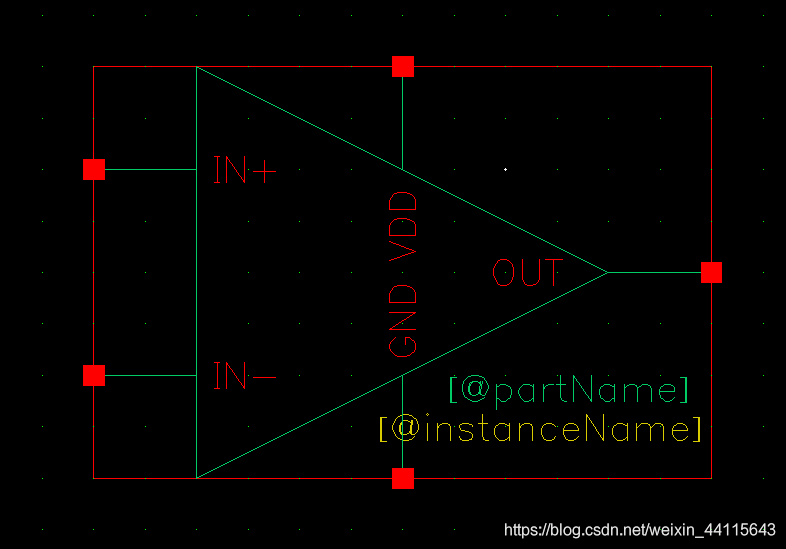

生成器件

由于之前文章记录过详细过程,这里一笔带过。

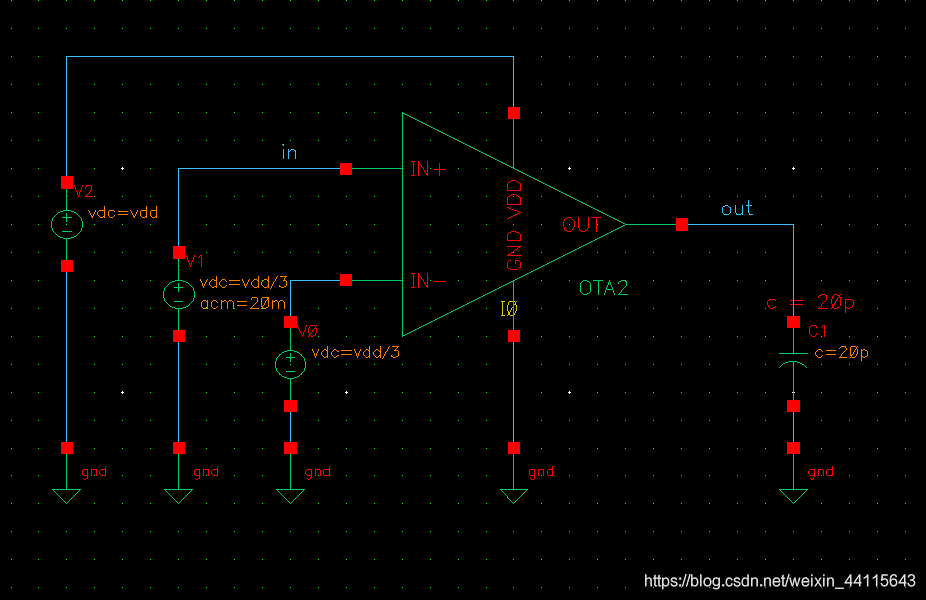

绘制测试用原理图

由于之前文章记录过详细过程,这里一笔带过。这里的差模输入,按照之前的使用vsin也可以,按照现在的使用vdc再设置里面的Ac magnitude参数也可以。

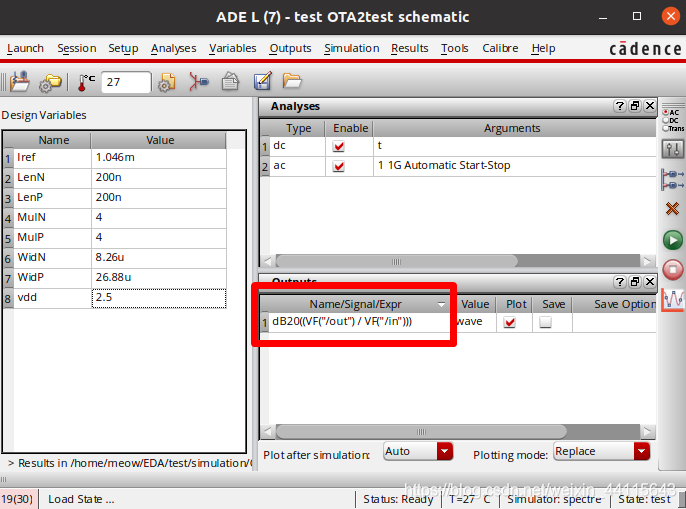

仿真设置

依次设置仿真类型,选择ac仿真,频率从1到1000M(这样出来的X轴为非线性,比较直观),输出点具体设置比较简单,略过。输出dB20参数的那个代码如下记录。

dB20((VF("/out") / VF("/in")))

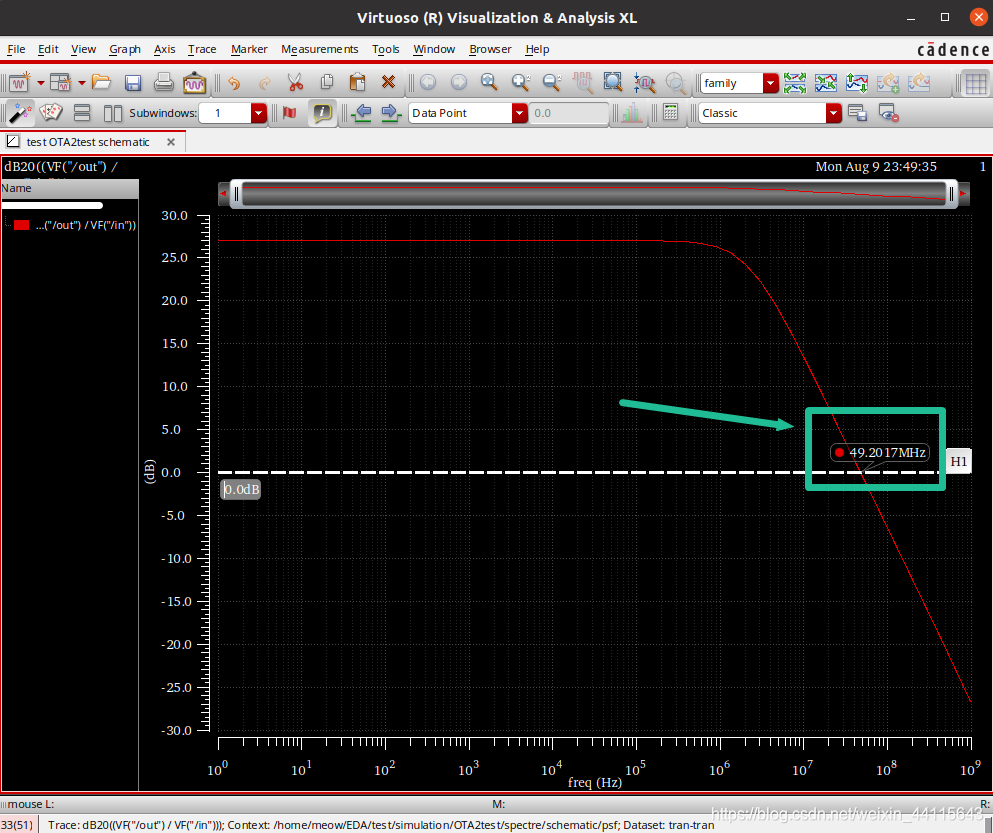

测试结果

点绿色图标开始仿真,出来仿真结果。得出GBW为49.2MHz,基本符合所需要的参数。当然,此电路还有很多优化的地方,但本文只讨论设计,优化的部分受限于篇幅,不在这里讨论。

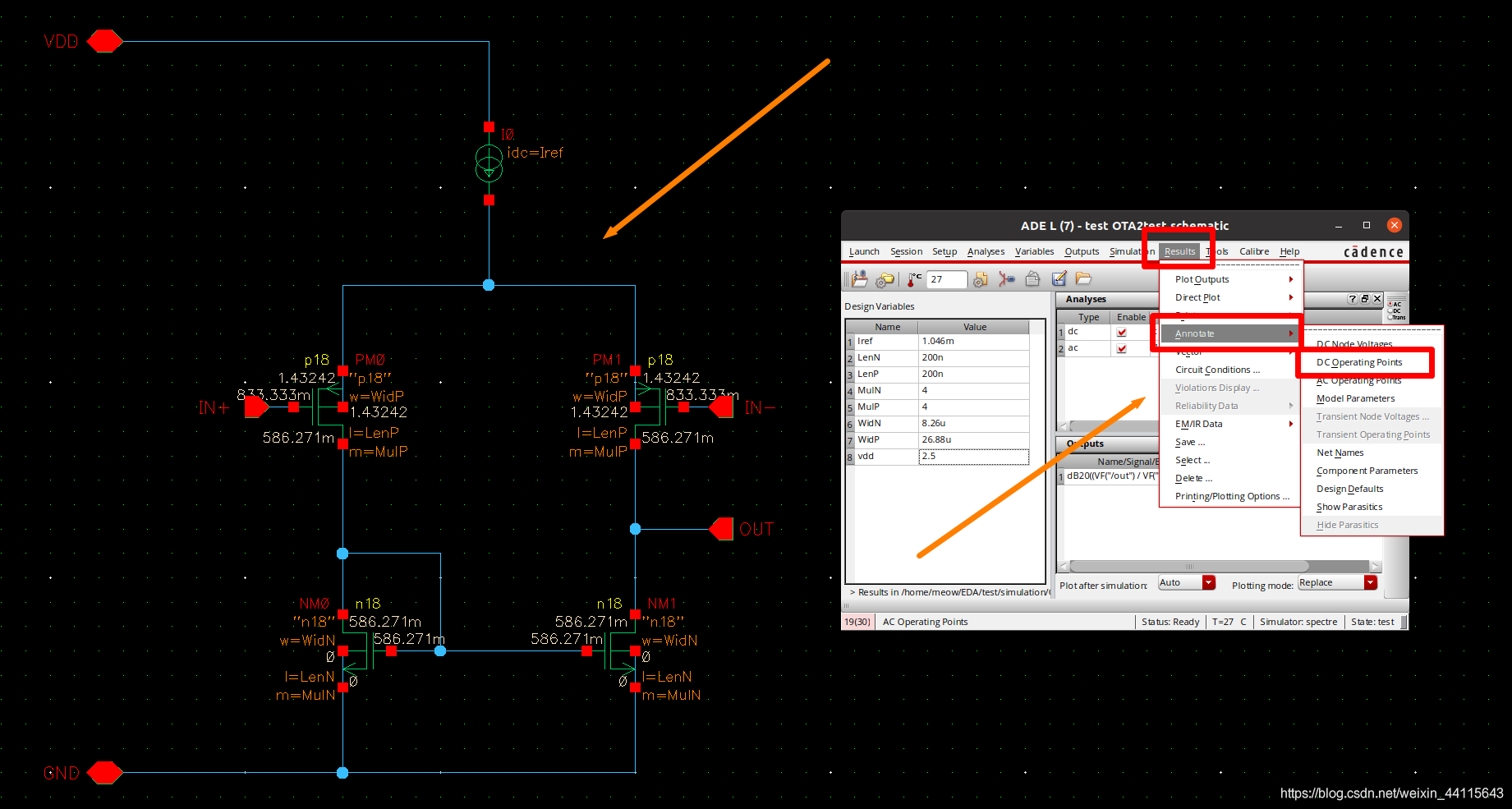

观察器件的直流参数,看看和预设是否接近。点击器件按E进入下层原理图,打开DC点显示。

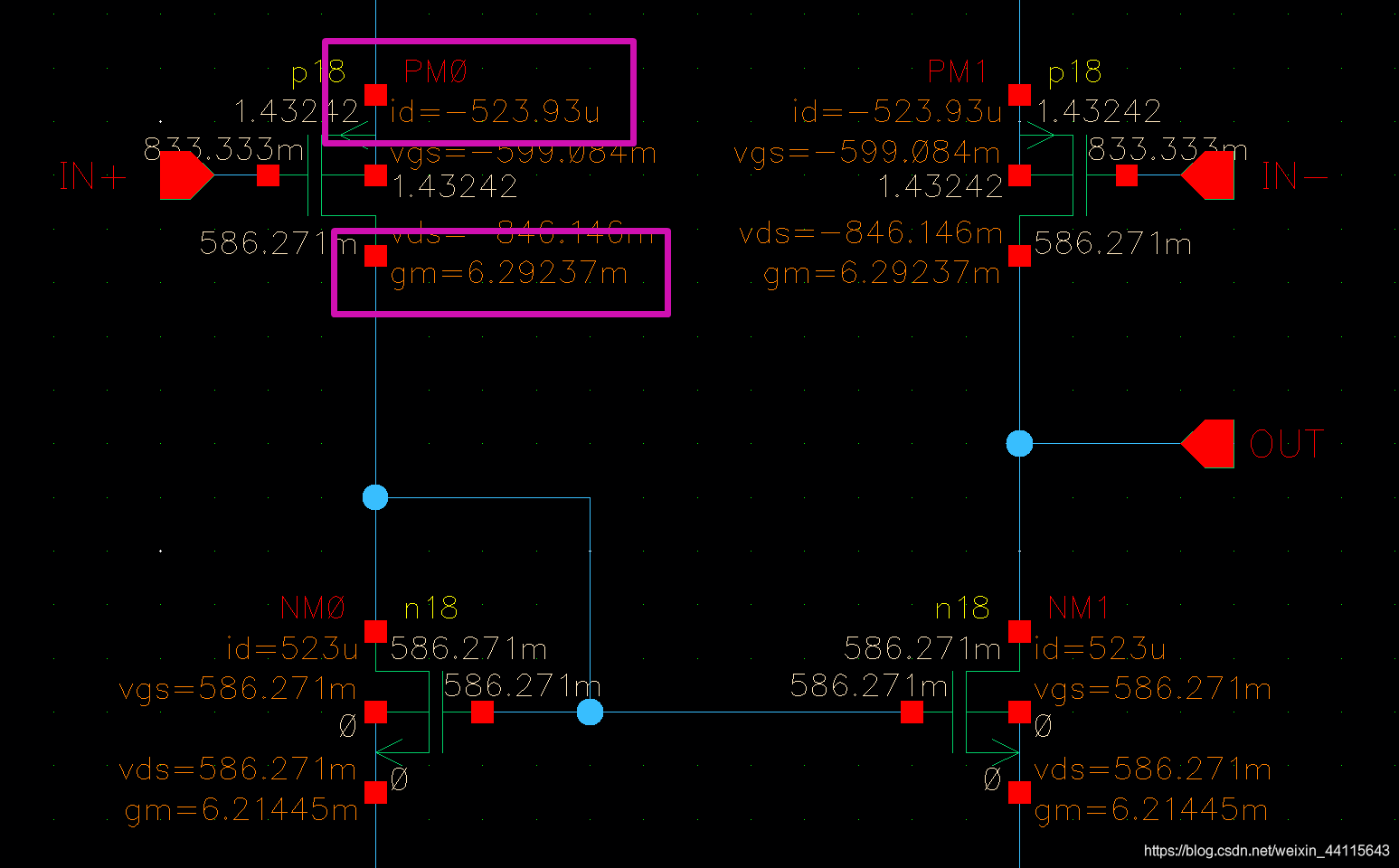

可以看到gm和id的值都很接近之前预想的值。

注意,前面仿真N-MOS和P-MOS的id/W曲线时使用的W参数是我事先计算好的,因为不同的W,出来的id/W是稍微有些差别的,这会导致最终计算出来的W有约0.1到0.2um的差别。

在实际设计时,我们通过计算得到W后,应该代回到前面仿真曲线时的那个参数里,再重新仿真一次id/W曲线,用这个新得到的id/W数值,重新计算一遍W,得到的结果才比较准确。

1545

1545

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?