Wire

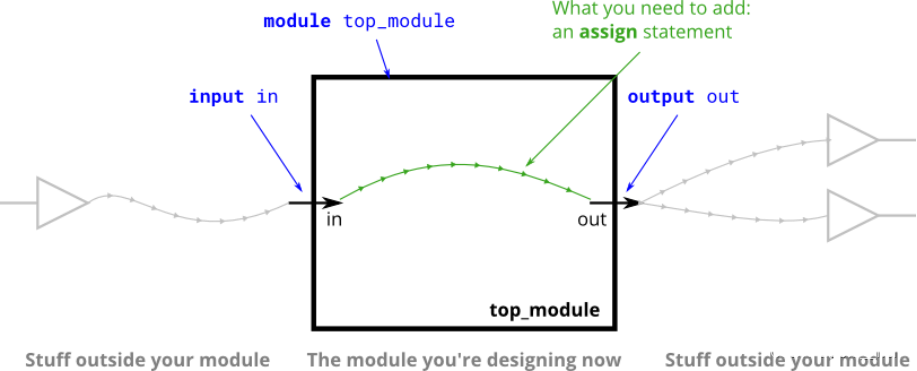

一、题目要求

创建一个具有一个输入和一个输出的模块,其行为类似于连接。

题目给的模块图

二、分析

连接输入输出,使用assign语句即可。这里要注意in和out是“有方向”的,你需要把in的值赋给out,而不能反过来,不然会报错。

代码如下:

module top_module( input in, output out );

assign out=in;

endmodule

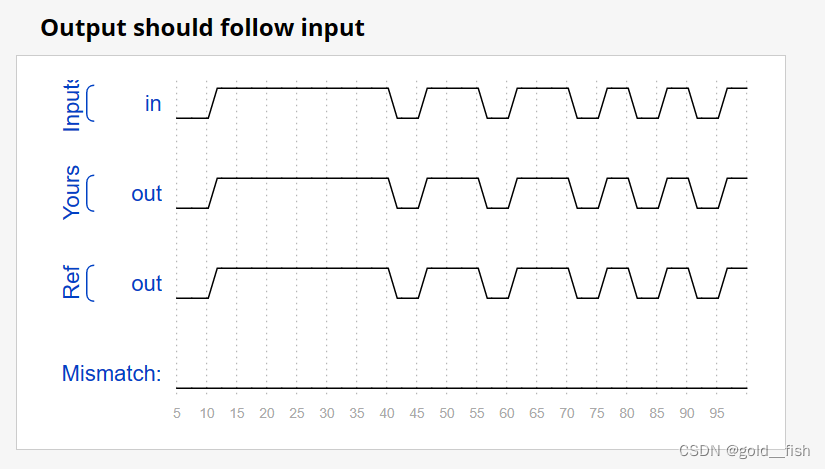

三、仿真图:

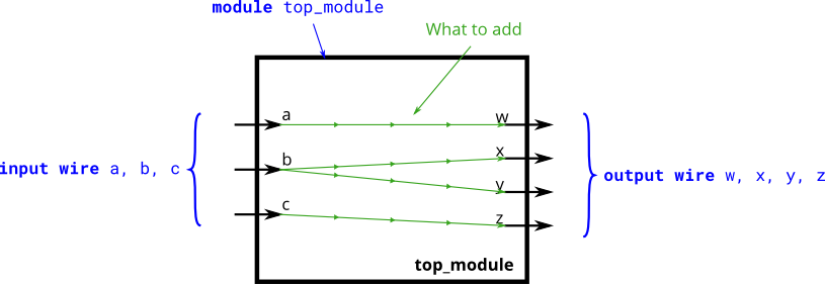

Wire4

一、题目要求

创建一个具有3个输入和4个输出的模块,输出输入的关系如下图模块所示

二、分析

输入输出均为“wire”类型,他们的关系是直接连接的,故直接使用assign语句即可。

代码如下:

module top_module(

input a,b,c,

output w,x,y,z );

assign w=a,x=b,y=b,z=c;

endmodule

三、仿真图:

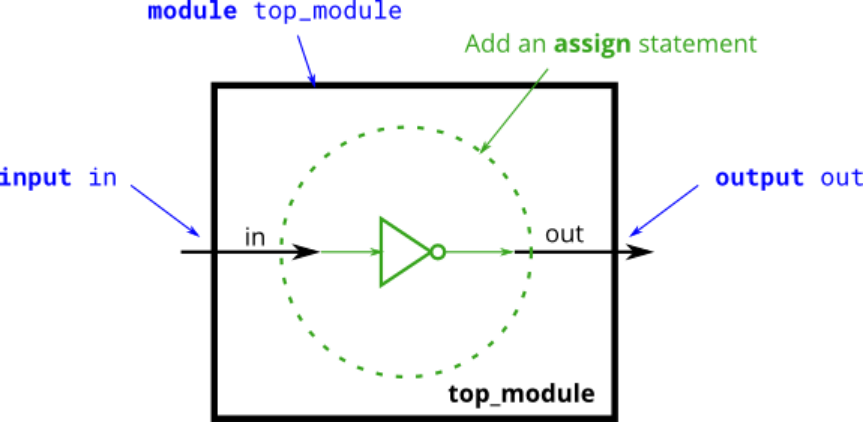

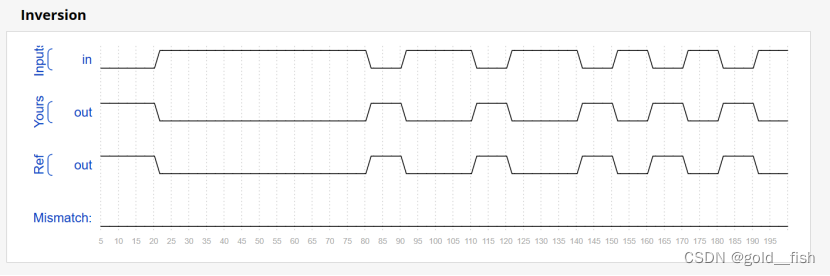

Notgate

一、题目要求

创建一个实现NOT(非)门的模块。模块图如下所示

二、分析

输出跟输入的关系为逻辑非,关系如下图真值表。逻辑非用verilog语言描述为“~”,赋值语句使用assign。

| in | out |

|---|---|

| 0 | 1 |

| 1 | 0 |

代码如下:

module top_module( input in, output out );

assign out=~in;

endmodule

三、仿真图

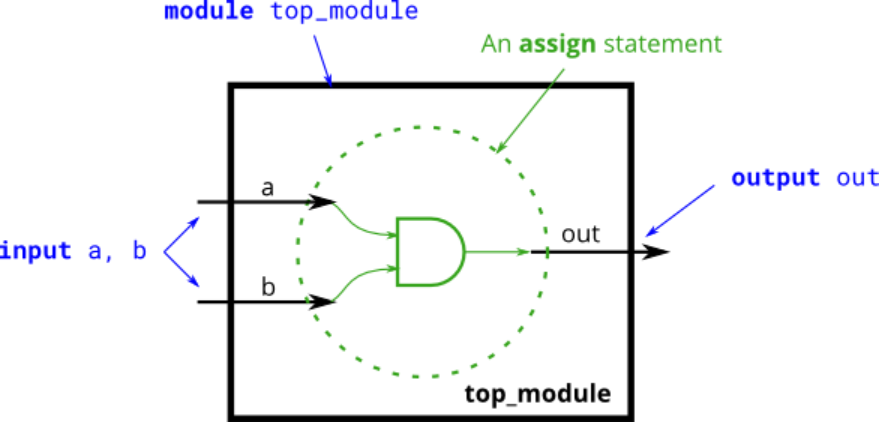

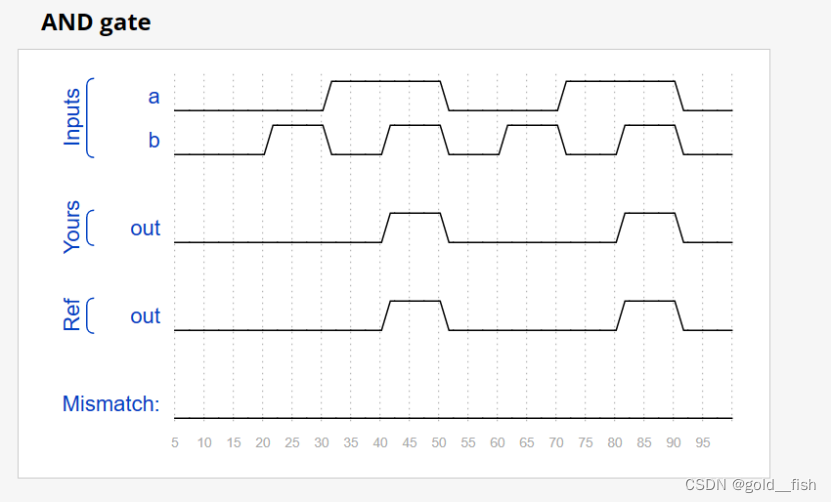

Andgate

一、题目要求

创建一个实现AND(与)门的模块。模块图如下所示

二、分析

输出与输入为逻辑与的关系,逻辑如下图真值表。逻辑与用verilog语言描述为“&”,赋值语句用assign。

| a | b | out |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

代码如下:

module top_module(

input a,

input b,

output out

);

assign out=a&b;

endmodule

三、仿真图:

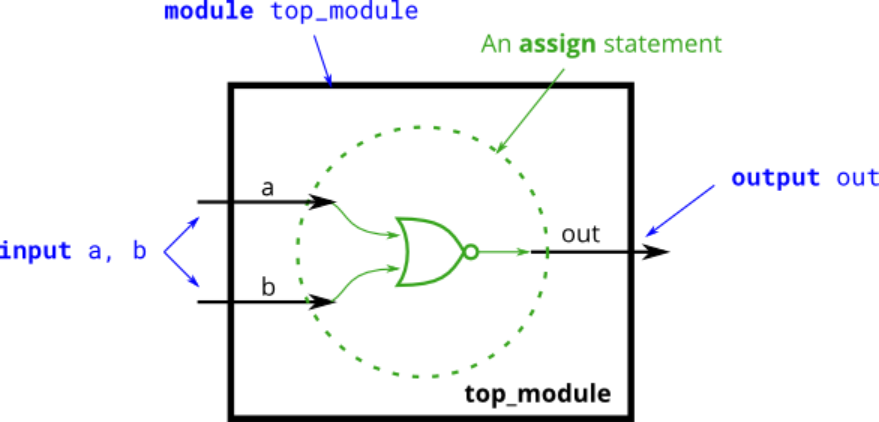

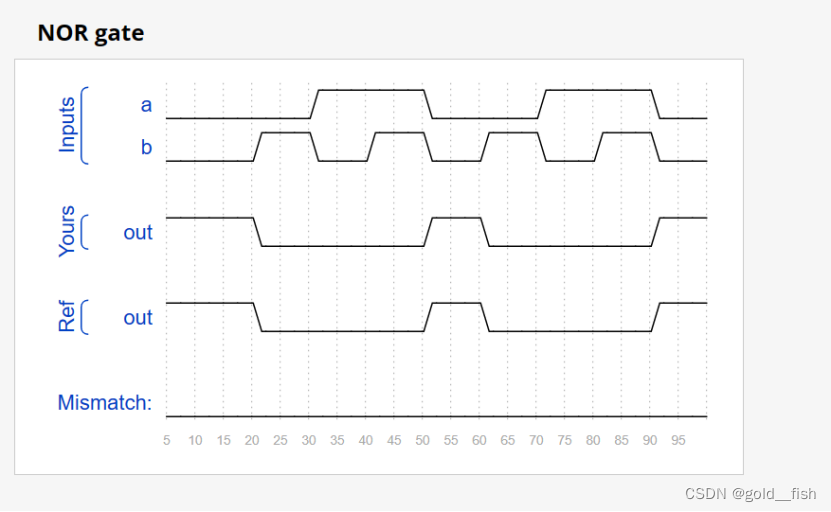

Norgate

一、题目要求

创建一个实现NOR(或非)门的模块。

二、分析

输出与输入为或非关系,逻辑如下图真值表。逻辑为先“或”后“非”,需要用到两种逻辑运算符或“|”和非“~”,赋值语句用assign。

| a | b | out |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

代码如下:

module top_module(

input a,

input b,

output out );

assign out=~(a|b);

endmodule

三、仿真图

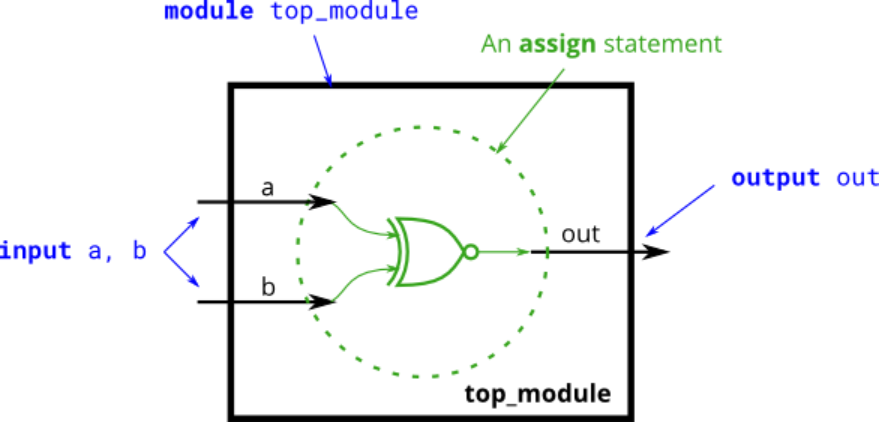

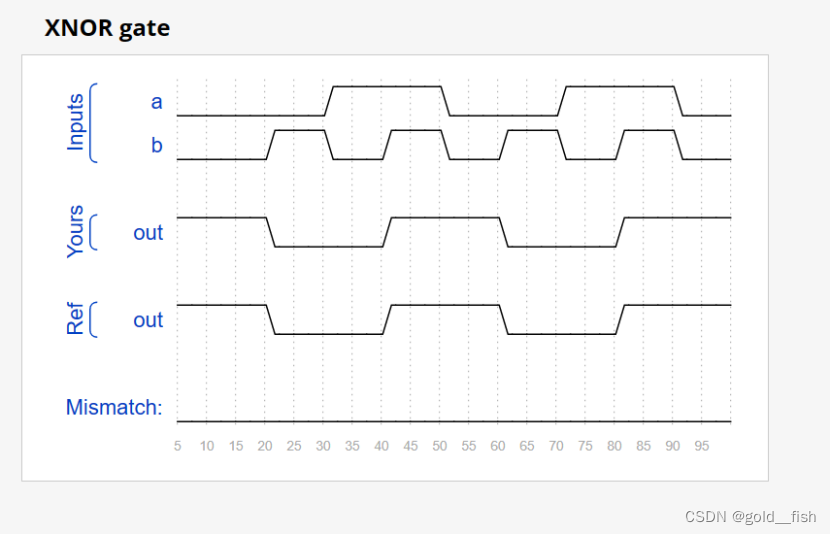

Xnorgate

一、题目要求

创建一个实现XNOR(同或,异或为xor)门的模块。模块图如下图所示

二、分析

输出跟输入为逻辑同或的关系,逻辑如下图真值表所示。异或用verilog语言描述为“^”同或跟异或为逻辑非的关系,即ab异或后取反即为同或。或者使用三目运算符a==b?a:b。赋值语句使用assign。

| a | b | out |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

代码如下(斜线注释后为三目运算符的表达式)

module top_module(

input a,

input b,

output out );

assign out=~(a^b);

//assign out=(a==b)? 1'b1:1'b0;

endmodule

三、仿真图

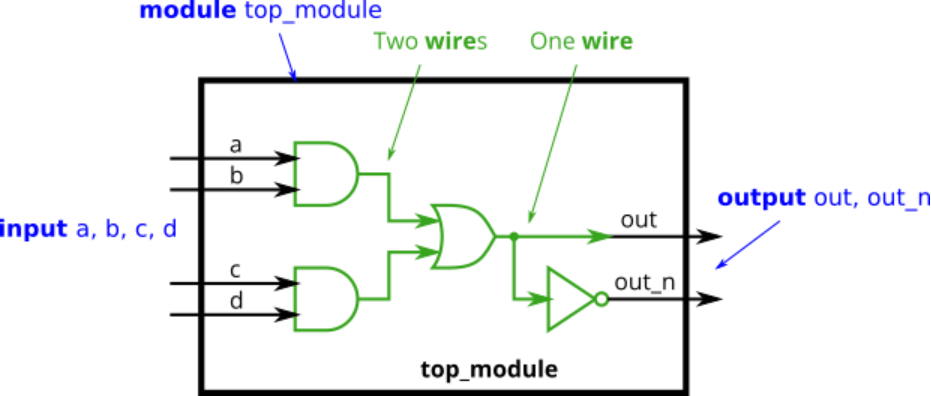

Wire decl

一、题目要求

要求使用wire类型声明语句声明三个中间变量,完成下图要求的逻辑。模块图跟逻辑关系如下图

二、分析

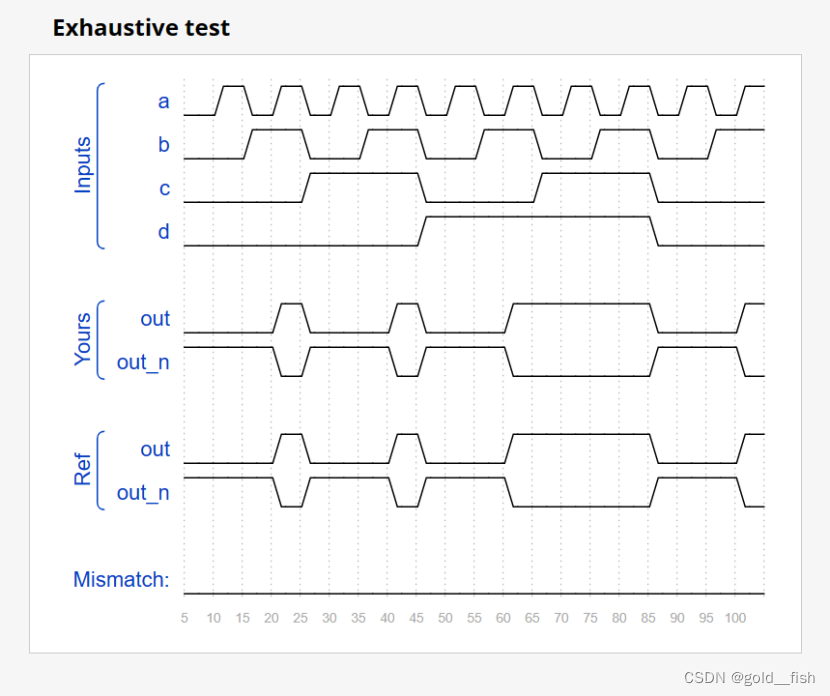

模块要求有三个wire类型的变量,不妨命名为wire1,wire2,wire3(名字可以任取),wire1保存ab相与(a&b)的结果,wire2保存cd相与(c&d)的结果,wire3保存wire1和wire2相或(wire1|wire2)的结果,然后将wire3直接赋值给out,wire3取反(~wire3)后赋值给out_n,赋值语句用assign。

代码如下

module top_module(

input a,

input b,

input c,

input d,

output out,

output out_n );

wire wire1,wire2,wire3;

assign wire1=a&b;

assign wire2=c&d;

assign wire3=wire1|wire2;

assign out=wire3;

assign out_n=~wire3;

endmodule

三、仿真图

7458

一、题目要求

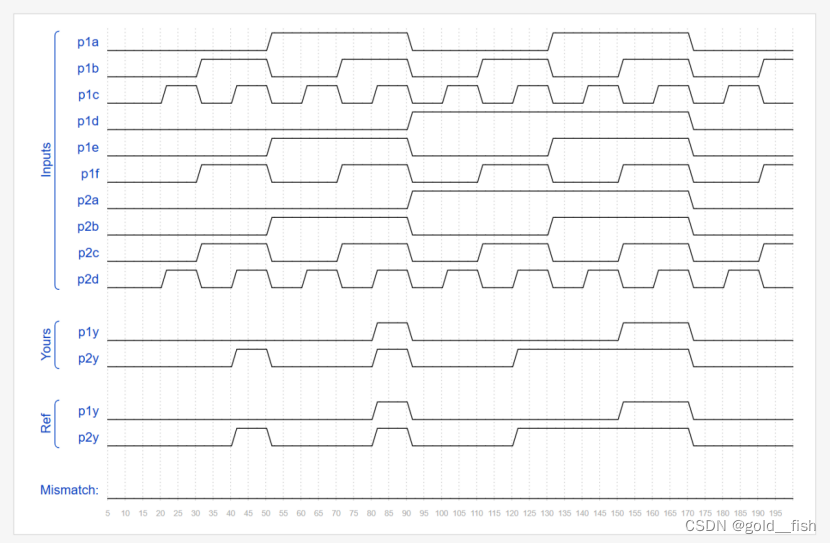

设计一个7458芯片,其内部连接跟端口要求如下图

二、分析

需要用wire声明中间变量暂存各个输入之间逻辑关系运算的结果。这里用wire1暂存p2a和p2b相与的结果,wire2暂存p2c和p2d相与的结果,wire3暂存p1a和p1c,p1d三者相与的结果,wire4暂存p1f,p1e,p1d三者相与的结果。然后将wire1和wire2相或的结果赋值给p2y,wire3和wire4相或的结果赋值给p1y。赋值语句用assign。

代码如下

module top_module (

input p1a, p1b, p1c, p1d, p1e, p1f,

output p1y,

input p2a, p2b, p2c, p2d,

output p2y );

wire wire1,wire2,wire3,wire4;

assign wire1=p2a&p2b,wire2=p2c&p2d;

assign wire3=p1a&p1b&p1c,wire4=p1d&p1e&p1f;

assign p2y=wire1|wire2,p1y=wire3|wire4;

endmodule

三、仿真图

273

273

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?