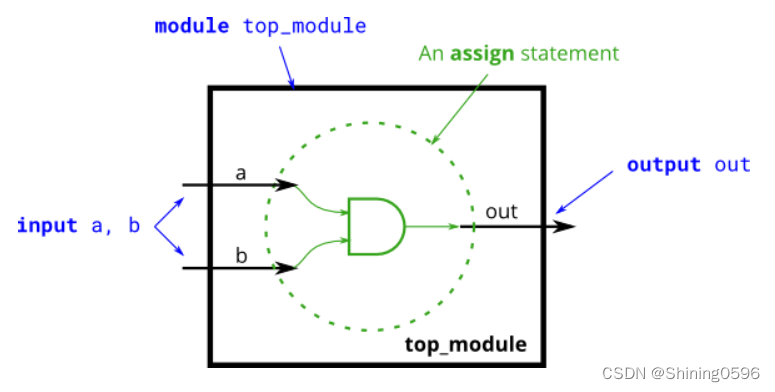

Create a module that implements an AND gate.

创建一个实现与门的模块。

This circuit now has three wires (a, b, and out). Wires a and b already have values driven onto them by the input ports. But wire out currently is not driven by anything. Write an assign statement that drives out with the AND of signals a and b.

该电路现在有三根线(a、b 和 out)。连线 a 和 b 已经有输入端口驱动到它们的值。但是目前的wire out不是由任何东西驱动的。编写一个用信号 a 和 b 的 AND 驱动的赋值语句。

Note that this circuit is very similar to the NOT gate, just with one more input. If it sounds different, it's because I've started describing signals as being driven (has a known value determined by something attached to it) or not driven by something. Input wires are driven by something outside the module. assign statements will drive a logic level onto a wire. As you might expect, a wire cannot have more than one driver (what is its logic level if there is?), and a wire that has no drivers will have an undefined value (often treated as 0 when synthesizing hardware).

请注意,该电路与非门非常相似,只是多了一个输入。如果听起来不同,那是因为我已经开始将信号描述为被驱动(具有由附加的东西决定的已知值)或不被某物驱动。输入线由模块外部的东西驱动。分配语句会将逻辑电平驱动到线路上。如您所料,一条线不能有多个驱动程序(如果有,它的逻辑级别是多少?),没有驱动程序的线将有一个未定义的值(在综合硬件时通常被视为 0)。

Module Declaration

module top_module(

input a,

input b,

output out );

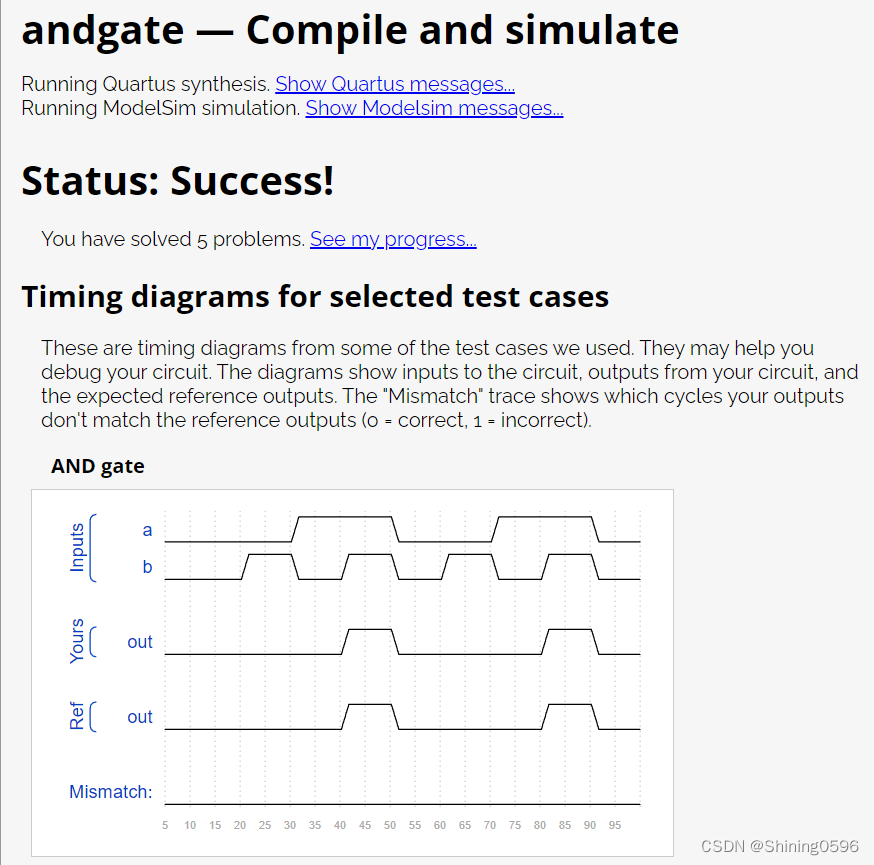

Verilog has separate bitwise-AND (&) and logical-AND (&&) operators, like C. Since we're working with a one-bit here, it doesn't matter which we choose.

Verilog 有单独的按位与 (&) 和逻辑与 (&&) 运算符,就像 C 一样。由于我们在这里使用一位,所以我们选择哪个并不重要。

module top_module(

input a,

input b,

output out );

assign out = a&&b;

endmodule

436

436

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?