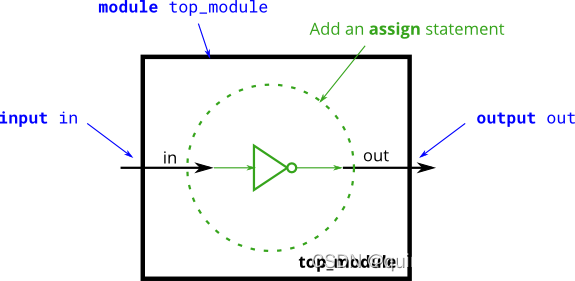

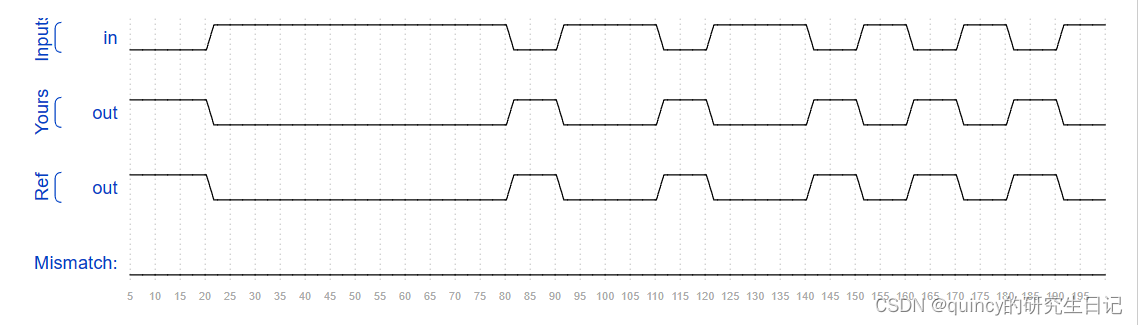

1. 非门(NOT Gate)

非门是最简单的逻辑门,它有一个输入和一个输出。非门的输出是其输入的逻辑非。如果输入为高电平(逻辑1),则输出为低电平(逻辑0);如果输入为低电平(逻辑0),则输出为高电平(逻辑1)。

Verilog代码实现:

module not_gate (

input wire in, // 输入信号

output wire out // 输出信号

);

// 使用assign语句创建一个非门

assign out = ~in;

endmodule

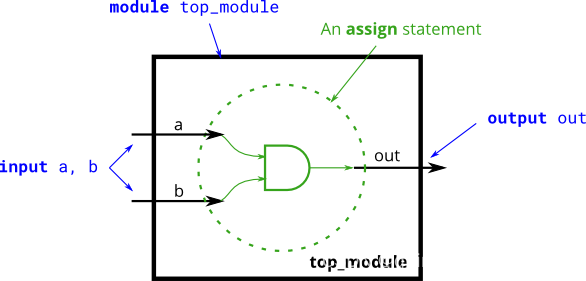

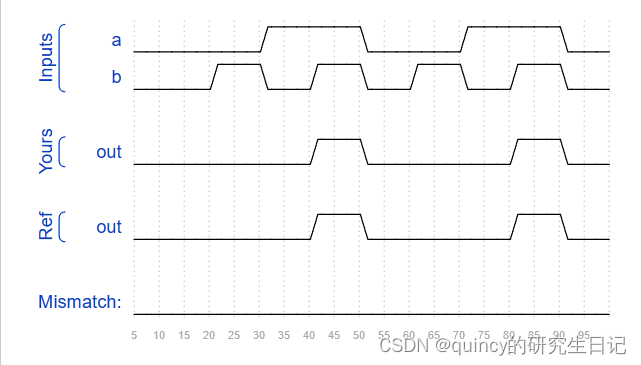

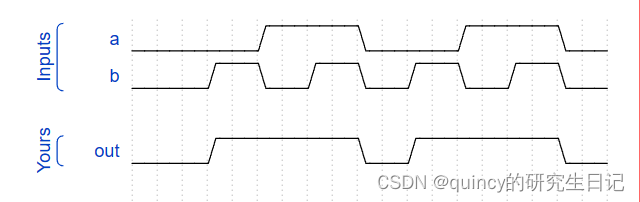

2. 与门(AND Gate)

与门有两个或更多的输入和一个输出。与门的输出是其所有输入的逻辑与。只有当所有输入都是高电平时,输出才是高电平;否则,输出为低电平。

Verilog代码实现:

module and_gate (

input wire a, // 第一个输入信号

input wire b, // 第二个输入信号

output wire out // 输出信号

);

// 使用assign语句创建一个与门

assign out = a & b;

endmodule

3. 或门(OR Gate)

或门有两个或更多的输入和一个输出。或门的输出是其所有输入的逻辑或。只要有一个输入是高电平,输出就是高电平;只有当所有输入都是低电平时,输出才是低电平。

Verilog代码实现:

module or_gate (

input wire a, // 第一个输入信号

input wire b, // 第二个输入信号

output wire out // 输出信号

);

// 使用assign语句创建一个或门

assign out = a | b;

endmodule

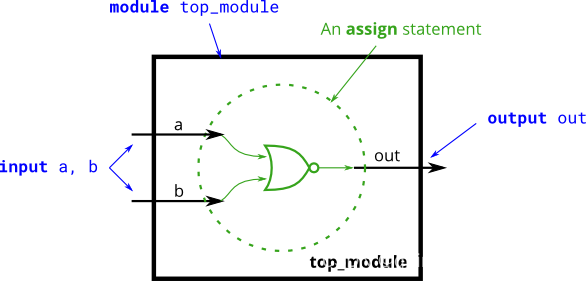

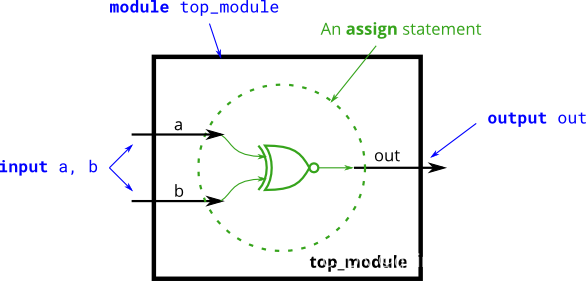

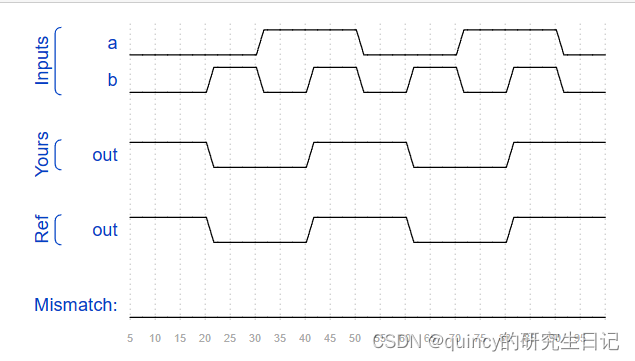

4. 或非门(NOR Gate)

或非门(NOR Gate)是逻辑或门(OR Gate)的输出经过非门(NOT Gate)的结果。在Verilog中,您可以使用assign语句来定义或非逻辑。下面是一个简单的例子,展示了如何创建一个两输入的或非门:

Verilog代码实现:

module nor_gate (

input wire a, // 第一个输入信号

input wire b, // 第二个输入信号

output wire out // 输出信号

);

// 使用assign语句创建一个或非门

// 或非逻辑是输入的逻辑或的结果取反

assign out = ~(a | b);

endmodule

5. 异或非门(XNOR Gate)

异或非门是异或门(XOR Gate)的输出经过非门的结果。异或门有两个输入,其输出是输入的逻辑异或。如果输入信号相同(都是高电平或都是低电平),则输出为高电平;如果输入信号不同,则输出为低电平。异或非门则将这个输出再取反。

Verilog代码实现:

module xnor_gate (

input wire a, // 第一个输入信号

input wire b, // 第二个输入信号

output wire out // 输出信号

);

// 使用assign语句创建一个异或非门

// 异或非逻辑是输入的异或结果取反

assign out = ~(a ^ b);

endmodule

在编写Verilog代码时,您可以将这些基本逻辑门组合起来,形成更复杂的数字电路。每个模块都可以作为一个独立的单元,通过输入输出端口与其他模块连接。通过这种方式,您可以构建从简单的逻辑电路到复杂的数字系统的一切。

769

769

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?