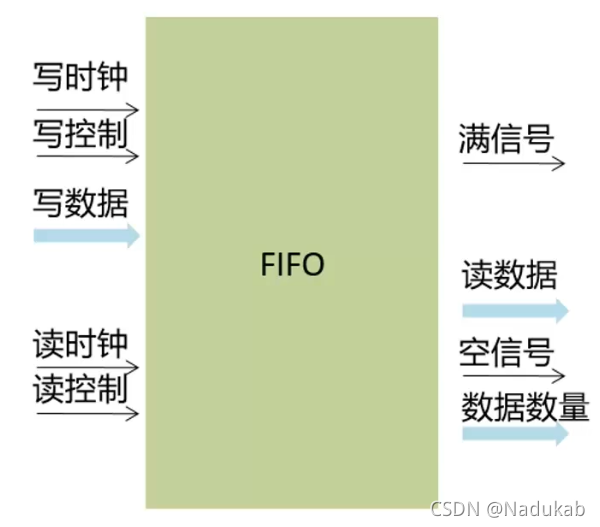

FIFO存储器是系统的缓冲环节,如果没有FIFO存储器,整个系统就不可能正常工作,它主要有几方面的功能:

1)对连续的数据流进行缓存,防止在进机和存储操作时丢失数据;

2)数据集中起来进行进栈和存储,可避免频繁的总线操作,减轻CPU的负担;

3)允许系统进行DMA操作,提高数据的传输速度。这是至关重要的一点,如果不采用DMA操作,数据传输将达不到传输要求,而且大大增加CPU的负担,无法同时完成数据的存储工作。

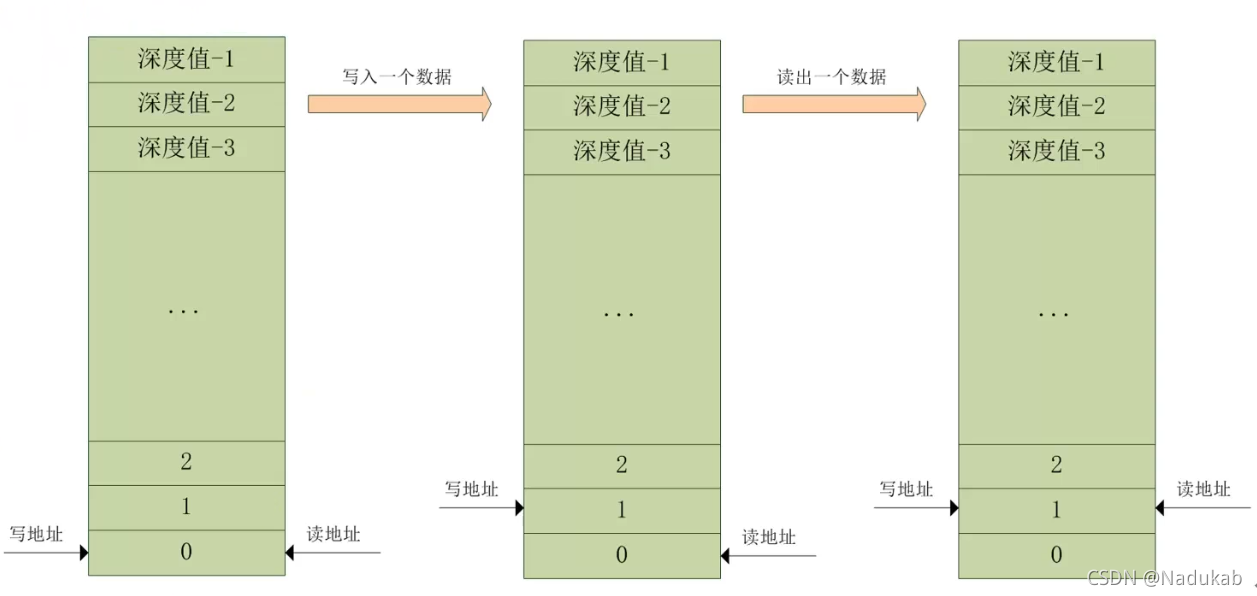

针对FIFO里面用到的Ram

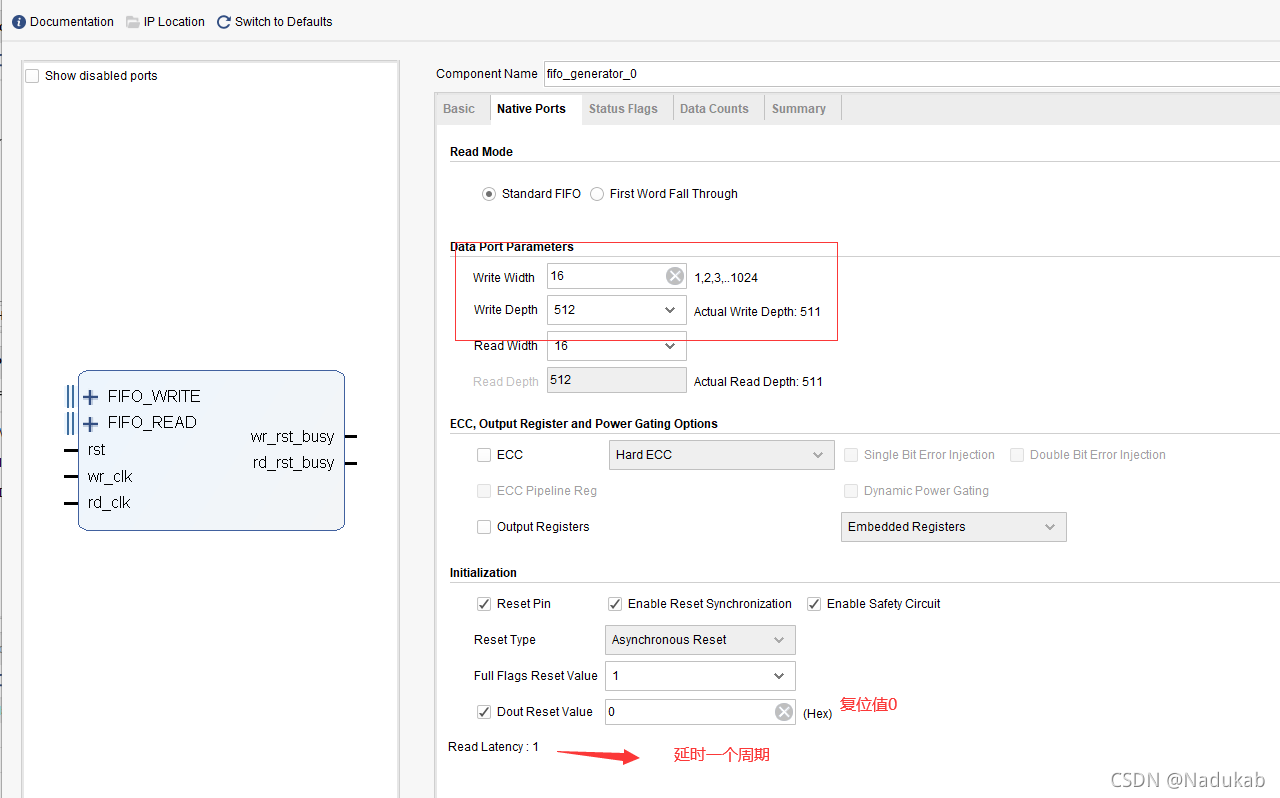

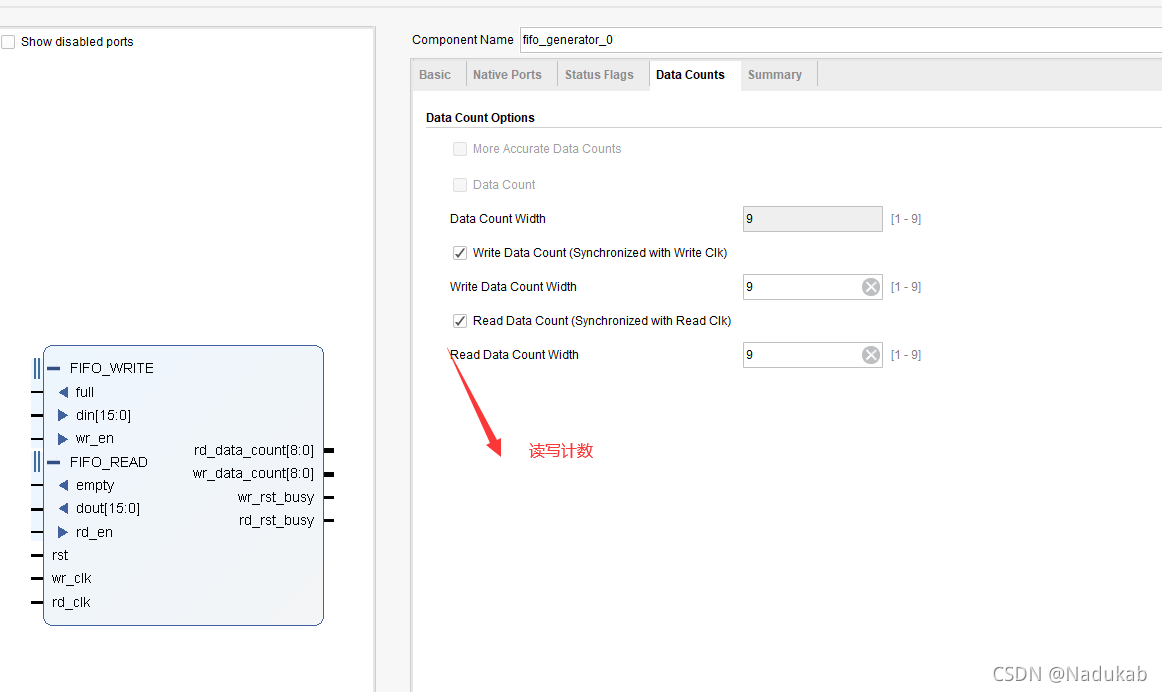

同样vivado新建设计文件,搜索fifo IP核,双击fifo_generator进行设置。

Common clock表示读写同步时钟,independent表示异步时钟。我们选择异步时钟ram

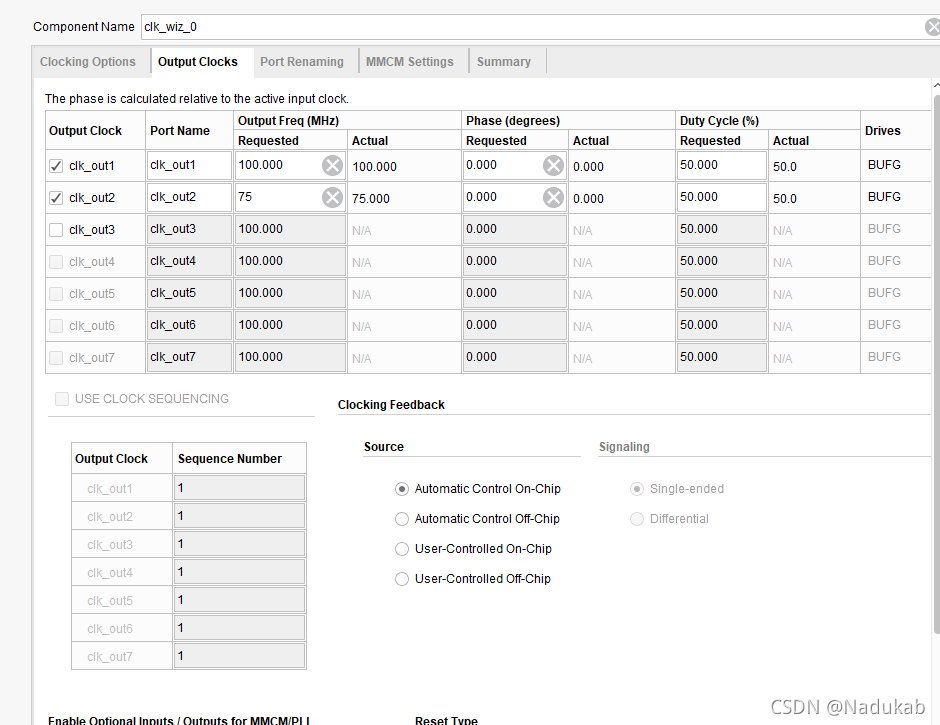

然后在锁相环里面设置,写的时钟比读的时钟快。

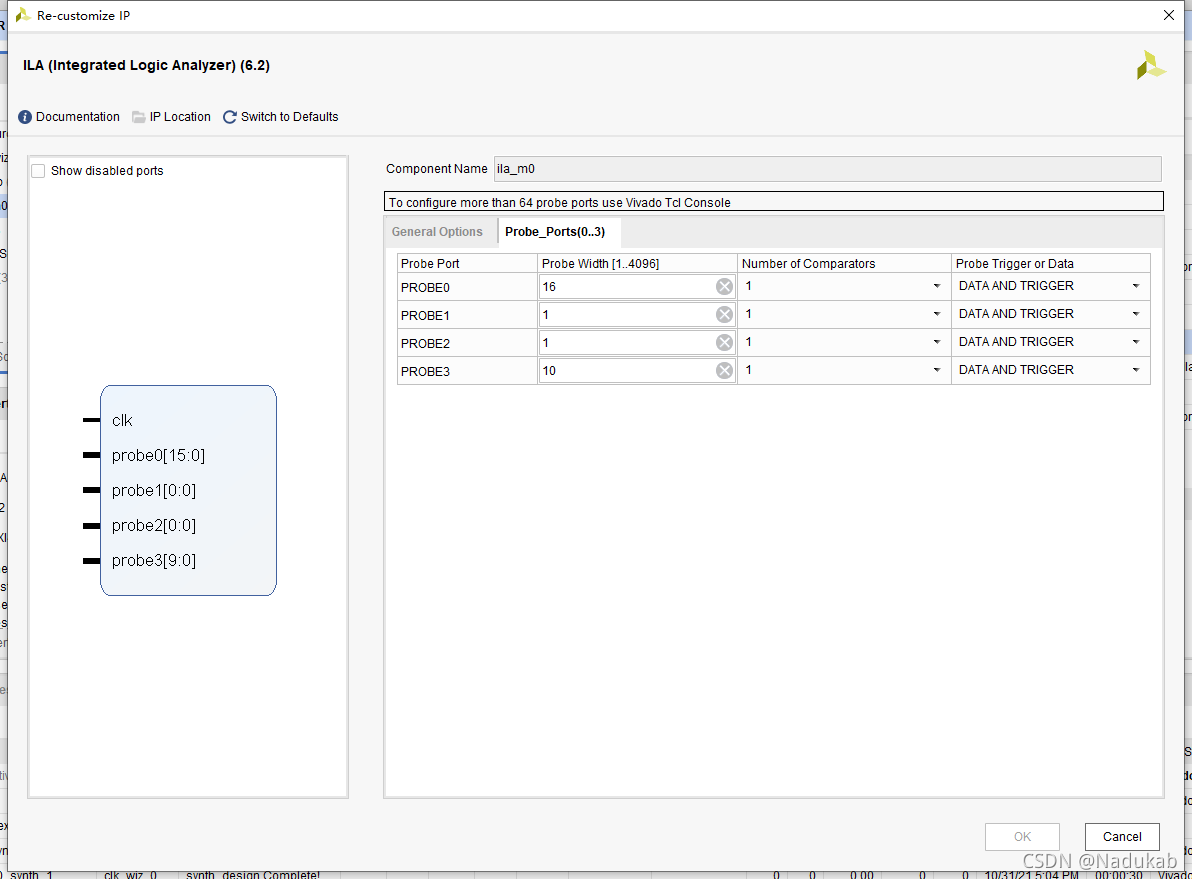

再创建逻辑分析仪 :

添加source文件,拷贝代码:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

module fifo_test

(

input clk,

本文介绍了FPGA中FIFO存储器的重要作用,如数据缓存、减轻CPU负担和提高DMA操作效率。通过Vivado设计流程,详细讲解了如何配置异步时钟的RAM型FIFO,并进行了仿真验证。最后,讨论了FIFO的不同工作模式对实际应用的影响。

本文介绍了FPGA中FIFO存储器的重要作用,如数据缓存、减轻CPU负担和提高DMA操作效率。通过Vivado设计流程,详细讲解了如何配置异步时钟的RAM型FIFO,并进行了仿真验证。最后,讨论了FIFO的不同工作模式对实际应用的影响。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1453

1453

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?