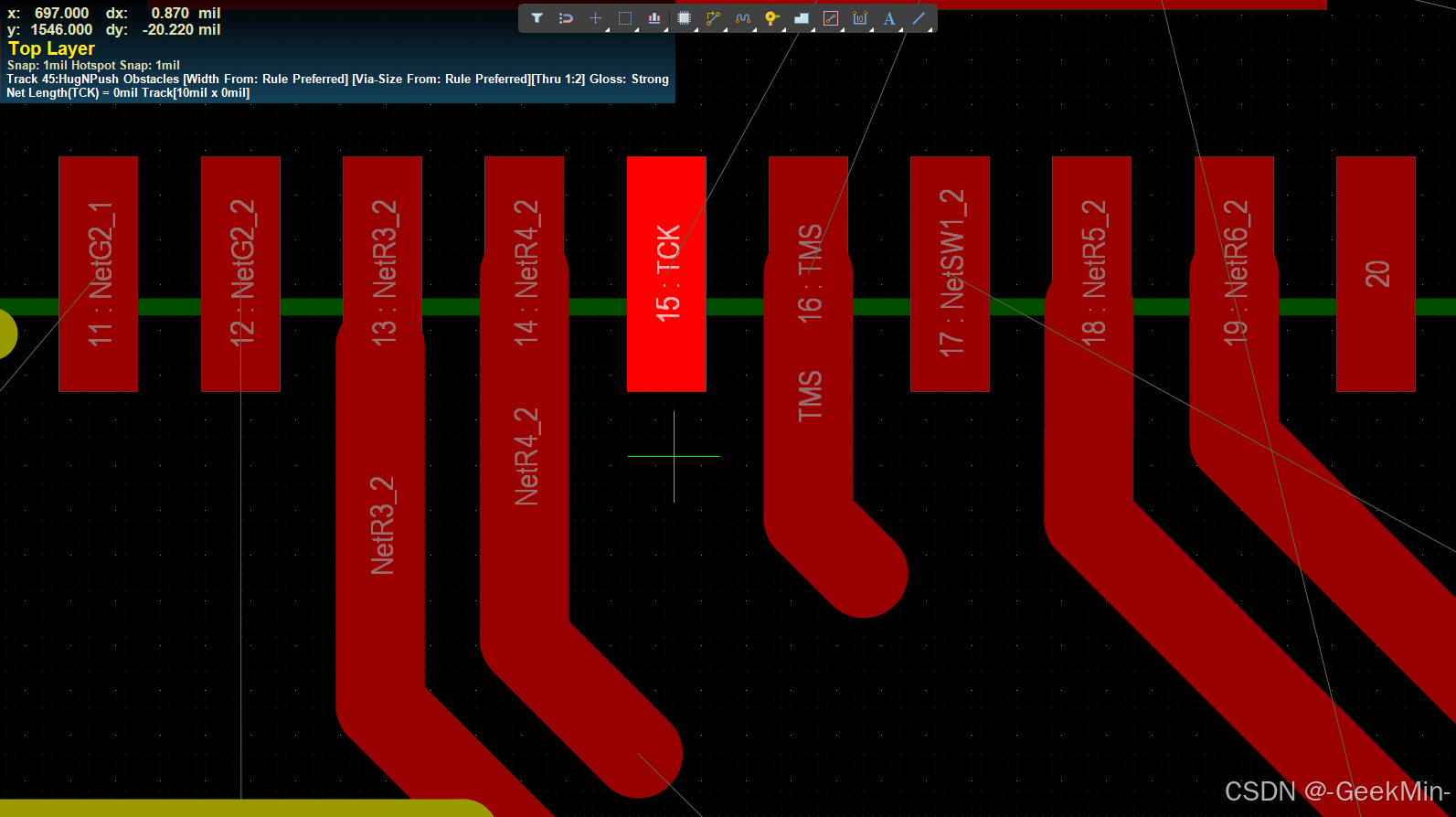

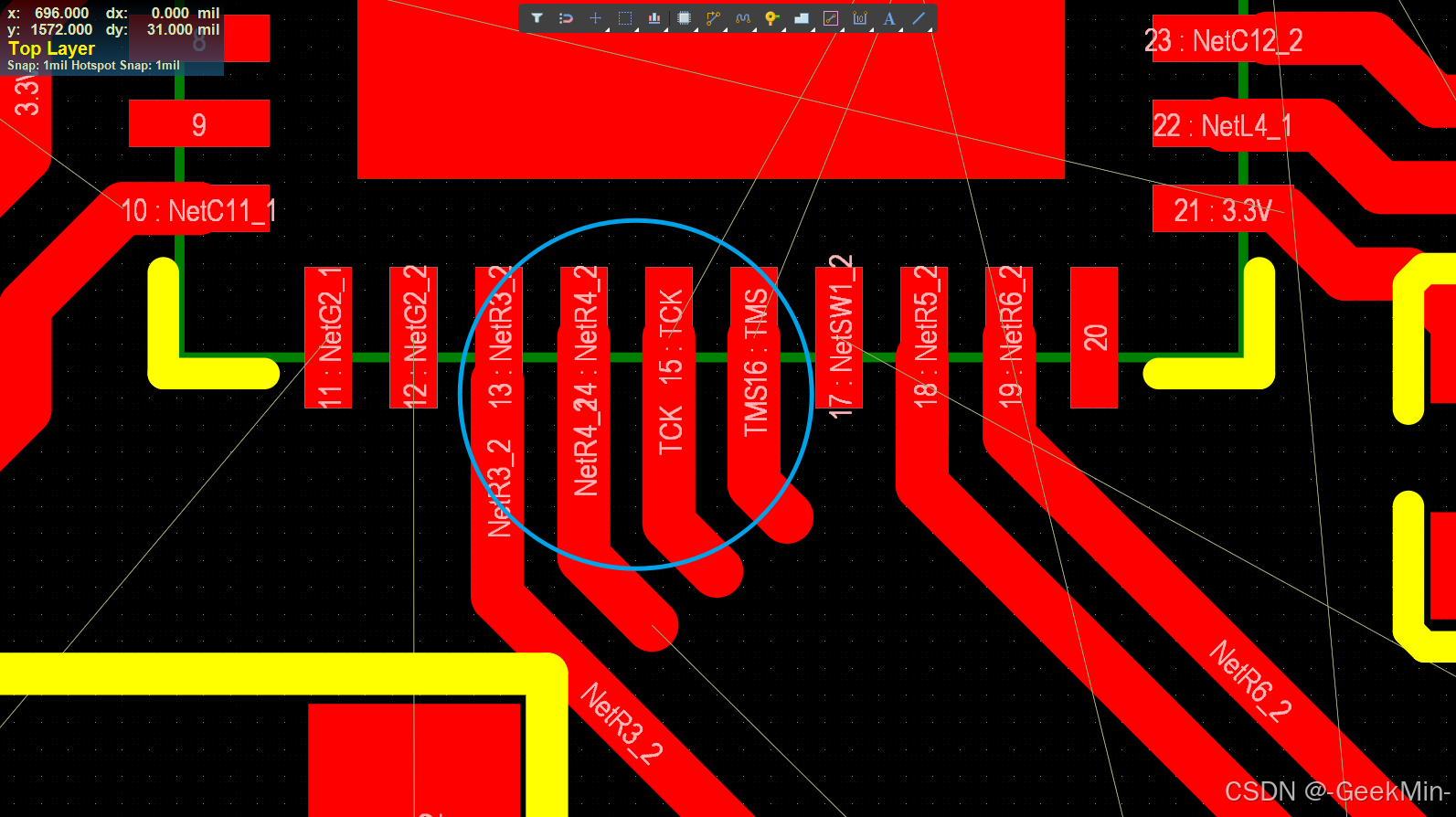

在画板子时发现选中了芯片引脚,但是拉不出线来,如下图所示:

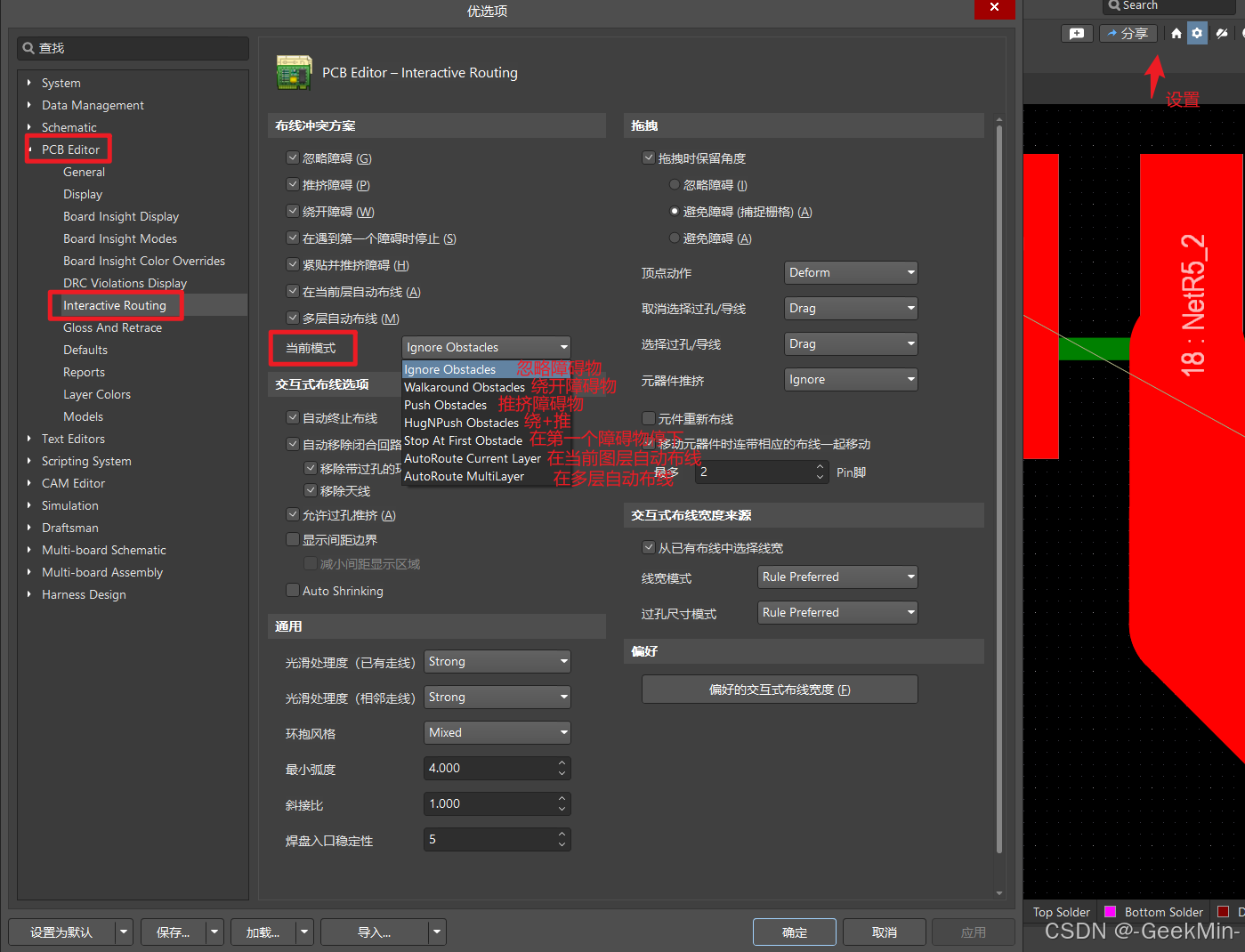

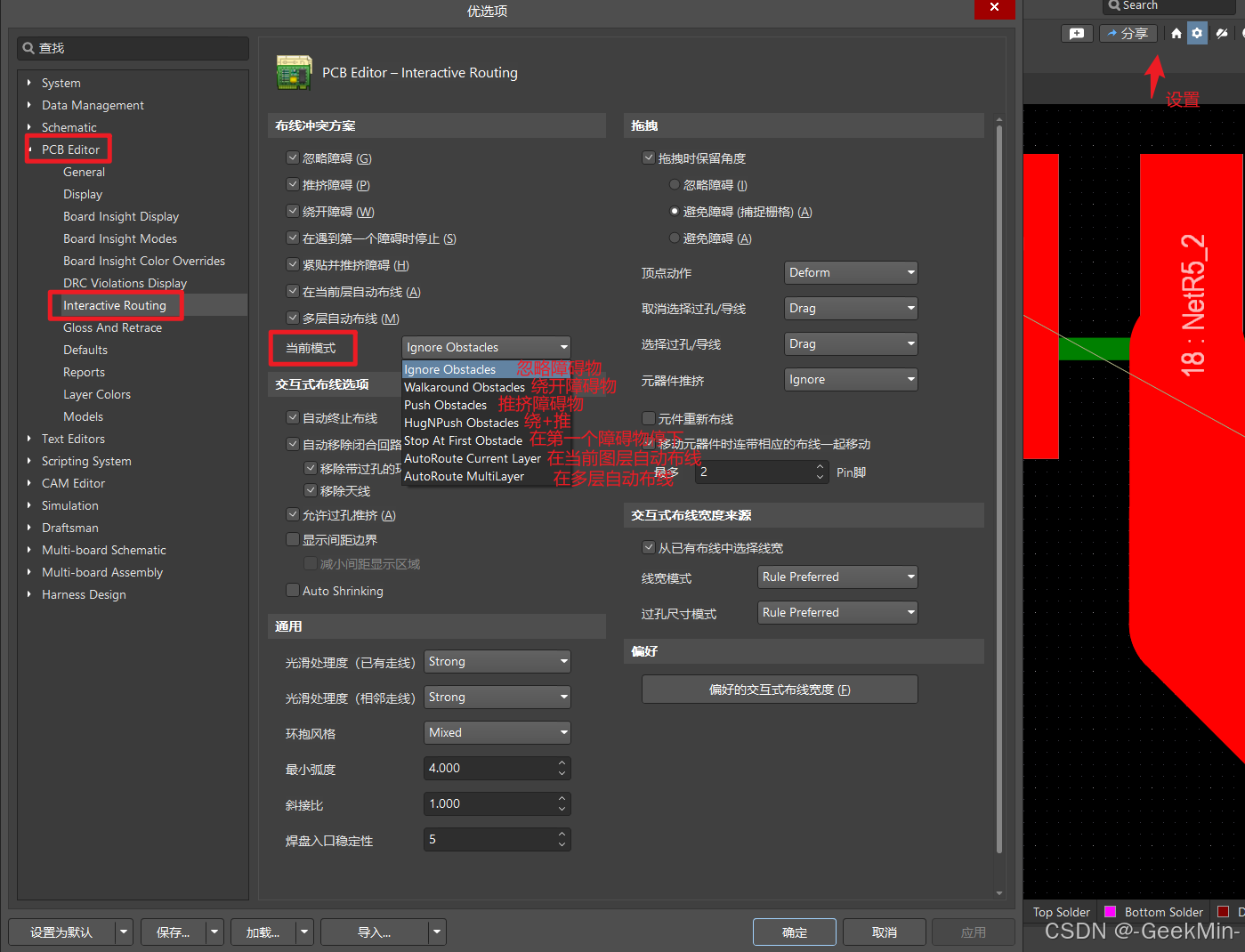

经过几番折腾,发现应该是设置上的问题,设置了hugNpush obstacle布线模式,其结合了Walkaround(绕开障碍物)+Push(推挤障碍物)功能,确保不违反规则。

发现了问题就好解决了。

有两种办法,第一种是更改规则,比如线宽。

第二种就是更改布线模式,更改未忽略障碍物,布线后可以自己调整,使间距满足要求,我更倾向于第二种。

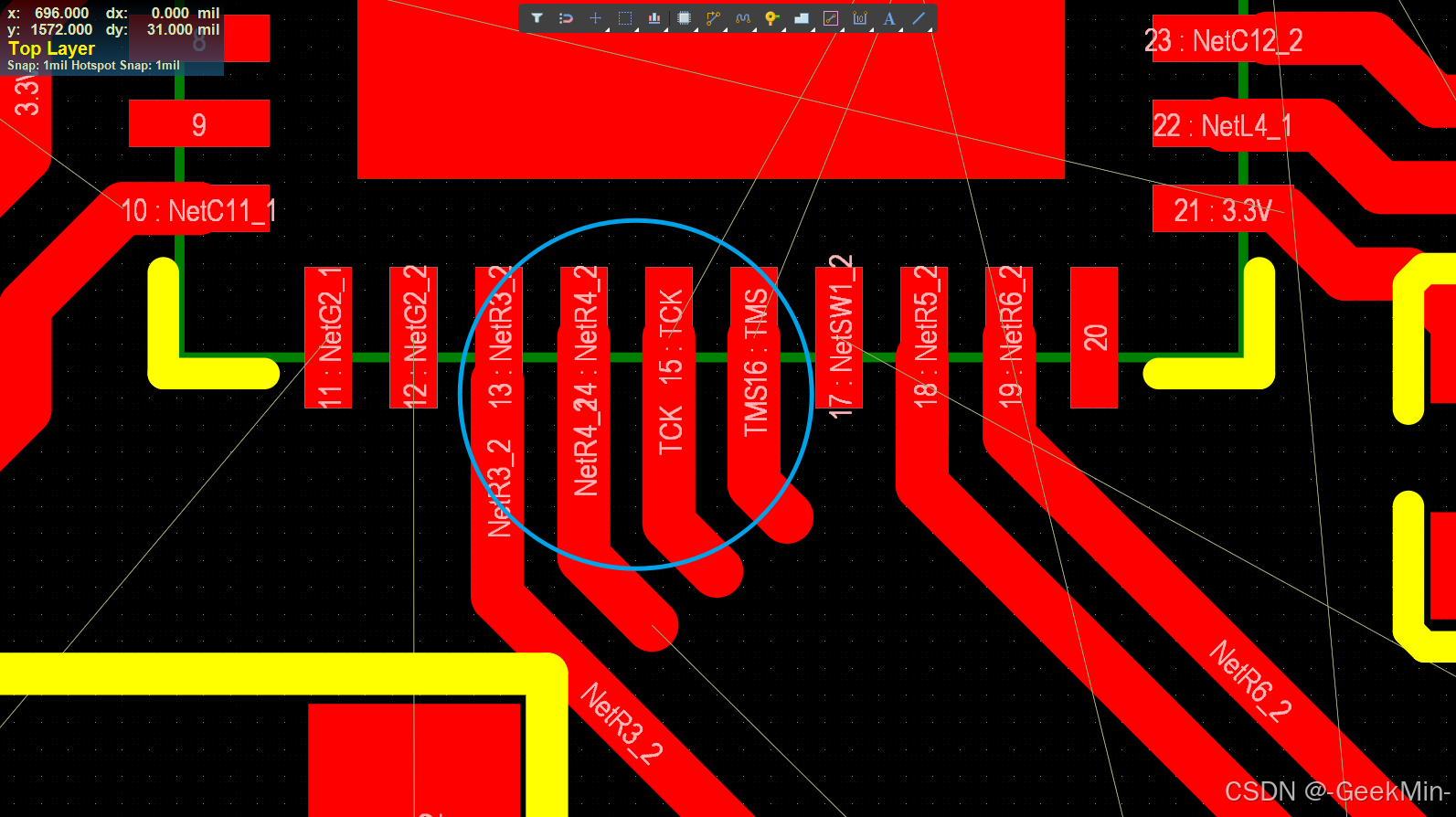

最后可以布出来啦,并且经过线间距调整,也不会报DRC错误~

在画板子时发现选中了芯片引脚,但是拉不出线来,如下图所示:

经过几番折腾,发现应该是设置上的问题,设置了hugNpush obstacle布线模式,其结合了Walkaround(绕开障碍物)+Push(推挤障碍物)功能,确保不违反规则。

发现了问题就好解决了。

有两种办法,第一种是更改规则,比如线宽。

第二种就是更改布线模式,更改未忽略障碍物,布线后可以自己调整,使间距满足要求,我更倾向于第二种。

最后可以布出来啦,并且经过线间距调整,也不会报DRC错误~

2294

2294

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?