数字设计综述:

典型的设计流程:表示超大规模集成电路设计的典型流程。图中不带阴影表示设计描述的层次。带阴影的表示设计的过程。

数字电路中两种基本设计方法:自顶向下和自底向上。

仿真两个不同组合部分:设计块和激励块,激励块用于测试设计块,激励块通常是顶层模块。

verilog语法介绍:

一、词法约定

模块:

module <模块名>(端口列表);

...

<模块内容>

...

endmodulemodule T_FF(input in,output out)

assign out = in;

endmodule注释

/*多行

注释*/

/*单行注释*/操作符

a = ~b;//~是单目操作符、b是操作数。单目操作符优先级高于操作数

a = b && c;//&&是双目操作符,b和c是操作数

a = b ? c :d//?:是三目操作符,b、c和d是操作数,b为1选c数字声明

指明位数的数字:<位数>'<进制><数字>

4'b1111 //4位的二进制数

/*十进制d、十六进制h、二进制b、八进制o*/不指明位数的数字:没有说明进制则默认十进制数,没有指定位宽则默认计算机位宽(如32位或64位)

23456 //32位的十进制数

'hc3 //32位的十六进制数

'o21 //32位的八进制数X值和Z值:不确定值用X表示;高阻值用Z表示。十六进制中x或z表示4位;八进制表示3位;二进制中表示1位。

12'h13x //12位的16进制数,4个低位不确定

6'hx //6位的16进制数,所有位不确定

32'bz //32位的高阻值负数:在位宽前添加负号表示负数

-6'd3 //6位的十进制数3,负数_和?:_用来提升可读性,?是z的另一种表示

12'b1111_0000

4'b10?? //相当于4'b10zz字符串

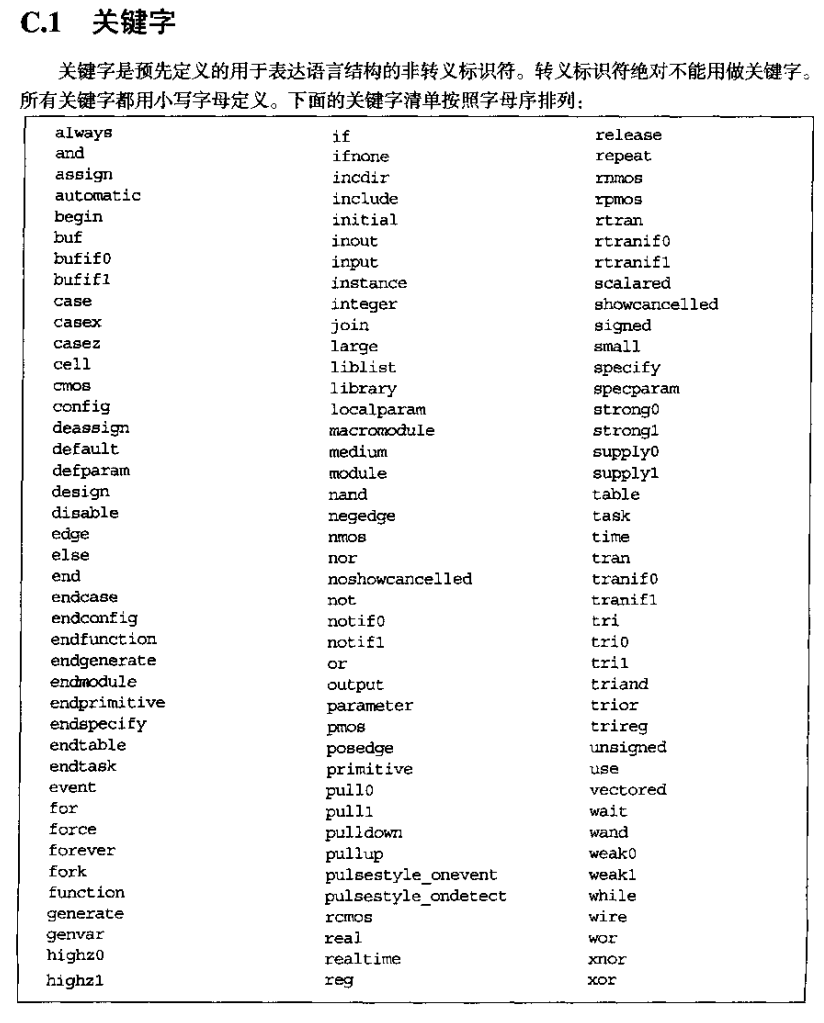

“hello world” //是一个字符串标识符和关键字

标识符由字母、数字、下划线和$组成。标识符第一个字符必须是字母或下划线。

转义标识符:以\开始,以空白符结束。

\a+b-c //与a+b-c等同二、数据类型

值的种类

线网:wire声明最为常用

寄存器:表示存储元件,保持原有数值,直到被改写。一般用reg进行声明。

向量:[high:low]或[low:high]进行说明,方括号中的左边总是表示向量的最高有效位。

wire [7:0] busA //8位总线

busA[7] //向量busA中的第7位

bus[2:0] //向量bus的低3位

buty = busA[7-,2] //从第7位算起,位宽为2,相当于busA[7:6]

buty = busA[2+,2] //从第2位算起,位宽为2,相当于busA[3:2]整数、实数和时间寄存器数据类型

整数:关键字integer

实数:实常量和实数寄存器数据类型使用关键字real声明,可以用十进制或科学计数法。

时间寄存器:关键字time。通过调用系统函数$time可以得到当前的仿真时间。仿真单位时间为s秒。

real delta;

intial

begin

delta = 4e10; //delta被赋值,用科学计数法表示

delta = 2.13; //delta被赋值为2.13

end

integer i; //i为整数型变量

intial

i = delta; //i得到值2(2.13取整数部分)

time save_time; //定义时间类型的变量save_time

initial

save_time = $time; //把当前的仿真时间记录下来数组:数组由多个元件构成,其中每个元件的位宽为n或1;向量由一个元件构成,位宽为n或1。

wire [7:0] a; //向量

wire [7:0] c; //一维数组

wire b [7:0][4:0] //二维数组存储器:使用寄存器的一维数组表示存储器。

reg memory [0:1023] // 1k的1位存储器

reg [7:0] membyte [0:1023] //1k的字节(8位)存储器参数:代表常数,不能赋值

parameter id = 5 ;//定义常数id为5,可在编译过程中被更改

localparam state = 4'b0001; //局部参数使用关键字localparam定义,不能被改变字符串

三、系统任务和编译指令

系统任务:所有系统任务都有$<keyword>形式。

$display:用于显示变量、字符串和表达式。

$display("hello")

--hello

$display("id = %b",id)

--id = 1'b1

$monitor:监视信息,提供了对信号值变化的监视作用。

initial

begin

$monitor($time,"value = %b,reset = %b",clock,reset);

end

-- value = 0,reseet =1

-- value = 1,reseet =1

-- value = 0,reseet =0$stop:暂停仿真

$finish:结束仿真

#50 $stop

#100 $finish编译指令

`define:定义。

`define word_size 32 //定义字长

`define s $stop //定义别名,用s代替$stop

`define word reg[31:0] //用word定义一个32位的寄存器`include:将一个verilog源文件包含在另一个verilog文件中。

`include header.v

8154

8154

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?