题目一:

vlg_design.v

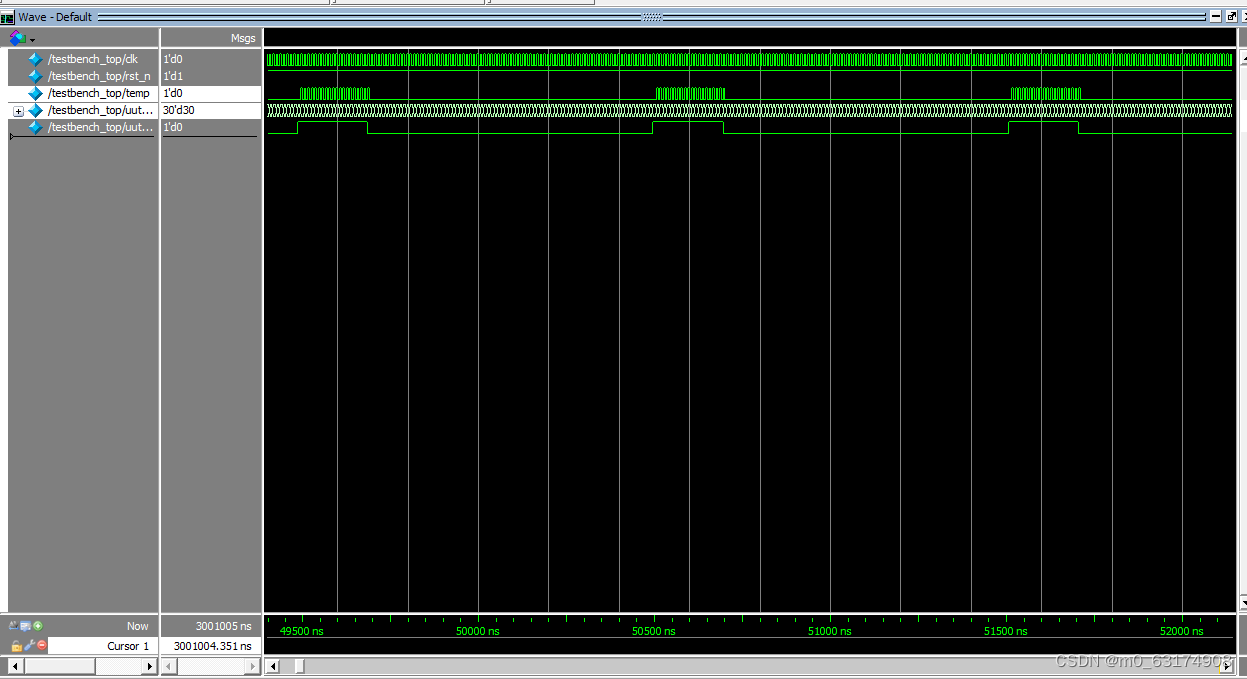

`timescale 1ns/1ps

module vlg_design(

input clk, //100MHz

input rst_n,

output temp

);

/

//

//可以通过宏定义,来改变条件

`define SIMULATION

`ifdef SIMULATION

localparam max_count = 30'd10000-1'b1; // 1S

localparam max_count_10 = 30'd100-1'b1; // 10MS

localparam max_count_2 = 30'd20-1'b1; // 2MS

`else

localparam max_count = 30'd100_000_000-1'b1; // 1s计数的最大值

localparam max_count_10 = 30'd1_000_000-1'b1; // 10ms计数的最大值

localparam max_count_2 = 30'd200_000-1'b1; // 2MS

`endif

reg[29:0] cnt;

always @(posedge clk) begin

if(!rst_n) cnt<=0;

else if(cnt<=max_count_10) cnt<=cnt+1'b1;

else cnt<=1'b0;

end

reg en_10ms;

always @(posedge clk)begin

if(!rst_n) begin

en_10ms<=1'd0;

cnt<=1'b0;

end

else if(cnt<=max_count_2) begin

en_10ms<=1'b1;

end

else en_10ms<=1'b0;

end

//

BUFGCE BUFGCE_inst (

.O(temp), // 1-bit output: Clock output

.CE(en_10ms), // 1-bit input: Clock enable input for I0

.I(clk) // 1-bit input: Primary clock

);

endmoduletestbench_top.v

`timescale 1ns/1ps

module testbench_top();

//参数定义

`define CLK_PERIORD 10 //时钟周期设置为10ns(100MHz)

//接口申明

reg clk;

reg rst_n;

wire temp;

//对被测试的设计进行例化

vlg_design uut_vlg_design(

.clk(clk),

.rst_n(rst_n),

.temp(temp)

);

//复位和时钟产生

//时钟和复位初始化、复位产生

initial begin

clk <= 0;

rst_n <= 0;

#1000;

rst_n <= 1;

end

//时钟产生

always #(`CLK_PERIORD/2) clk = ~clk;

//测试激励产生

initial begin

@(posedge rst_n); //等待复位完成

@(posedge clk);

#3_000_000; //仿真3秒钟

/*repeat(300000) begin

@(posedge clk);

end

*/

$stop;

end

endmodule题目二:

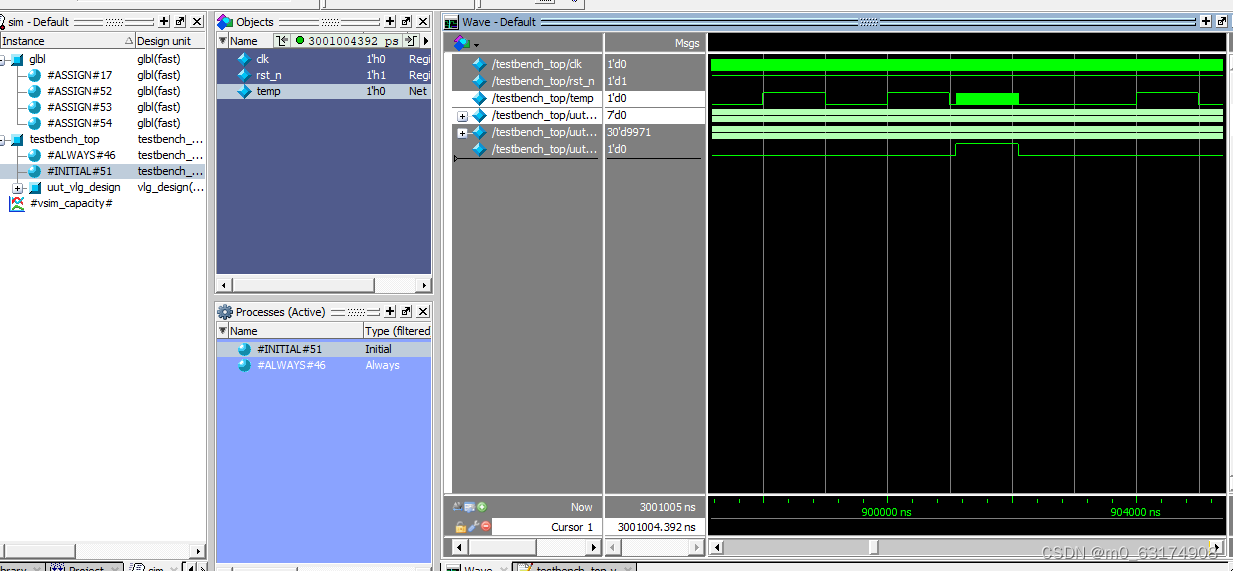

`timescale 1ns/1ps

module vlg_design(

input clk, //100MHz,定义clk为快时钟

input rst_n,

output temp

);

/

//

//首先,定义一个慢时钟

reg clk_slow;

reg [6:0] count_slow;

always @(posedge clk) begin

if(!rst_n) count_slow<=1'd0;

else if(count_slow == 7'd99) count_slow <= 1'd0;

else count_slow <= count_slow + 1'b1;

end

always @(posedge clk) begin

if(!rst_n) begin

count_slow<=1'd0;

clk_slow<=1'b0;

end

else if(count_slow == 7'd99) clk_slow <= ~clk_slow;

end

//可以通过宏定义,来改变条件

`define SIMULATION

`ifdef SIMULATION

localparam max_count = 30'd10000-1'b1; // 1S

localparam max_count_10 = 30'd100-1'b1; // 10MS

localparam max_count_2 = 30'd20-1'b1; // 2MS

`else

localparam max_count = 30'd100_000_000-1'b1; // 1s计数的最大值

localparam max_count_10 = 30'd1_000_000-1'b1; // 10ms计数的最大值

localparam max_count_2 = 30'd200_000-1'b1; // 2MS

`endif

reg[29:0] cnt;

always @(posedge clk) begin

if(!rst_n) cnt<=0;

else if(cnt<=max_count) cnt<=cnt+1'b1; // 1S的周期进行计数

else cnt<=1'b0;

end

reg en_10ms;

always @(posedge clk)begin

if(!rst_n) begin

en_10ms<=1'd0;

cnt<=1'b0;

end

else if(cnt<=max_count_10) begin

en_10ms<=1'b1;

end

else en_10ms<=1'b0;

end

//

BUFGMUX BUFGMUX_inst (

.O(temp), // 1-bit output: Clock output

.I0(clk_slow), // 1-bit input: Clock input (S=0)

.I1(clk), // 1-bit input: Clock input (S=1)

.S(en_10ms) // 1-bit input: Clock select

);

endmoduletestbench_top.v与题目一一样!

830

830

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?