vlg_design.v

`timescale 1ns/1ps

module vlg_design(

input i_clk,

input i_rst_n,

output [3:0] o_cnt1,o_cnt2

);

/

//创建一个递增的计数器

reg[3:0] count;

//创建寄存器一及寄存器二

reg[3:0] r_cnt1,r_cnt2;

always @(posedge i_clk) begin

if(!i_rst_n) begin

count<=1'b0;

r_cnt1<=0;

r_cnt2<=0;

end

else begin

count<=count+1'b1;

r_cnt1<=count;

r_cnt2<=r_cnt1;

end

end

assign o_cnt1= r_cnt1;

assign o_cnt2= r_cnt2;

endmoduletestbench_top.v

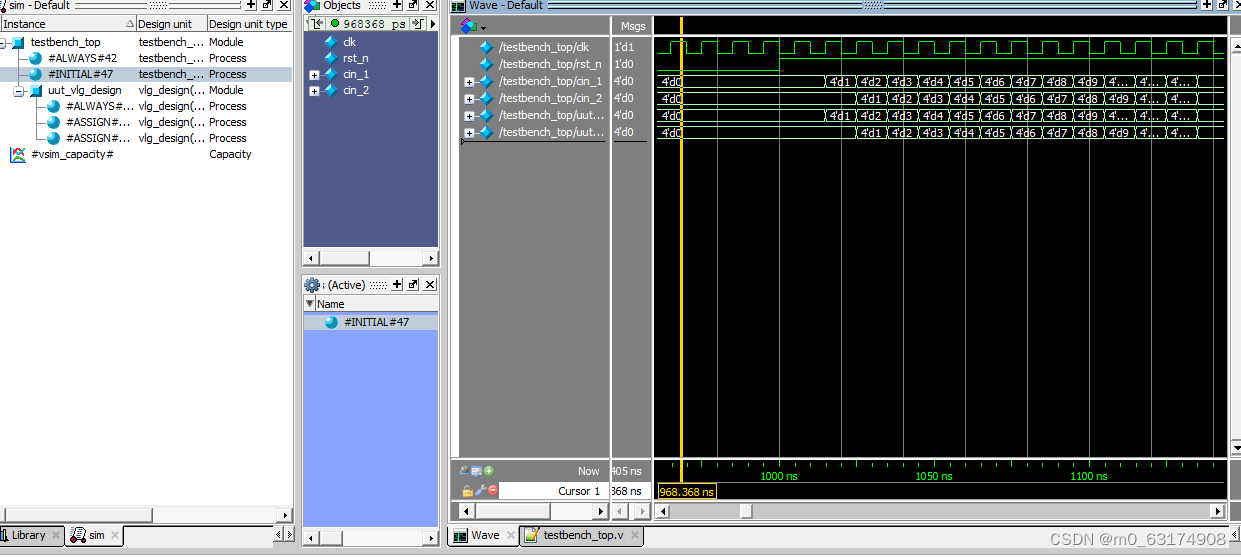

`timescale 1ns/1ps

module testbench_top();

//参数定义

`define CLK_PERIORD 10 //时钟周期设置为10ns(100MHz)

//接口申明

reg clk;

reg rst_n;

wire[3:0] cin_1,cin_2;

//对被测试的设计进行例化

vlg_design uut_vlg_design(

.i_clk(clk),

.i_rst_n(rst_n),

.o_cnt1(cin_1),

.o_cnt2(cin_2)

);

//复位和时钟产生

//时钟和复位初始化、复位产生

initial begin

clk <= 0;

rst_n <= 0;

#1000;

rst_n <= 1;

end

//时钟产生

always #(`CLK_PERIORD/2) clk = ~clk;

//测试激励产生

initial begin

@(posedge rst_n); //等待复位完成

@(posedge clk);

repeat(20*16*2) begin

@(posedge clk);

end

$stop;

end

endmodule

813

813

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?