对电路网表转换为图的结构,进而使其能够进行更多的优化算法操作,对于EDA是十分重要的。

如今电子设计自动化(EDA)是应对大规模集成电路设计的挑战的关键领域。

它确保可扩展性、可靠性,并提高研发效率。然而,EDA方法通常需要时间和资源,且无法保证最优解。为了解决这些问题,机器学习(ML)已被纳入设计流程中的多个阶段,例如布局(placement)和布线(routing)。

然而,许多方法忽略了EDA问题中的许多对象,这些对象可以自然地表示为图(graph)。图神经网络(GNN)提供了直接使用电路、中间RTL(寄存器转换级电路Register Transfer Level)和网表(netlist)的图结构来解决EDA问题的机会。因此,将电路网表转换为图的结构对于EDA具有重要意义,它为更多优化算法操作提供了新的可能性。

但是网络上很少能够找到其对应的开源简单算法。

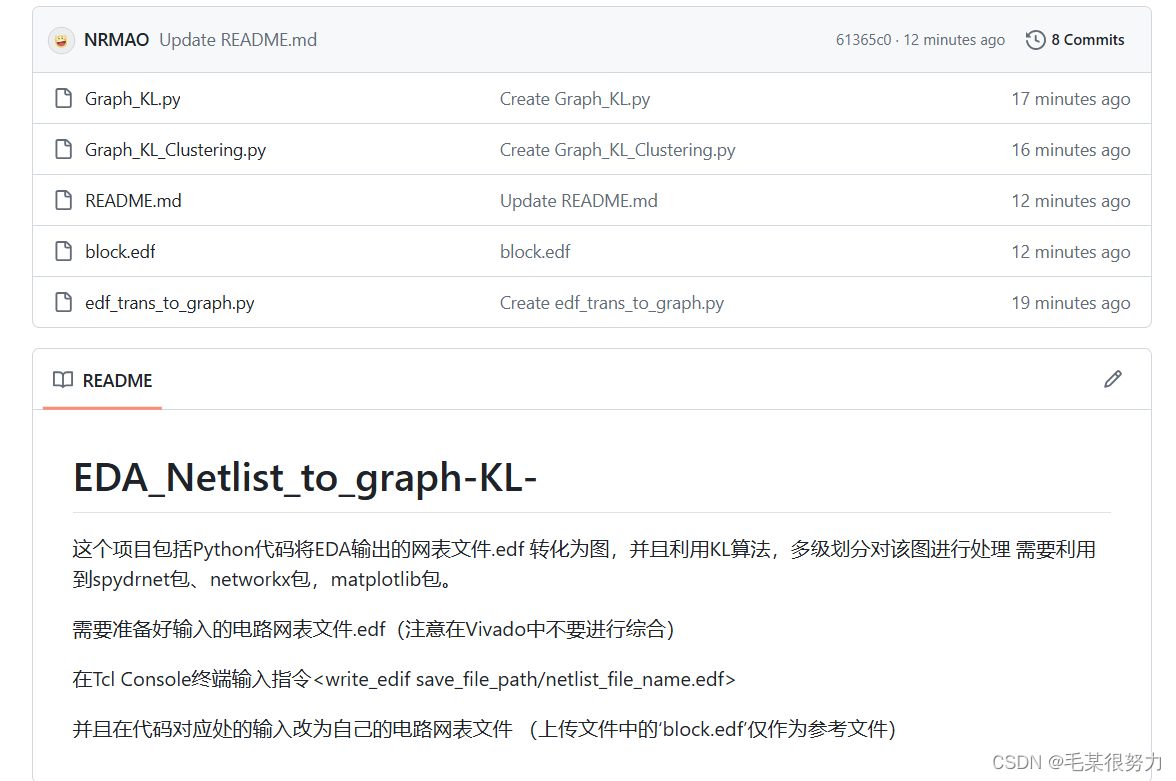

而对图的进行KL算法的划分,也就可以间接对布线进行划分,于是编写了代码,托管到了GitHUb上(https://github.com/NRMAO/EDA_Netlist_to_graph-KL-),希望大家可以一起管理,提出宝贵的意见,也欢迎私信交流。

490

490

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?