基于FPGA的图像反转

在数字图像处理中,如果是CPU进行处理,则一定是任何时候只有一个像素处于一种操作状态。如当前正在进行灰度化,那么在降噪之前,必须把所有像素都进行灰度化,才可以进行后面的操作。

但当FPGA处理时,任何时刻不同的像素都处于不同的运行状态。如像素a在处理二值化,像素b在处理Sobel算子,像素c正在处理降噪,相互之间互不影响。研究图像处理的流水线和数据并发是用Verilog语言处理数字图像算法的关键,这样的运行方式大大加快了FPGA的图像处理速度。

通过数字图像处理课程的学习,以及毕业设计相关知识的学习。本次作业通过vivado FPGA仿真,验证FPGA图像处理效果。

- 处理效果

先上处理效果。

512×512 处理前

512×512 处理后

- 处理过程

通过在Pycharm上运行OpenCV,用python语言将bmp图像转为txt格式。通过在vivado软件,以Verilog语言将txt中的数被十六进制FF减去,输出得到txt格式数据。再在python上运行OpenCV将txt格式,文件转为bmp图像。

将bmp图像灰度化并转为txt格式

import cv2

import numpy as np

'''

main entry

'''

def main():

picture = cv2.imread('lena.bmp')

print(picture.shape[0])

print(picture.shape[1])

print(picture.shape[2])

color_img = np.copy(picture)

picture = cv2.cvtColor(picture, cv2.COLOR_BGR2GRAY)

f = open("data.txt", 'w')

for i in range(picture.shape[0]):

for j in range(picture.shape[1]):

f.write(hex(picture[i, j])[2:]+ "\n")

f.close()

cv2.imshow('lena', picture)

cv2.waitKey(0)

cv2.destroyAllWindows()

if __name__ == '__main__':

main()

2.2在vivado中用Verilog语言将txt数据取反、并编写testbench文件

Source:

module reverse_image(clk, rst, input_data, output_data);

input clk;

input rst;

input[7:0] input_data;

output[7:0] output_data;

wire clk;

wire rst;

wire[7:0] input_data;

wire[7:0] output_data;

// assign output_data = 255 - input_data ;

assign output_data = 8'hFF - input_data ;

endmoduleSimulation:

`timescale 1ns/1ps

module tb;

reg clock;

reg rst;

reg [7:0] image [(512*512-1):0];

reg[18:0] cnt;

integer file_id;

wire[7:0] input_data;

wire[7:0] output_data;

initial begin

clock = 1'b0;

forever #10 clock = ~clock;

end

initial begin

cnt = 19'b0;

$readmemh("./data.txt", image); /

file_id = $fopen("./new_data.txt", "w");

end

initial begin

rst = 1'b1;

#195 rst = 1'b0;

#20000000 $stop;

$fclose(file_id);

end

assign input_data = image[cnt[17:0]];/

always @(posedge clock or posedge rst) /

if (rst) begin /

cnt <= 19'b0; /

end /

else if(cnt[18] == 1'b0) /

begin /

$fwrite(file_id, "0x%x\n", output_data); /

cnt <= cnt + 1'b1; /

end /

initial

begin

$dumpfile("hello.vcd");

$dumpvars(0, tb);

end

reverse_image reverse_image0(

.clk(clock),

.rst(rst),

.input_data(input_data),

.output_data(output_data)

);

endmodule

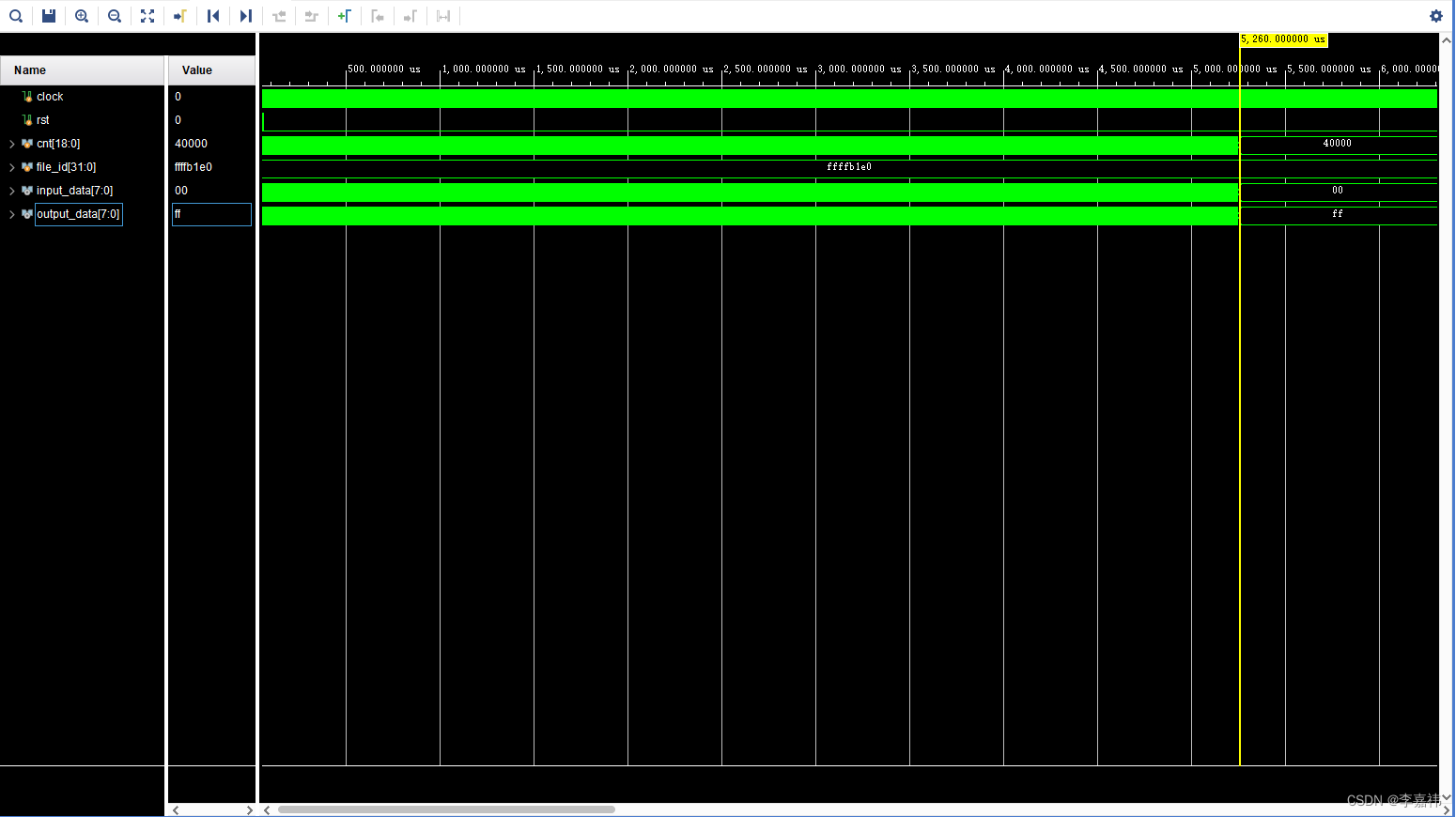

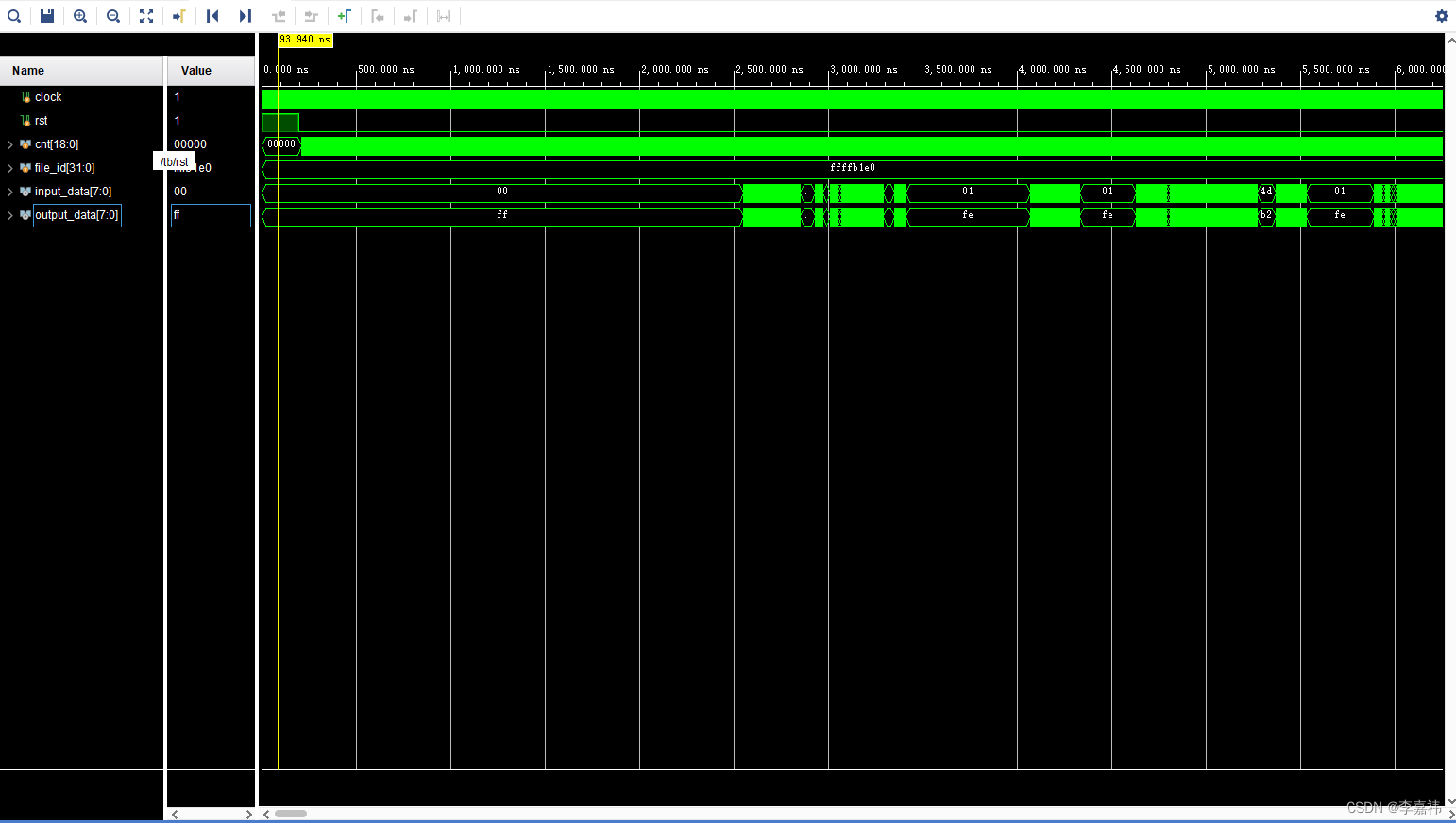

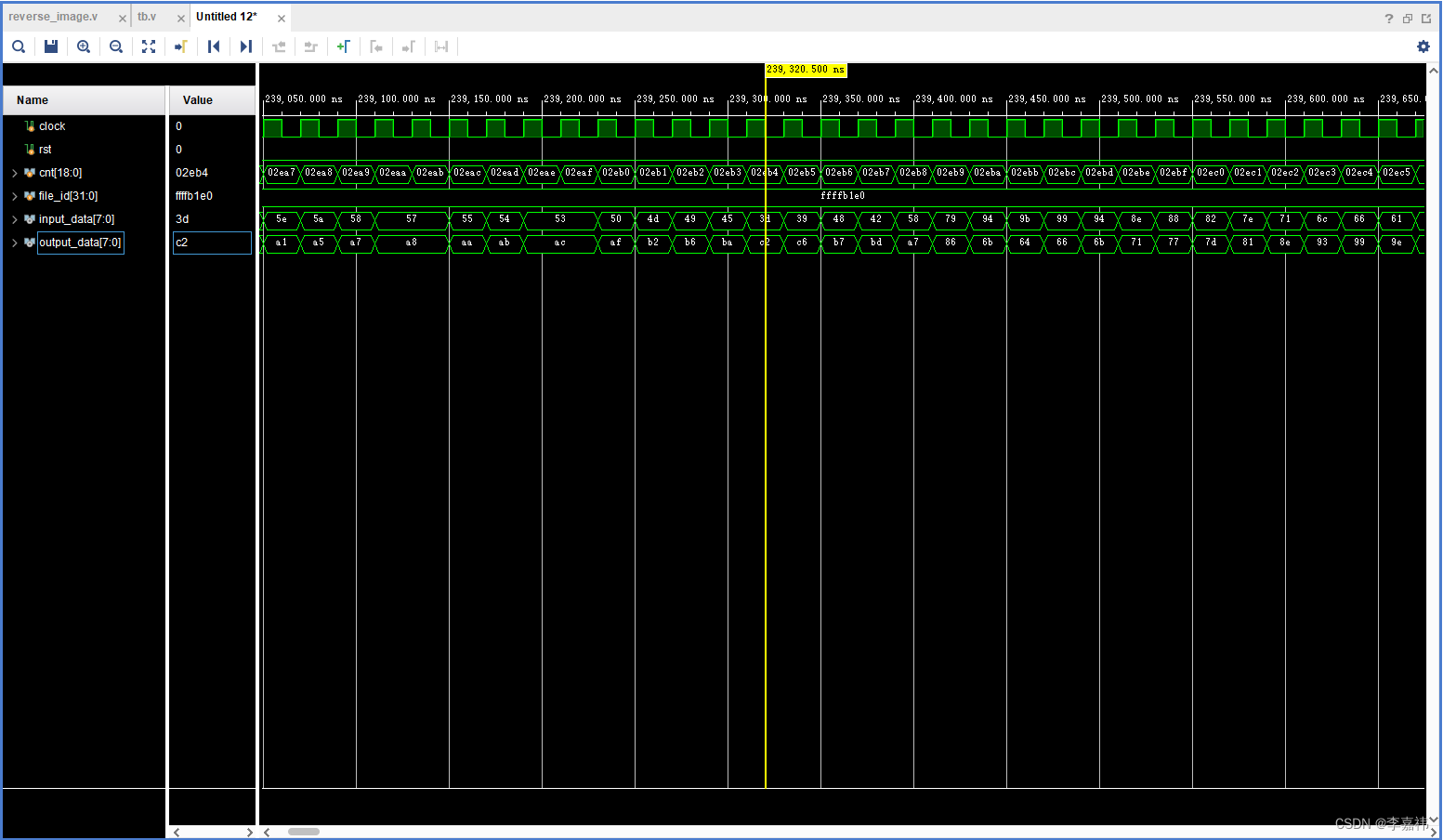

vivado仿真结果如下图:

仿真总图

仿真开始阶段图

仿真中间部分截取图

将前文转换的data.txt,放在工程文件的xsim文件夹里,仿真的结果都输出在了xsim文件夹里的new_data.txt。

2.3在OpenCV中将输出的txt文件转为bmp图像

import cv2

import numpy as np

'''

main entry

'''

def main():

picture = cv2.imread('./lena.bmp')

for i in range(512):

for j in range(512):

picture[i, j] = 255

f = open("./new_data.txt", 'r')

for i in range(512 * 512):

line = f.readline()

picture[int(i / 512), int(i % 512)] = int(line, 16)

f.close()

cv2.imwrite('./new_lena.bmp', picture)

cv2.waitKey(0)

cv2.destroyAllWindows()

if __name__ == '__main__':

main()至此,可以看到在vivado仿真中,处理速度就可以达到5.26ms,如果在FPGA实机中,速度将可以达到更快。需要工程项目的关注+留言邮箱。

本文介绍了如何使用FPGA的并行特性,通过Verilog编程实现图像反转过程的加速,对比了CPU和FPGA在图像处理中的效率,展示了Vivado工具在FPGA仿真中的应用,以及实际处理速度的提升。

本文介绍了如何使用FPGA的并行特性,通过Verilog编程实现图像反转过程的加速,对比了CPU和FPGA在图像处理中的效率,展示了Vivado工具在FPGA仿真中的应用,以及实际处理速度的提升。

1209

1209

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?