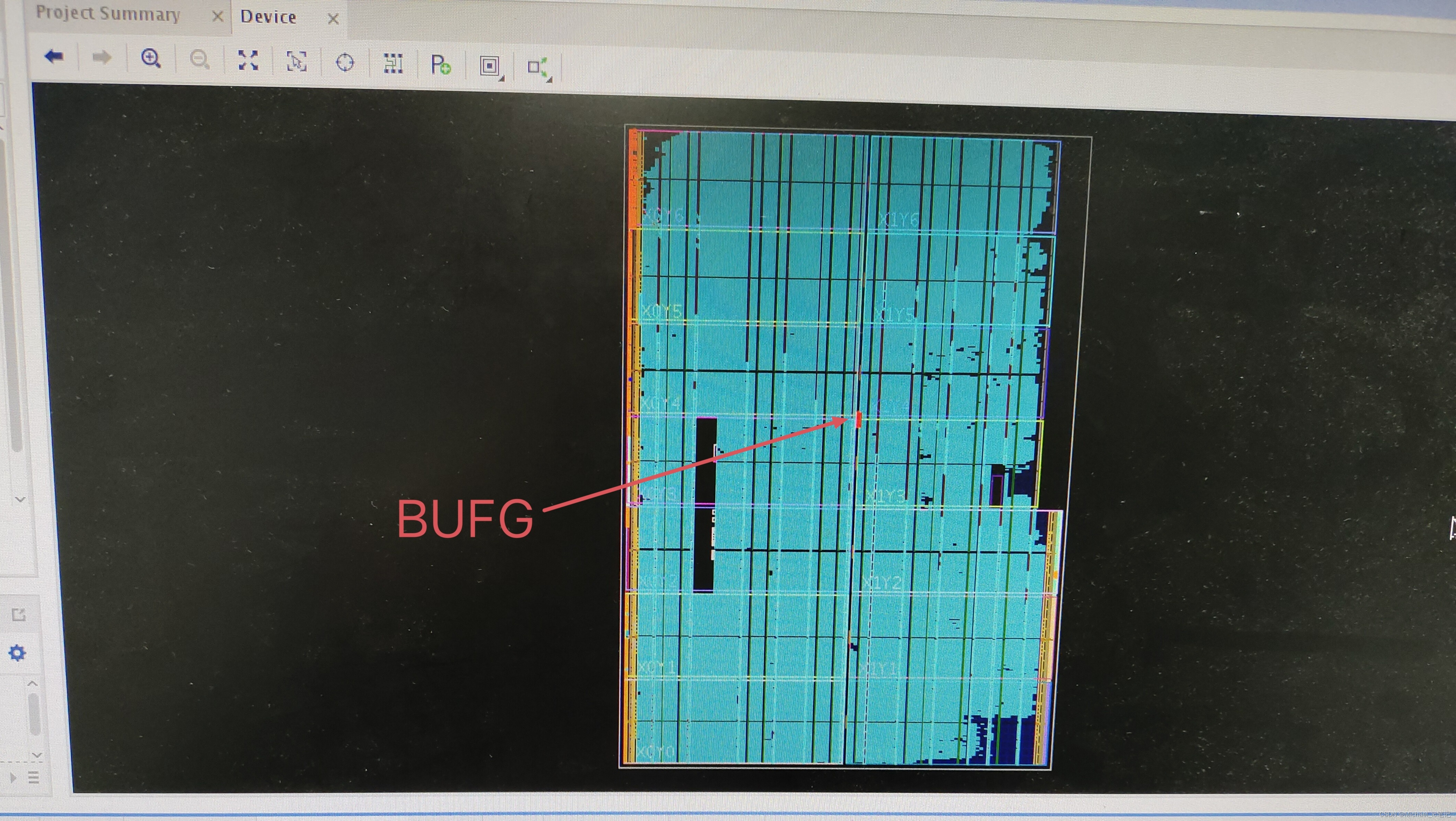

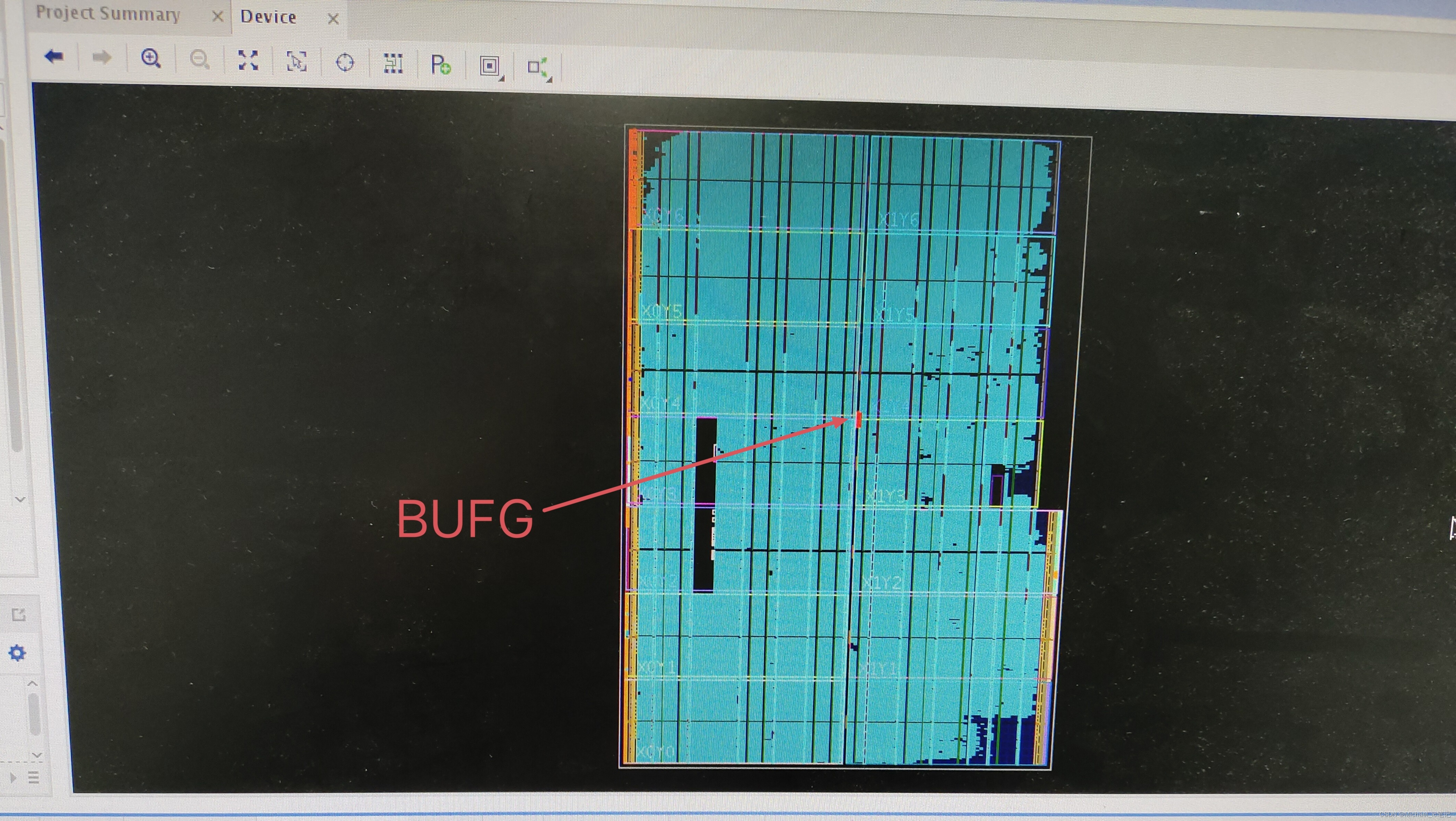

由于xilinx FPGA的时钟资源BUFG一般是固定个数,且其网表模块布局一般分布在整个芯片的正中间位置,故如若出现布局布线BUFG-BUFG级联[Place 30-120]问题。

一般的解决办法有两种,其一是代码设计修改前级级联驱动BUFG为No buff的方式,例如pll/mmcm 核的生成输出时钟驱动配置选择No buff;其二是如若不修改代码设计则需要添加BUFG的物理位置约束,注意级联的BUFG-BUFG物理位置选择必须是相邻的位置,具体可参考UG472时钟资源。

由于xilinx FPGA的时钟资源BUFG一般是固定个数,且其网表模块布局一般分布在整个芯片的正中间位置,故如若出现布局布线BUFG-BUFG级联[Place 30-120]问题。

一般的解决办法有两种,其一是代码设计修改前级级联驱动BUFG为No buff的方式,例如pll/mmcm 核的生成输出时钟驱动配置选择No buff;其二是如若不修改代码设计则需要添加BUFG的物理位置约束,注意级联的BUFG-BUFG物理位置选择必须是相邻的位置,具体可参考UG472时钟资源。

1万+

1万+

454

454

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?