一.VGA协议

- VGA协议,即Video Graphics Array(视频图形阵列),是由IBM公司在1987年推出的视频传输标准。该标准被广泛应用于彩色显示器领域,尤其在CRT显示器时代占据着重要地位。以下是对VGA协议的详细介绍:

- 接口特性:VGA接口是一个15针的D型接口,通过模拟信号传输视频数据。它主要传输红、绿、蓝三种颜色的模拟信号以及水平和垂直的同步信号[3]。

- 色彩原理:VGA基于红、绿、蓝三基色原理来合成不同的颜色。通过调整这三种基本色的强度,可以产生广泛的颜色范围[1]。

- 扫描方式:VGA采用逐行扫描的方式,从屏幕左上角开始,从左向右逐点扫描,每扫描完一行,电子束回到屏幕左边下一行的起始位置,然后进行场同步并使扫描回到屏幕左上方[1]。

- 时序控制:VGA显示要求精确的时序控制,包括行同步和场同步信号。这些信号确保图像数据在正确的时间被正确地传输到显示屏上。行同步信号负责水平同步,而场同步信号负责垂直同步[4]。

- 规格参数:VGA有多种分辨率和刷新率设置,常见的如640x480@60Hz等。每种模式都有其特定的时序参数,这些参数定义了有效图像区域的大小和位置,以及同步脉冲的长度和位置[2]。

- 应用领域:尽管数字接口技术如HDMI已逐渐取代VGA,但由于其结构简单、成本低廉,VGA仍然在许多老旧设备和一些特殊应用中使用[3]。

此外,对于希望深入了解或使用VGA的用户来说,了解其基本的工作原理和关键参数是非常重要的。例如,在进行VGA接口设计时,需要考虑的因素包括:

- 兼容性:确保VGA控制器能够与不同分辨率和刷新率的显示器兼容。

- 信号完整性:由于VGA是模拟信号传输,长距离传输可能会影响信号质量,因此可能需要使用高质量的电缆和连接器。

- 硬件设计:设计电路板时,应考虑到VGA信号的干扰问题,合理布局以减少干扰。

二.VGA显示原理

- VGA显示原理是利用模拟信号进行视频传输,采用逐行扫描的方式将图像像素点依次显示在屏幕上。

VGA(Video Graphics Array)技术自1987年由IBM公司推出以来,已成为视频显示领域广泛使用的标准之一。尽管现代显示技术如HDMI已逐渐占据主流,但了解VGA的工作原理对于理解传统显示技术仍具有重要意义。以下是对VGA显示原理的详细阐述:

- 色彩生成与信号转换:VGA通过红、绿、蓝三基色的组合来产生不同的颜色,这三种颜色的混合可以创造出人眼可见的几乎所有颜色。具体来说,VGA接口中的三个模拟信号分别对应于这三种基本颜色,通过调整这三种信号的强度,可以实现多种颜色和灰度级的显示[1]。

- 逐行扫描与同步信号:在显示过程中,VGA采用逐行扫描的方式,从屏幕左上角开始,逐个像素点向右扫描,完成一行后迅速返回到下一行的起始位置,并继续扫描,直到扫描完屏幕底部的最后一行。这一过程需要精确的时序控制,包括行同步和场同步信号。这些同步信号确保了图像数据能在正确的时间被正确地传输到显示屏上,从而避免了图像的扭曲或滚动[2]。

- 时序标准与兼容性:为了适应不同制造商的显示器,VGA有一套详细的时序标准,这保证了不同设备间的兼容性。例如,行同步和场同步信号的频率和持续时间都需要严格按照这些标准来设置,以确保图像能稳定连续地显示[2]。

- 硬件设计挑战:由于VGA传输的是模拟信号,因此容易受到电磁干扰的影响。设计师在使用VGA时需要考虑如何减少这种干扰,比如使用屏蔽电缆和合理的电路布局来保持信号的完整性。同时,数字到模拟的转换也是设计中的关键部分,通常需要高精度的数模转换器来实现高质量的图像输出[3]。

2.1实验环境

软件:Quartus (Quartus Prime 18.0) Standard Edition Visual Studio Code

硬件:DE2-115FPGA开发板,显示屏

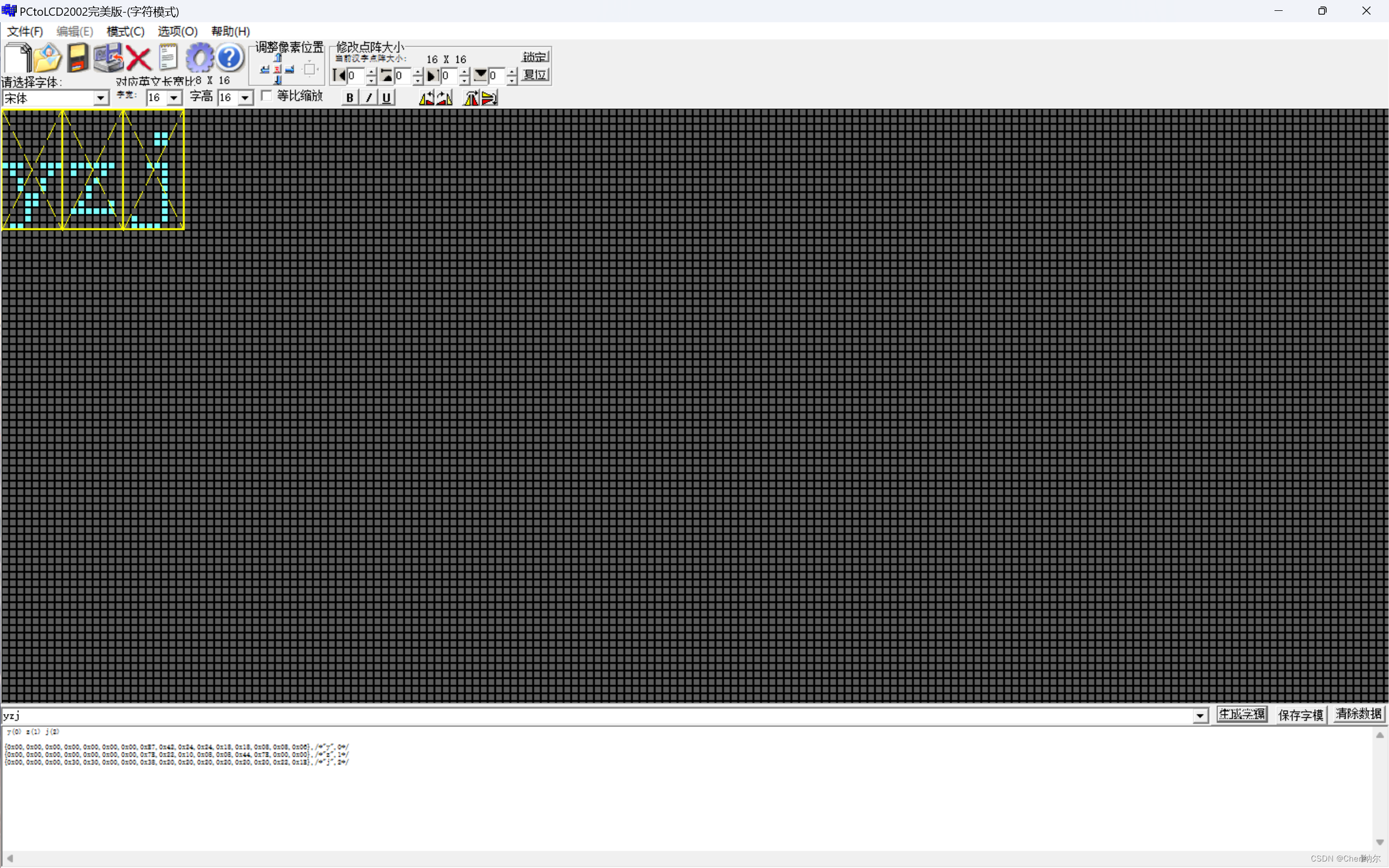

2.2 字符取模

2.3实验代码

data_drive.v

module data_drive (input wire vga_clk,

input wire rst_n,

input wire [ 11:0 ] addr_h,

input wire [ 11:0 ] addr_v,

input wire [ 2:0 ] key,

output reg [ 15:0 ] rgb_data);

localparam red = 16'd63488;

localparam orange = 16'd64384;

localparam yellow = 16'd65472;

localparam green = 16'd1024;

localparam blue = 16'd31;

localparam indigo = 16'd18448;

localparam purple = 16'd32784;

localparam white = 16'd65503;

localparam black = 16'd0;

reg [ 383:0 ] char_line[ 64:0 ];

localparam states_1 = 1; // 彩条

localparam states_2 = 2; // 字符

localparam states_3 = 3; // 图片

parameter height = 78; // 图片高度

parameter width = 128; // 图片宽度

reg [ 1:0 ] states_current ; // 当前状态

reg [ 1:0 ] states_next ; // 下个状态

reg [ 13:0 ] rom_address ; // ROM地址

wire [ 15:0 ] rom_data ; // 图片数据

wire flag_enable_out1 ; // 文字有效区域

wire flag_enable_out2 ; // 图片有效区域

wire flag_clear_rom_address ; // 地址清零

wire flag_begin_h ; // 图片显示行

wire flag_begin_v ; // 图片显示列

//状态转移

always @( posedge vga_clk or negedge rst_n ) begin

if ( !rst_n ) begin

states_current <= states_1;

end

else begin

states_current <= states_next;

end

end

//状态判断

always @( posedge vga_clk or negedge rst_n ) begin

if ( !rst_n ) begin

states_next <= states_1;

end

else if ( key[ 0 ] ) begin

states_next <= states_1;

end

else if ( key[ 1 ] ) begin

states_next <= states_2;

end

else if ( key[ 2 ] ) begin

states_next <= states_3;

end

else begin

states_next <= states_next;

end

end

//状态输出

always @( * ) begin

case ( states_current )

states_1 : begin

if ( addr_h == 0 ) begin

rgb_data = black;

end

else if ( addr_h >0 && addr_h <81 ) begin

rgb_data = red;

end

else if ( addr_h >80 && addr_h <161 ) begin

rgb_data = orange;

end

else if ( addr_h >160 && addr_h <241 ) begin

rgb_data = yellow;

end

else if ( addr_h >240 && addr_h <321 ) begin

rgb_data = green;

end

else if ( addr_h >320 && addr_h <401 ) begin

rgb_data = blue;

end

else if ( addr_h >400 && addr_h <481 ) begin

rgb_data = indigo;

end

else if ( addr_h >480 && addr_h <561 ) begin

rgb_data = purple;

end

else if ( addr_h >560 && addr_h <641 ) begin

rgb_data = white;

end

else begin

rgb_data = black;

end

end

states_2 : begin

if ( flag_enable_out1 ) begin

rgb_data = char_line[ addr_v-208 ][ 532 - addr_h ]? white:black;

end

else begin

rgb_data = black;

end

end

states_3 : begin

if ( flag_enable_out2 ) begin

rgb_data = rom_data;

end

else begin

rgb_data = black

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4619

4619

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?