11.1.6 直接接口

在嵌入式设备中,最好的方式就是直接与数字传感器芯片相连, 这种场合主要发生在相机的设计中。 直接相连的方式等同于连接到一个模拟信号的解码器上。数字像 素从传感器流入,同时伴随着场行同步信号,通过一组寄存器来进行 传感器的配置,例如快门速度、除法、增益控制、窗口操作、降采样 等。这些寄存器的配置通常都是采用串行配置。在CMOS传感器中,每个像素实际上都是可以独立寻址的,尽管这 样的接口通常不会直接提供给用户,但是一些工作模式还是利用了这 个性能。这些提供给用户的工作模式包括以下几种。

(1)窗口操作:常规模式是读出整幅图像,而窗口操作则允许选 择一个感兴趣的矩形窗口,只读出区域内像素。窗口操作减小了传感 器的读取面积,因而提高了帧频。在目标只占图像区域一小部分情况 下的目标跟踪就是窗口操作的一种应用。

(2)跳读:跳读是窗口操作的一种替代选择。这种方式通过跳过 整行或整列,减小了读取像素点的数量。它能在不影响视野的情况下 减小像素点的数量。

(3)像素融合:像素融合是将相邻的像素组合起来的又一种方 式。与跳读相比,这种模式具有两种优势。首先,由于相邻像素的融 合是一种低通滤波操作,这种方式可以减小陡峭边缘附近的锯齿失 真。其次,由于每个像素点都对输出做贡献,像素融合可以提高低亮 度条件下的灵敏度。像素融合通常具有较低的帧频,因为每生成一个 输出像素都要读取内部多个像素。 直接与传感器相接的缺点是传感器与FPGA之间的信号路径要足够 短,以保证时序和信号完整性。

11.2 视频输出接口

11.2.1 CVT标准

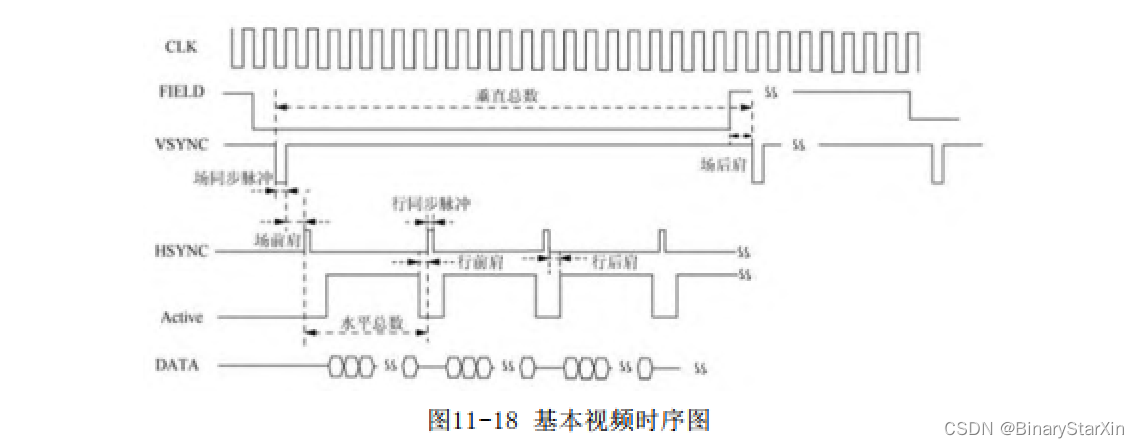

1.基本视频时序先来了解一下视频信号的基本时序,在关于系统仿真的章节中, 在对视频流进行模拟仿真时,已经提出了一个基本的视频流时序。实 际上的视频流时序与此视频流时序基本一致,但是稍有不同,如图11- 18所示。

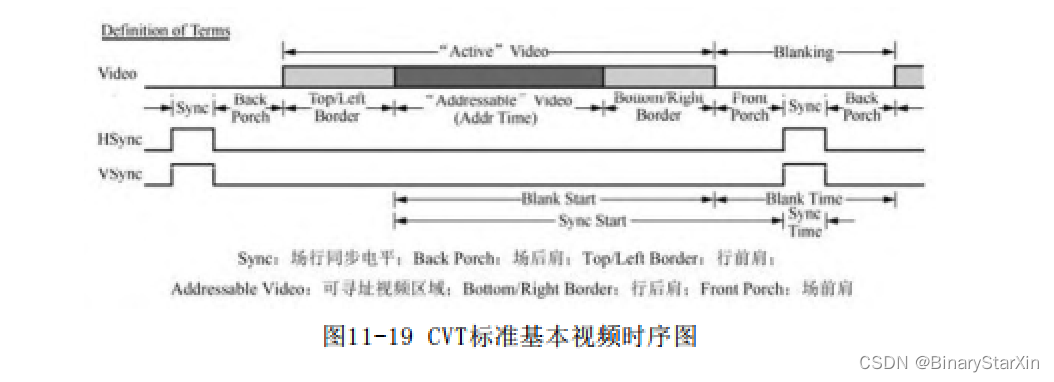

标准的视频信号包括以下几种。 (1)场同步信号VSYNC:标识一帧图像的起始时刻。 (2)行同步信号HSYNC:标识一帧图像中每行图像的起始时刻。 (3)场信号FIELD:指示当前是奇数行还是偶数行。 (4)数据有效信号Active:标识像素流有效信号(这个信号也即 我们常用的dvalid信号)。 (5)像素信号DATA:真正的视频数据流。 (6)像素时钟信号CLK:像素参考时钟(仅对于数字视频有 效),一般情况下是上升沿有效。 值得注意的是,场行同步信号的有效电平在不同的标准中可以不 同。 2.CVT标准视频时序视 频 电 子 标 准 协 会 ( Video Electronics Standards Association , VESA ) 定 义 了 一 组 公 式 , 称 为 “ 协 调 视 频 时 序 ” (CVT)标准。该标准详细规定了在给定分辨率和刷新率下的时序要 求,同时也列出了过去的一些工业时序标准。 在CVT标准中,有两组时序规定:一组面向传统的CRT监视器(可 以满足电子枪的切换时间要求),另一组面向不需要太长消隐期的当 代平板显示器。后一组规定大大缩减了水平消隐期,从而增加了视频 内容的可用带宽,并显著降低了像素时钟频率。水平和垂直脉冲的极 性指示了采用哪一种时序模式——CRT时序模式、缩减消隐期的时序模 式,或者过去的时序模式。CVT标准还通过垂直同步的持续宽度将图像 长宽告知显示器。 CVT标准中的时序参数如图11-19所示(场行同步均为高电平有 效)。

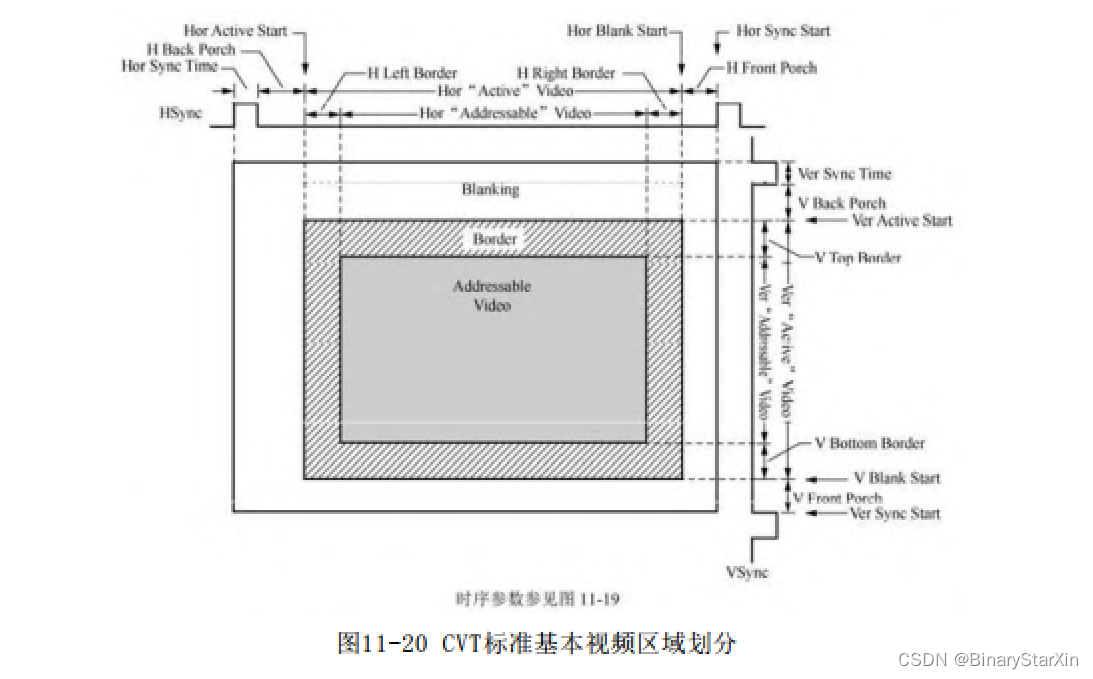

1)CVT视频区域划分 CVT将一个视频流分为3个区域:Blanking区域(暗电平区域), Border区域(边界区域)和Addressable Video区域(可寻址视频区 域),如图11-20所示。这3个区域在一个完整的视频场内构成了三个 封闭环。Border区域是视频边界区域,这个区域是为了划分视频边界所设 计的,通常情况下是不存在的,因为我们完全可以在视频显示的上游 对边界进行划分和处理。因此,实际上上述视频时序图被划分成两个 闭环。 Blanking区域是视频消隐区域,在这个区域内的扫描电平通常为 黑电平(Black Level)。这个区域内没有有效的像素信号。主要用作 场行同步产生,同时让CRT扫描枪有足够的时间进行移动和切换。 Addressable Video是有效视频区域,这个区域的左上角为输入视 频当前帧的第一个有效像素,右下角为最后一个像素。

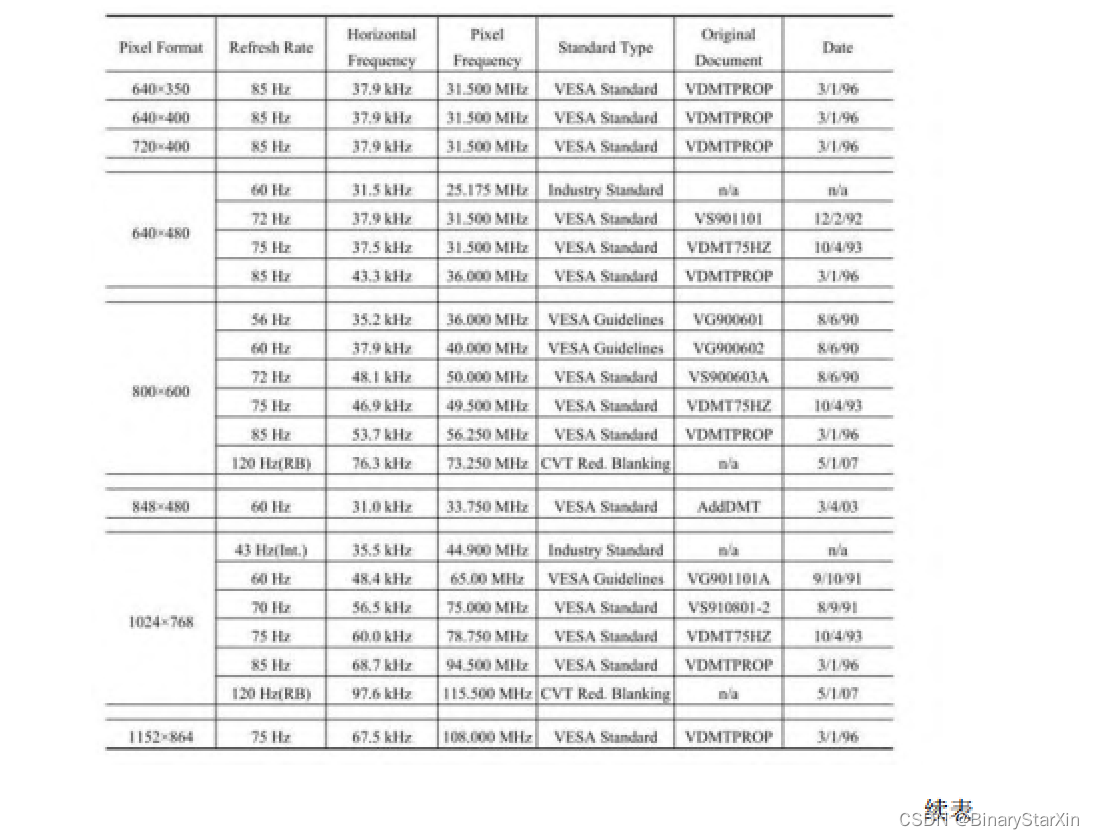

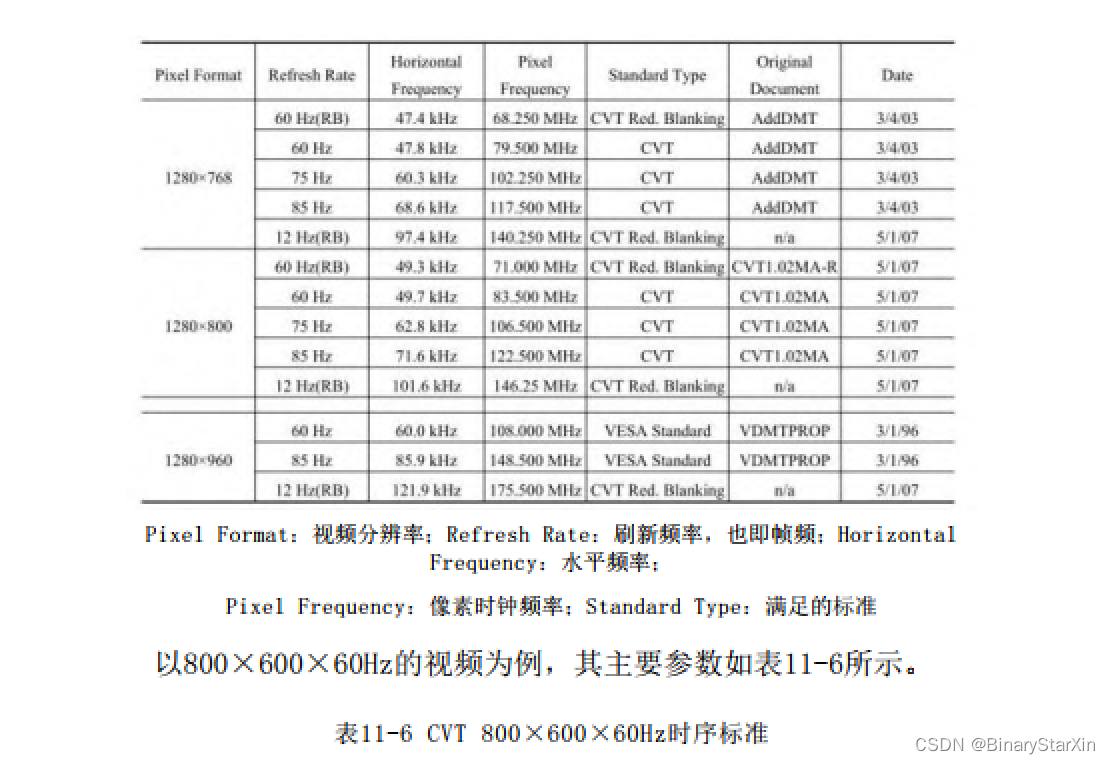

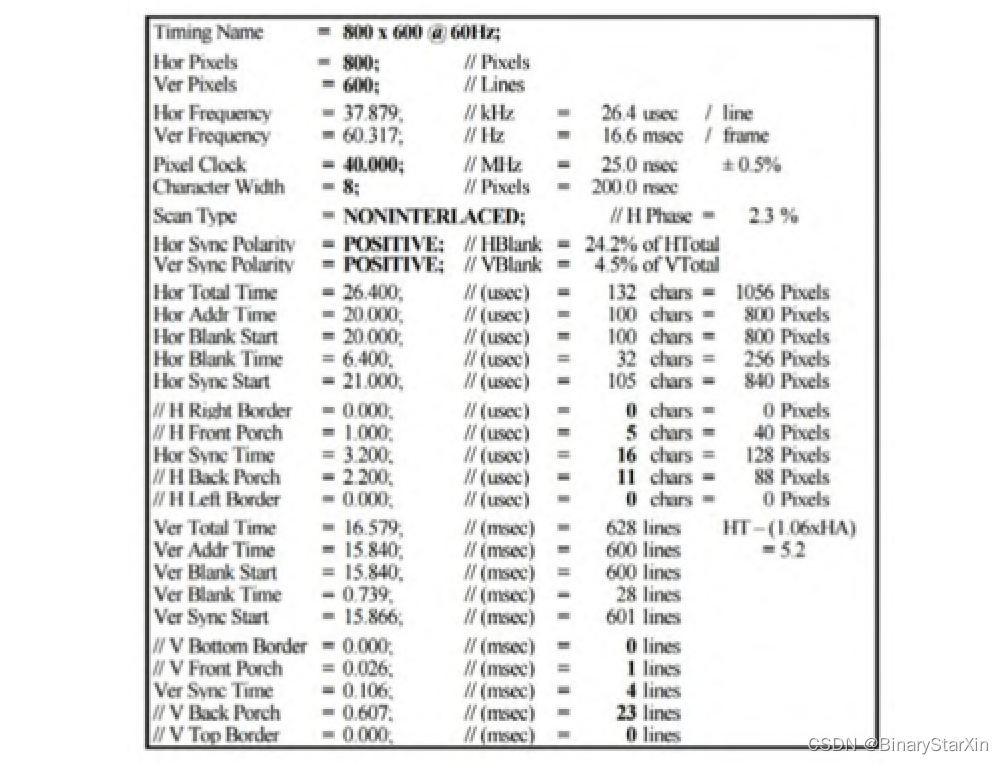

2)CVT视频标准主要时序参数(不考虑Border区域) (1)垂直同步时间VSync:指的是垂直同步的脉冲时间。(2)垂直同步前肩V Front Porch:指的是当前有效视频场结束 到下个垂直同步到来的时间间隔。 (3)垂直同步后肩V Back Porch:指的是垂直同步结束到下一个 有效视频场数据到来的时间间隔。 (4)水平同步时间HSync:指的是水平同步的脉冲时间。 (5)水平同步前肩H Front Porch:指的是当前行结束到下个水 平同步到来的时间间隔。 (6)水平同步后肩H Back Porch:指的是水平同步结束到下一行 数据到来的时间间隔。 实际上,一旦视频的分辨率被确定,内部的有效视频矩形区的面 积已经固定,上述这6个参数决定了矩形的外环尺寸大小。很显然,这 个外环的矩形尺寸决定了一帧视频的扫描时间,其横坐标方向即为视 频的行扫描时间。整个矩形框的扫描时间即为一帧视频的扫描时间, 对于60Hz的扫描频率,这个时间约为16.6667ms。 我们当然希望这个尺寸越小越好,这样我们可以最大地利用带 宽,但是这个时间要保证CRT显示器的硬件切换时间,对于CVT标准, 通常情况下对于固定的分辨率和扫描频率,这几个参数是固定的。 表11-5列出了几个CVT标准中的一些常用分辨率和刷新频率下的时 序参数。其他分辨率和刷新频率下的时序参数可以通过查表得到,或 者从CVT标准附带的数据表中得到。 表11-5 CVT部分标准

视频时序很容易用两个计数器来产生,一个用于生成沿着每一行 的水平时序,另外一个用于生成垂直时序。根据计数器的数值即可确 定生成每个时序信号的时刻。用“小于”和“大于”来判断计数器的 数值是否位于一个特定的范围内,不如用“等于”判断更好,因为后 者所需的逻辑资源更少一点。这需要采用一个1bit的寄存器,在信号 开始时将其置为高电平,在信号结束时将其清零。仅当在每一行结束 时水平计数器被重置后,垂直计数器才开始工作。垂直同步脉冲与水 平同步脉冲的主沿相同步。在图像区域的扫描开始时,计数器通常都 是零。这样,在消隐期结束时,计数器的数值对应于总的像素数,于 是可以省略一个比较步骤。但是如果流水线需要预装填,那么将起始 点前移可以简化逻辑电路。

11.2.2 VGA

1.VGA简介 VGA接口,也即Video Graphics Array,是IBM在1987年随PS/2机 一起推出的一种模拟视频传输标准。最初的VGA是特指IBM的PS/2上的 显示硬件接口,但是随着VGA的广泛应用及推广,VGA已经发展成为一 个计算机和嵌入式领域的模拟视频传输标准。 标 准 的 VGA 接 口 是 15pin 的 D-SUB 接 口 , 最 初 的 分 辨 率 只 有 640×480,VGA的不断发展使其衍生出了许多更高分辨率的显示模式标 准,例如 Super VGA,支持800×600的分辨率,Extend VGA,支持 1024×768的分辨率,最新的VGA标准QSXVGA支持2560×2048超过2K的 分辨率(当然,更高的分辨率带来了更高的时钟频率和成本要求)。 因此,在高清视频大行其道的今天,VGA接口并没有像预期中的那样被 淘汰,另外一方面的原因是VGA作为一个视频显示接口早已成为各种计 算机及显示接口的标配,目前基本上所有的显示器和计算机都配有VGA 接口,但是不一定会有DVI或是HDMI接口。

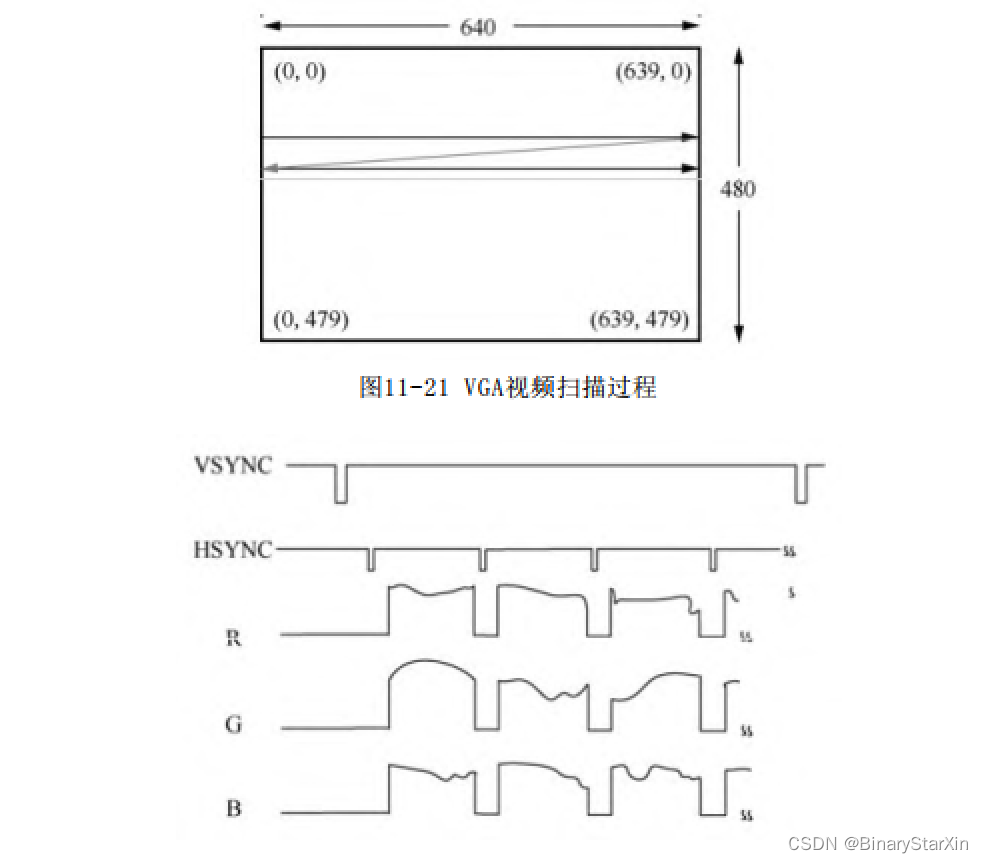

2.VGA时序图 在理解了CVT时序标准之后,我们可以很容易地理解VGA的时序, 然而CVT标准里面并没有关于扫面顺序的规定。因此我们首先需要确定 的是VGA接口的扫描顺序。 VGA的扫描方式是逐行顺序扫描,对于CRT显示器,电子束从监视 器的左上角开始扫描,扫描第一行之后接着扫描第二行,直到一副图 像扫描完毕,电子枪从屏幕的右下角移动到左上角重新开始新的一帧 扫描。每行的消隐时间一般约占扫描时间的20%,这样便给扫描电子束 留 了 足 够 的 时 间 来 重 定 位 , 以 便 开 始 下 一 行 的 扫 描 。 对 于 标 准 640×480的分辨率,其显示扫描过程如图11-21所示。 一个标准的VGA时序包括5个有效信号:(1)行同步信号(HSYNC):数字信号,视频行同步信号(低电 平有效)。 (2)场同步信号(VSYNC):数字信号,视频场同步信号(低电 平有效)。 (3)R信号:模拟信号(0~0.7V),红色视频分量。 (4)G信号:模拟信号(0~0.7V),绿色视频分量。 (5)B信号:模拟信号(0~0.7V),蓝色视频分量。 一个典型的VGA时序图如图11-22所示。

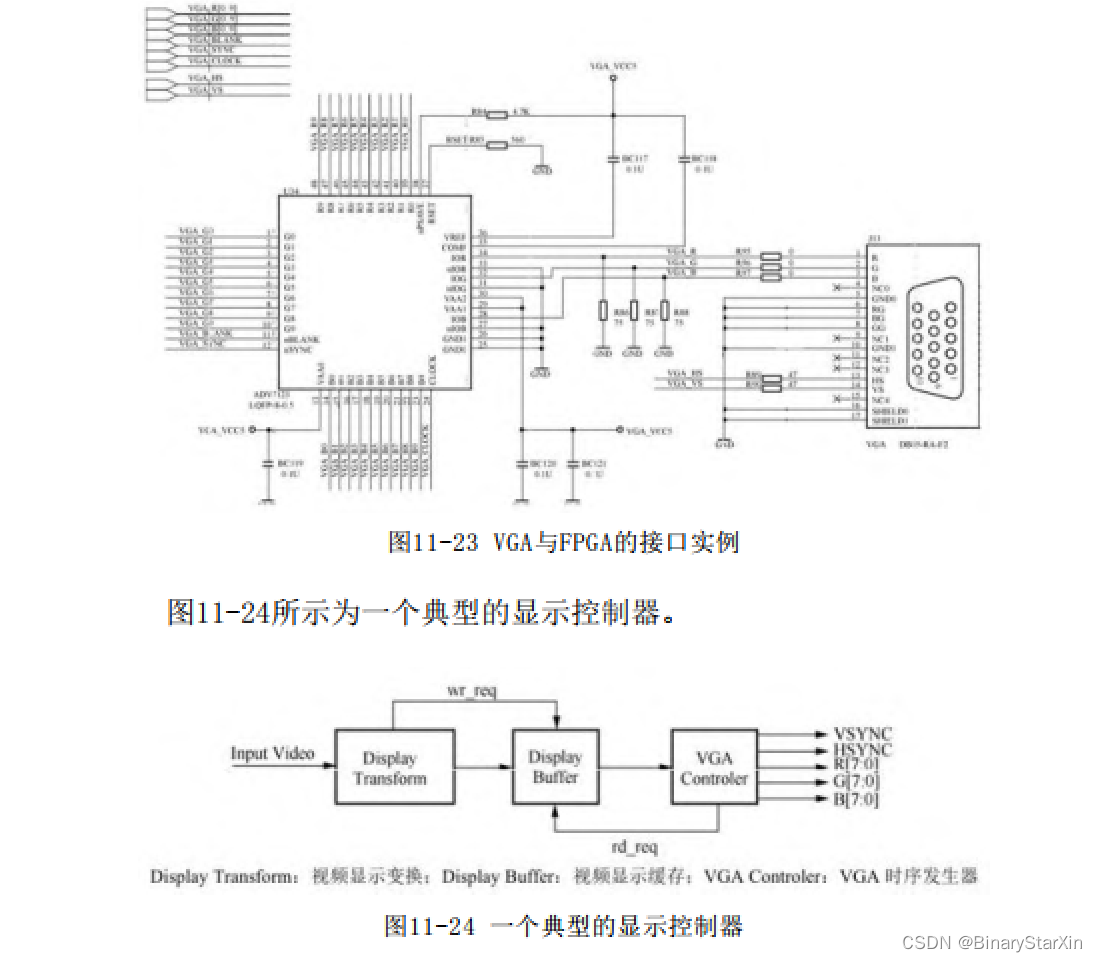

图11-22 VGA时序图 几个重要的时序参数在图中并没有列出来,这是由于VGA的时序标 准也满足CVT标准。这些时序参数的定义与CVT的定义保持一致。 3.VGA与FPGA的接口 VGA是一个模拟显示接口,FPGA输出的数字视频流不能直接接到 VGA显示接口上面进行显示。和视频输入接口相反的是,需要通过一个 视频编码器,将FPGA输出的待显示的数字视频信号转换为模拟视频信 号,这个视频编码器实质上也是一个DA转换器。 通常情况下,这个视频编码器不会自动生成满足要求的VGA时序, 而是直接由FPGA来生成时序,编码器只负责对输入的信号进行DA转 换,并接收一些简单的控制信息,例如黑电平信号、复合同步信号 等。 ADV7123是ADI公司生产的一款典型的视频编码器,它内置3个 10bit的高速(最高支持330MHz)DAC,可完成10位RGB三通道输入视频 数据的数模转换。 其与FPGA的一个典型电路应用如图11-23所示(引用自Altera DE2 开发板): 4.VGA设计示例 一个典型的VGA控制器至少包含以下内容: (1)提供完整的VGA标准时序。 (2)提供显示缓存及其控制接口。 (3)必要的显示变换处理。

VGA标准时序的产生是比较简单的工作,特别是在确定了显示分辨 率的时候(通常情况下在嵌入式设计中,这个分辨率是固定的)。在 图11-24中,VGA Controller主要完成这个工作。它主要是根据指定的 时序参数设置来产生行同步信号和场同步信号,并在视频显示有效时 刻从视频显示缓冲区读取数据进行输出到视频编码器进行DA转换。为了提高显示的对比度和增强显示效果,显示变换处理在某些场 合是十分必要的,比如我们在直方图章节所介绍的直方图线性变换。 在实际应用中,丢帧显示也是常用的显示手段。这主要发生在待显示 的数据流带宽相对于显示带宽较大的场合。 显示缓存及其控制是比较麻烦的一件事情。在实际应用中,除了 基本的时序功能测试,一般不会存在不需要显示缓存的场合。这是由 于待显示视频流的带宽往往和显示模块带宽不是严格匹配的。不匹配 主要由两个因素引起:一是对于固定分辨率和刷新频率的显示时序, 显示时钟是固定的(参见CVT标准),这个时钟往往与上游的待显示数 据流不同域。因此,至少需要一个缓存器来作为跨时钟域的转换器和 带宽匹配器。二是即使上下游的时钟是同步的,待显示的视频流的有 效带宽与显示带宽通常情况下也不是一致的:待显示的六个时序参数 通常情况下与标准时序不一致,在部分情况下还很有可能是动态变化 的。

显示缓存可以放在片内或片外,这主要取决于实际的应用场合。 对于分辨率较低的显示缓存,即使前后带宽速率差别较大,所需缓存 空间也不会很大,通常情况下会将其放在片内。对于分辨率较高的显 示缓存,如果前后带宽速率差别不大,就将其放在片内也是可行的: 这时需要的缓存空间也不会很大。若带宽差别比较大,则所需的缓存 空间相对较大。此时,将缓存放在片内不太合适。 5.基于Verilog的VGA控制器 以下的代码是一个VGA时序发生器的示例:(显示时钟40MHz,视 频分辨率800×600,刷新频率60Hz)。

'timescale 1ps/1ps

module vga_timing(

clk,

reset_n,din_valid, //输入有效

din, //输入数据

vsync, //输出场同步

hsync, //输出行同步

video_w, //输入视频宽度

video_h, //输入视频高度

scan_freq, //输入扫描频率

rgb_out, //输出像素

col, //输出列计数

row, //输出行计数

frame_cnt //输出帧计数

);

parameter dw = 8;

parameter dw_iw = 13;

//6个主要的时序参数(参见CVT标准800*600)

//vertical parameter

parameter vfront_porch = 1;

parameter vsnyc_pulse = 4;

parameter vback_porch = 23;

//horizon parameter

parameter hfront_porch = 40;

parameter hsnyc_pulse = 128;

parameter hback_porch = 88;

localparam dw_freq = 8;

input clk;

input reset_n;

input din_valid;input [dw*3-1:0] din;

input [dw_iw-1:0]video_w;

input [dw_iw-1:0]video_h;

input [dw_freq-1:0]scan_freq;

output reg vsync;

output reg hsync;

output reg [dw*3-1:0]rgb_out;

output [dw_iw:0] col;

output [dw_iw:0] row;

output [dw_freq-1:0]frame_cnt;

reg is_video_active;

reg [dw_freq-1:0]frame_cnt_r;

wire [dw_iw-1:0] iw;

wire [dw_iw-1:0] ih;

wire [dw_freq-1:0]hz;

wire [dw_iw:0] vwhole_col;

wire [dw_iw:0] hwhole_line;

wire [31:0] vwhole_col_tmp;

wire [31:0] hwhole_line_tmp;

reg [dw_iw:0] in_line_cnt;

reg [dw_iw:0] line_counter;

wire [dw*3-1:0] rgb_in;

assign iw = video_w;

assign ih = video_h;

assign hz = scan_freq;

assign vwhole_col_tmp = (vfront_porch + vsnyc_pulse +

vback_porch+ {{32-dw_iw{1'b0}},video_h});assign hwhole_line_tmp = (hfront_porch + hsnyc_pulse +

hback_porch+{{32-dw_iw{1'b0}},video_w});

assign vwhole_col = vwhole_col_tmp[dw_iw:0];

assign hwhole_line = hwhole_line_tmp[dw_iw:0];

always @(posedge clk or negedge reset_n)

if (reset_n == 1'b0)

rgb_out <= {dw*3{1'b0}};

else

begin

if (is_video_active == 1'b1 & din_valid == 1'b1)

rgb_out <= #1 din;

else

rgb_out <= {dw*3{1'b0}};

end

//frame counter

always @(posedge clk or negedge reset_n)

begin: frmae_conut

if (reset_n == 1'b0)

frame_cnt_r <= {dw_freq{1'b0}};

else

begin

if ((in_line_cnt == 1) & (line_counter == (ih +

1)))

begin

if (frame_cnt_r == hz - 1)

frame_cnt_r <= {dw_freq{1'b0}};

elseframe_cnt_r <= frame_cnt_r + 1'b1;

end

end

end

assign frame_cnt = frame_cnt_r;

assign col = in_line_cnt;

assign row = line_counter;

//in line(horison)counter

always @(posedge clk or negedge reset_n)

begin: in_line_count

if (reset_n == 1'b0)

in_line_cnt <= {dw_iw+1{1'b0}};

else

begin

if (in_line_cnt < (hwhole_line - 1'b1))

in_line_cnt <= in_line_cnt + 1'b1;

else

in_line_cnt <= {dw_iw+1{1'b0}};

end

end

//line(vertical)counter

always @(posedge clk or negedge reset_n)

begin: line_count

if (reset_n == 1'b0)

line_counter <= {dw_iw+1{1'b0}};

else

beginif (in_line_cnt == (hwhole_line - hback_porch -

1))

begin

if (line_counter < (vwhole_col - 1'b1))

line_counter <= line_counter + 1'b1;

else

line_counter <= {dw_iw+1{1'b0}};

end

end

end

//vsync signal output

always @(posedge clk or negedge reset_n)

begin: vsync_output

if (reset_n == 1'b0)

vsync <= 1'b1;

else

begin

if (line_counter >= (ih + vfront_porch) &

line_counter <=

(ih + vfront_porch + vsnyc_pulse-1))

vsync <= 1'b0;

else

vsync <= 1'b1;

end

end

//hsync signal output

always @(posedge clk or negedge reset_n)begin: hsync_output

if (reset_n == 1'b0)

hsync <= 1'b1;

else

begin

if (in_line_cnt <= (iw + hsnyc_pulse +

hfront_porch - 1) &

in_line_cnt >= (iw + hfront_porch - 1))

hsync <= 1'b0;

else

hsync <= 1'b1;

end

end

//video active signal

always @(posedge clk or negedge reset_n)

begin: pixel_valid_signal

if (reset_n == 1'b0)

is_video_active <= 1'b0;

else

begin

if (in_line_cnt <= iw - 1 & line_counter <= ih

- 1)

is_video_active <= 1'b1;

else

is_video_active <= 1'b0;

end

end

7780

7780

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?