一、在线Verilog编程网站学习

1、门电路练习

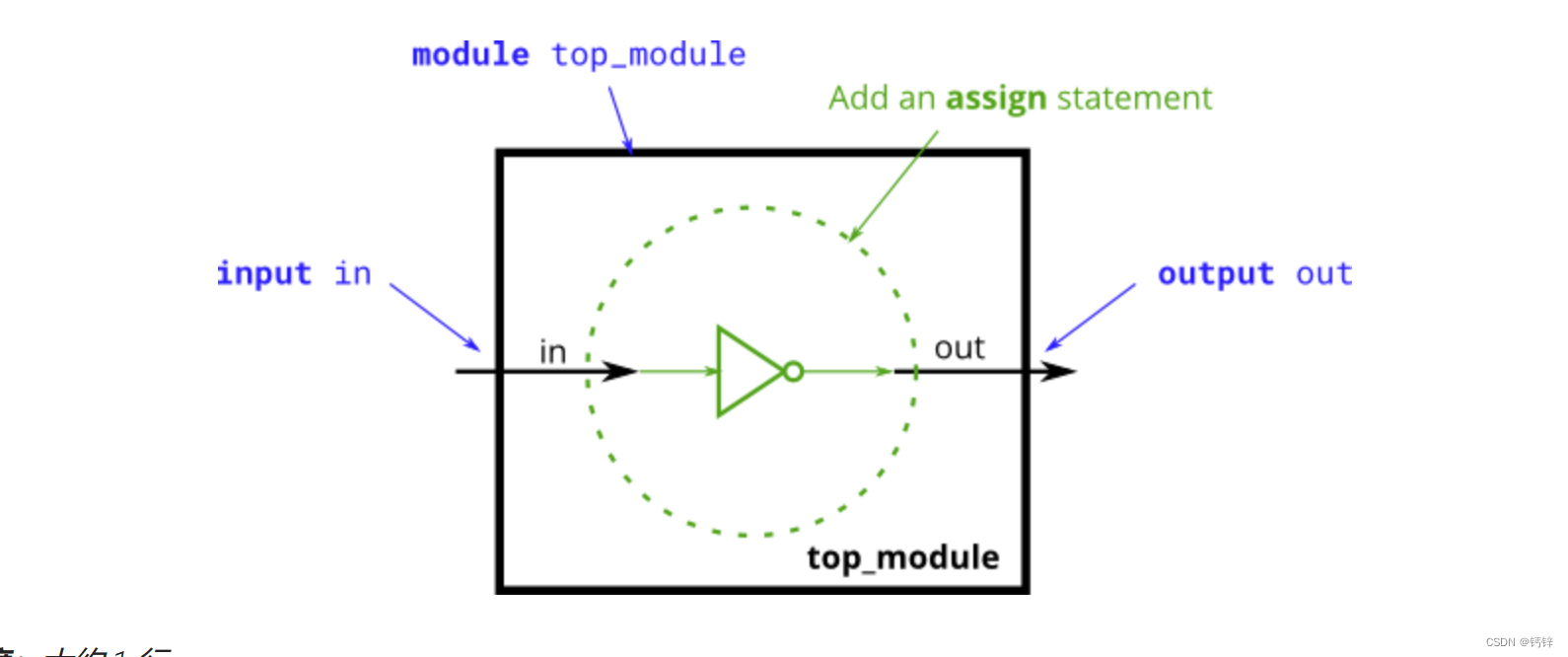

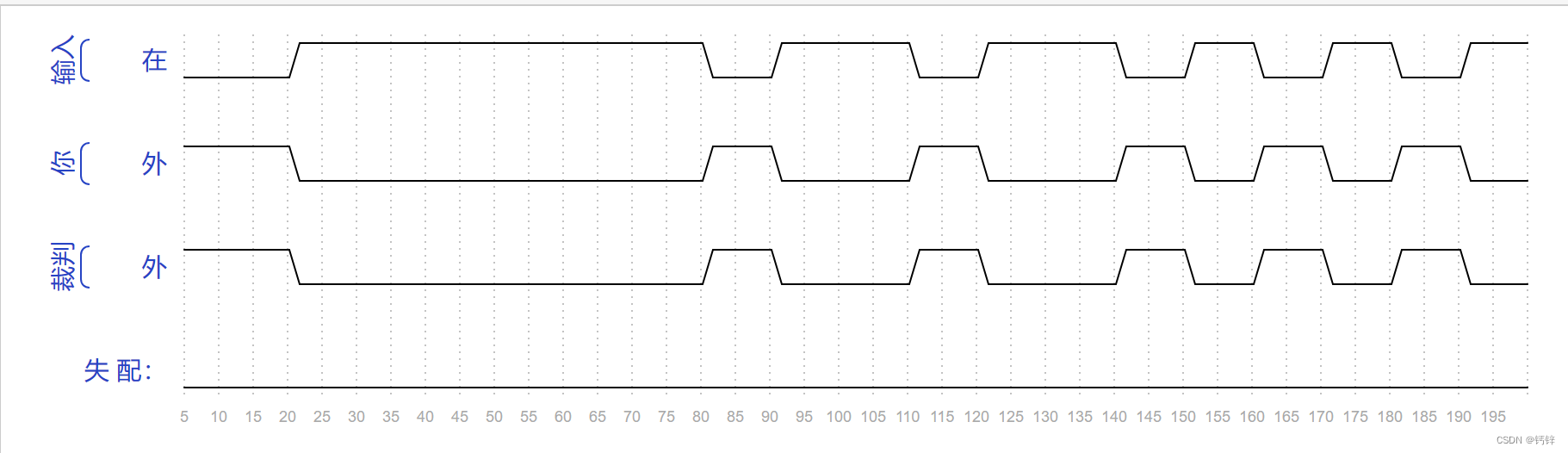

1.非门

module top_module( input in, output out );

assign out = ~in;

endmodule

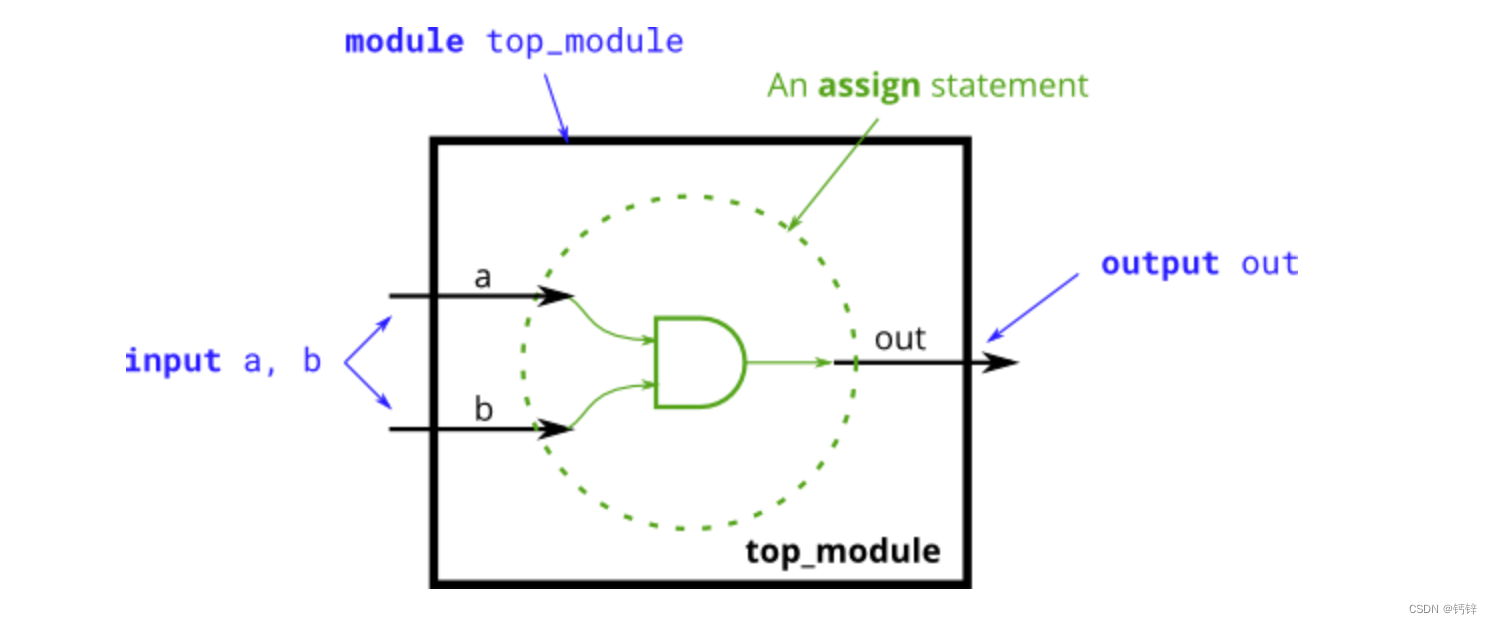

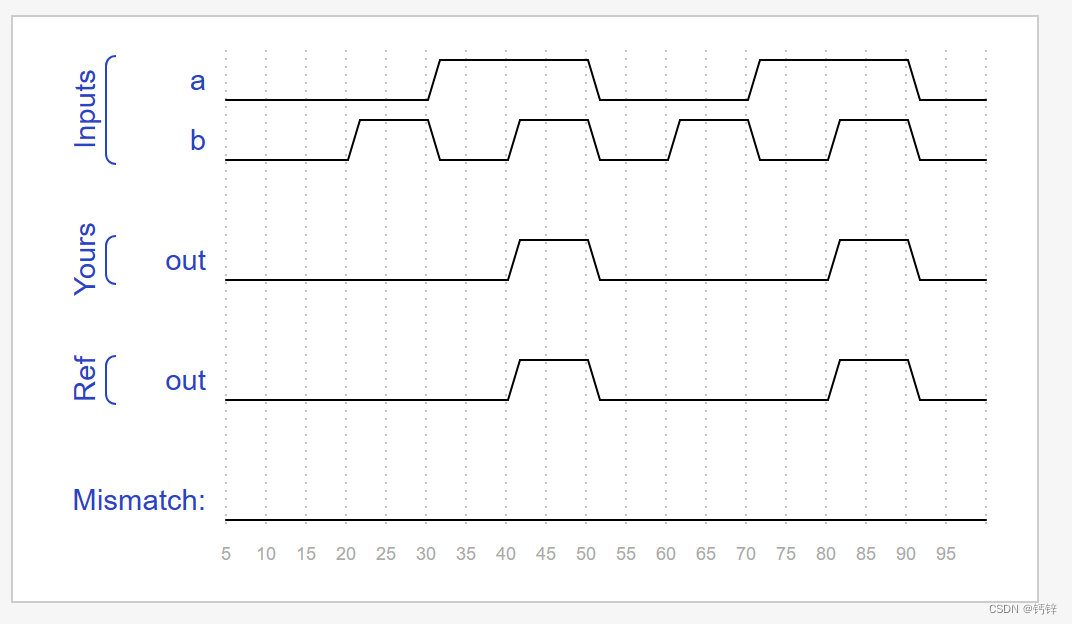

2.与门

module top_module(

input a,

input b,

output out );

assign out = a & b;

endmodule

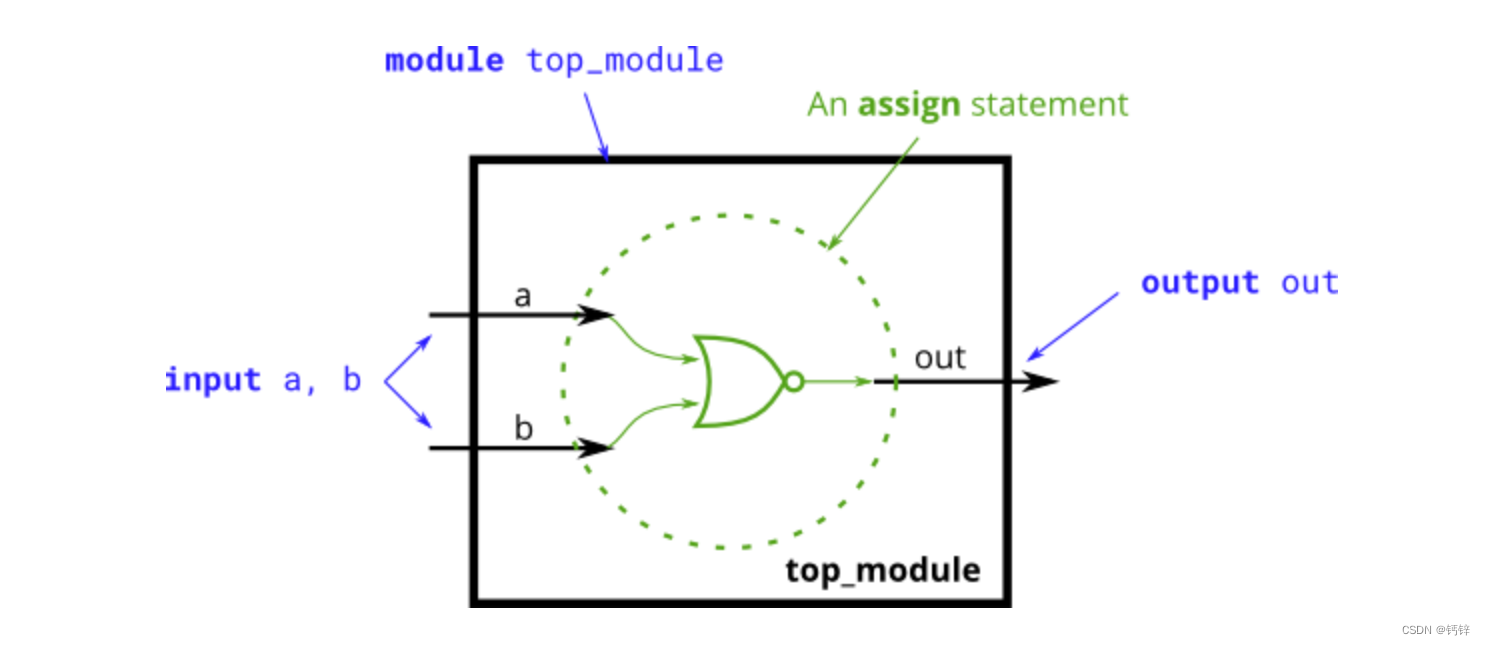

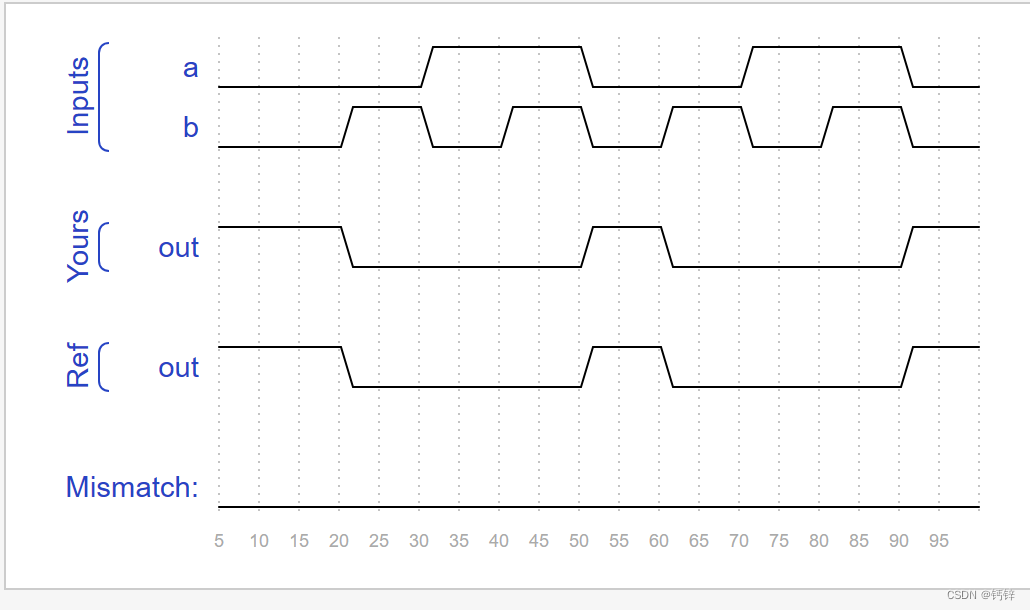

3.NOR门

module top_module(

input a,

input b,

output out );

assign out = ~(a | b);

endmodule

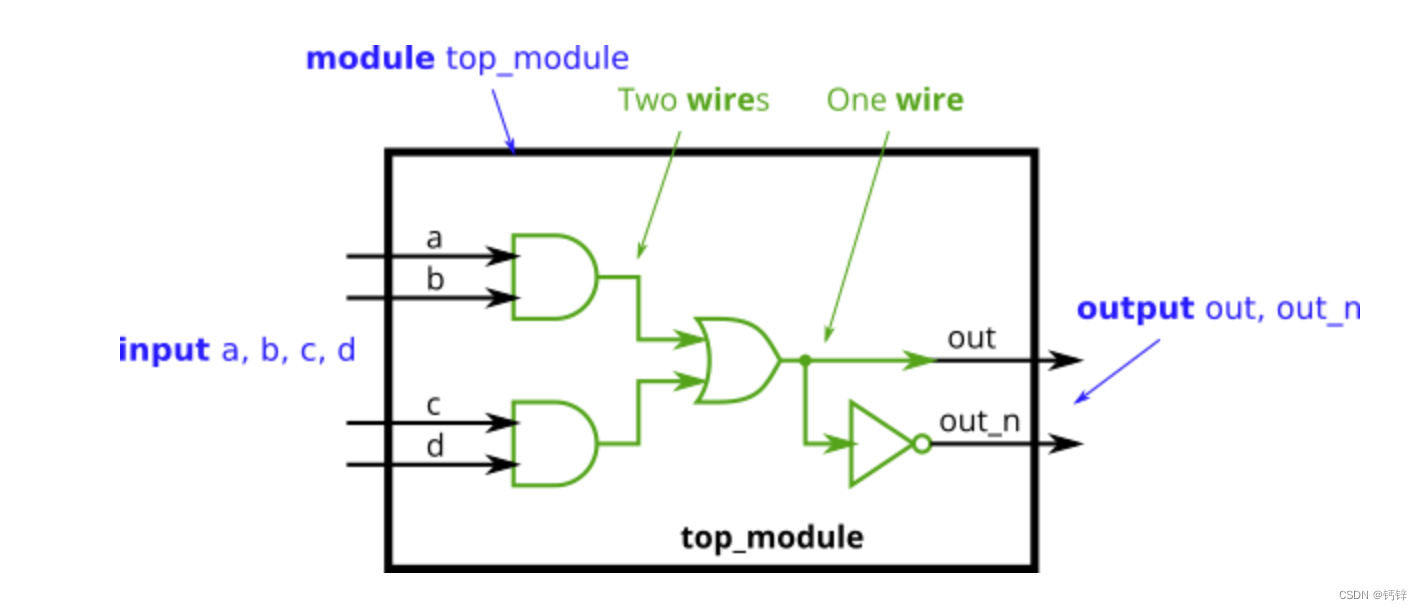

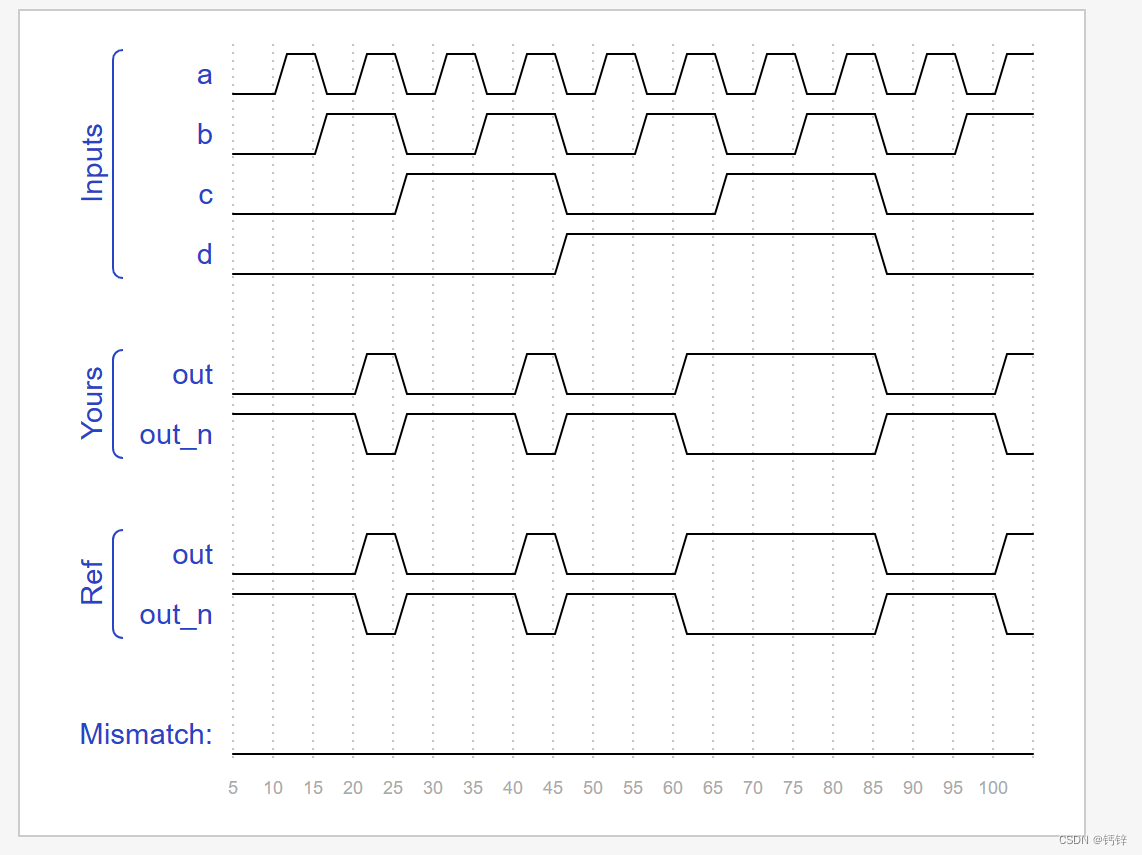

2、组合电路练习

module top_module(

input a,

input b,

input c,

input d,

output out,

output out_n );

wire and_1 = a & b;

wire and_2 = c & d;

wire or_1 = and_1 | and_2;

assign out = or_1;

assign out_n = ~or_1;

endmodule

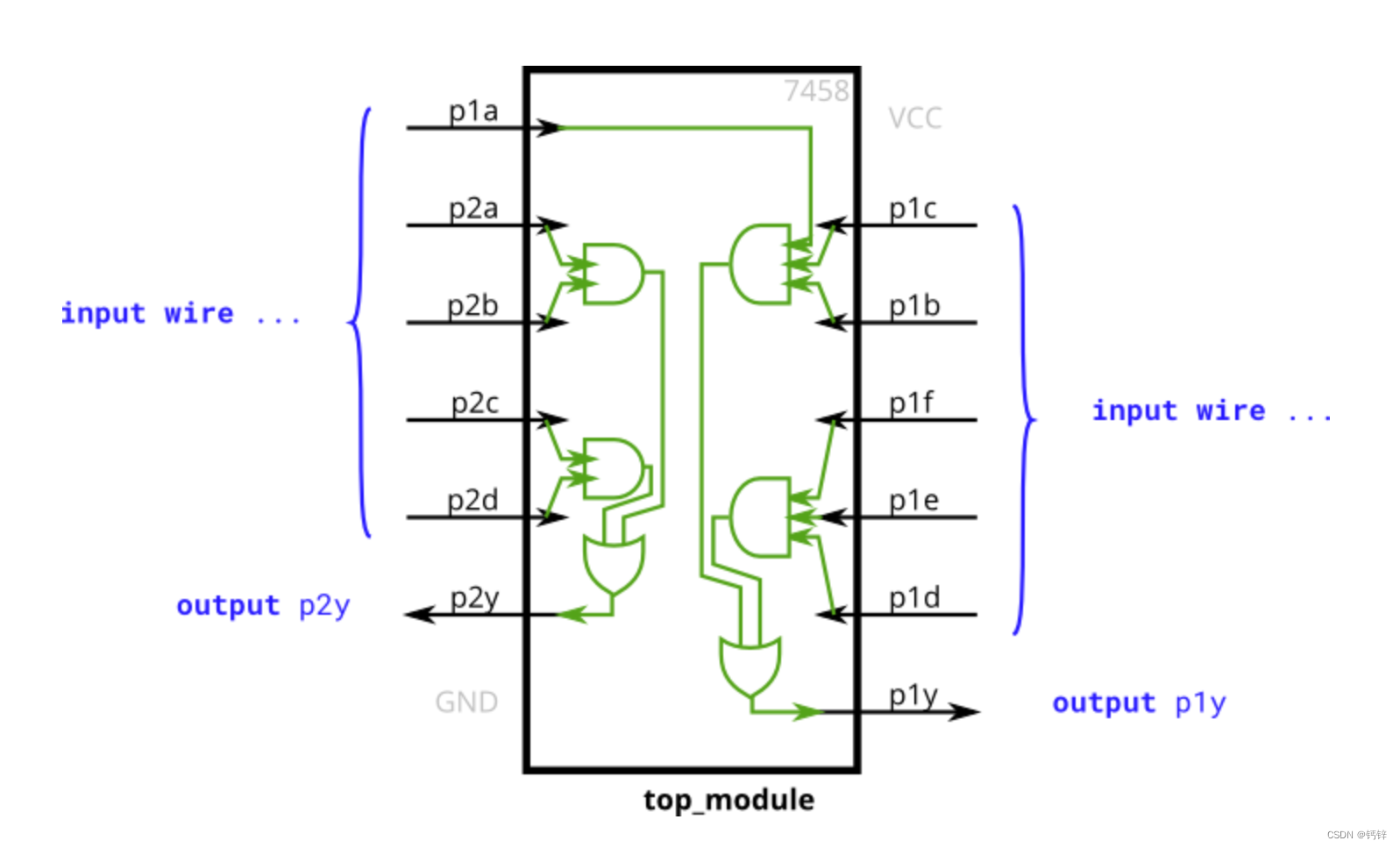

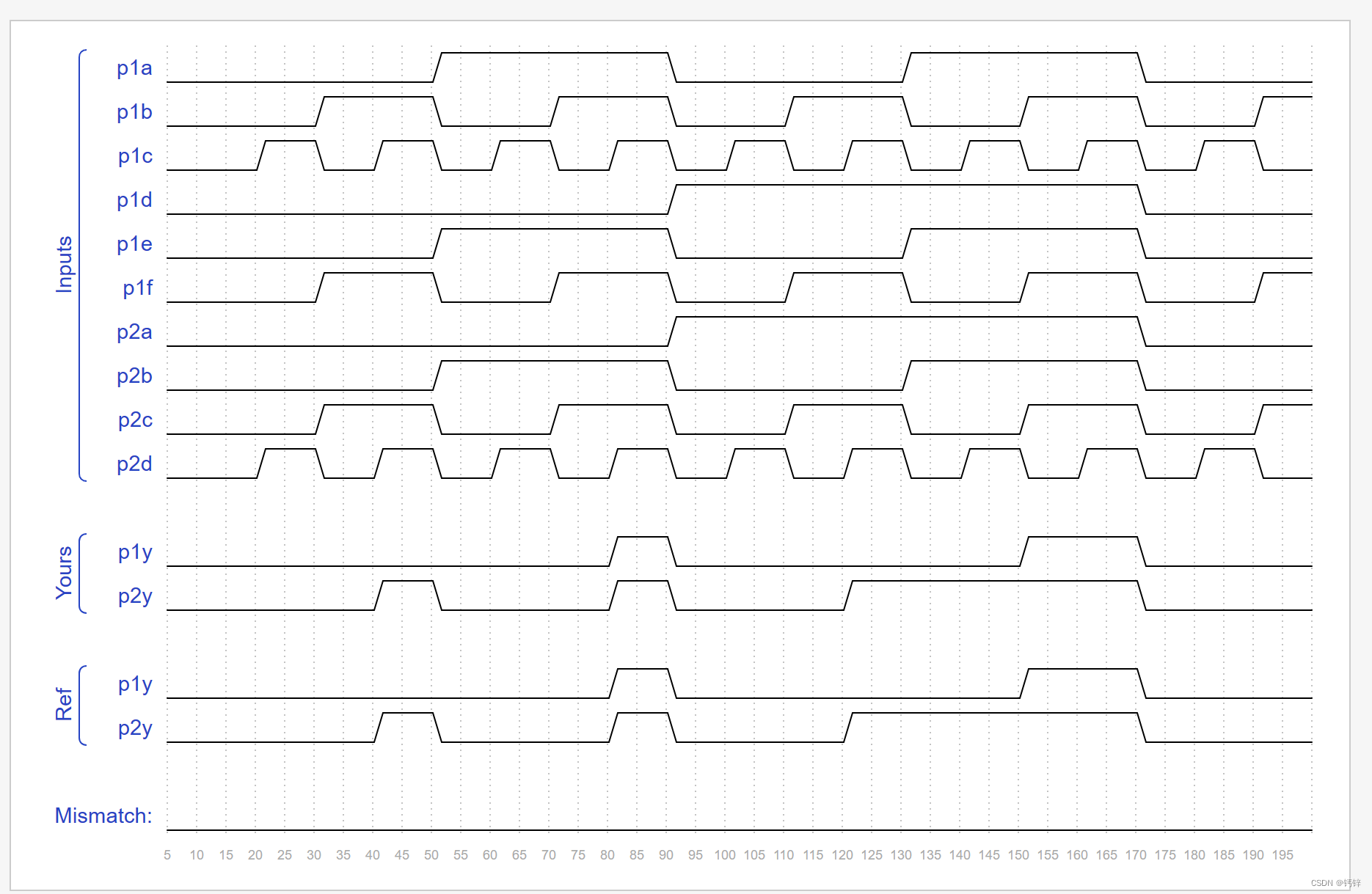

module top_module (

input p1a, p1b, p1c, p1d, p1e, p1f,

output p1y,

input p2a, p2b, p2c, p2d,

output p2y );

assign p1y=(p1a & p1b & p1c) | (p1f & p1e & p1d);

assign p2y=(p2c & p2d) | (p2a & p2b);

endmodule

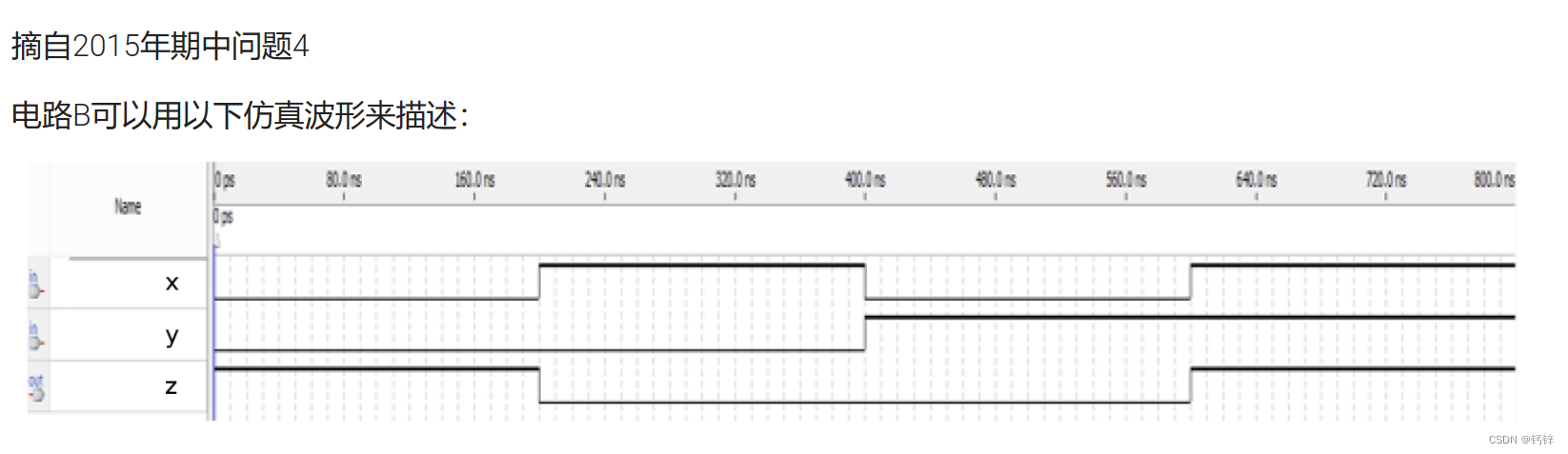

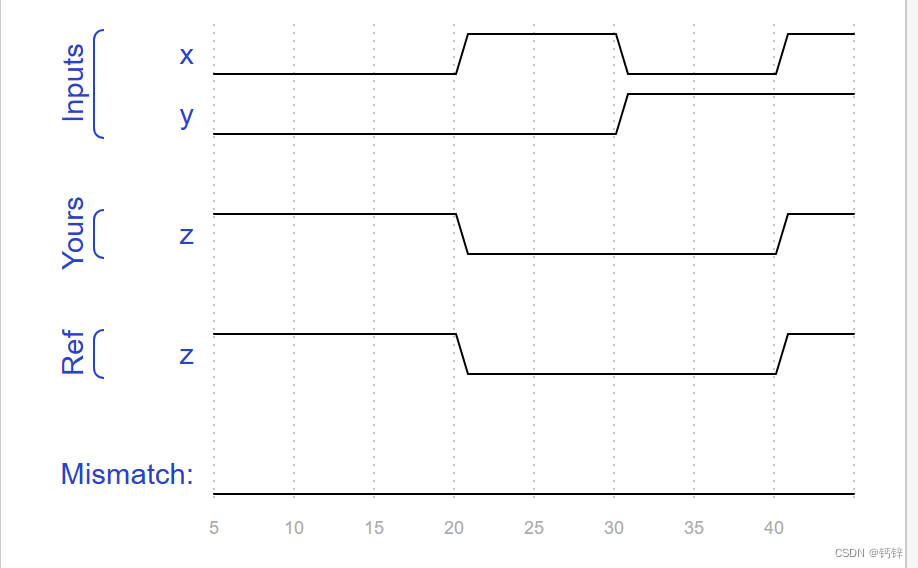

module top_module ( input x, input y, output z );

assign z = ~ (x ^ y);

endmodule

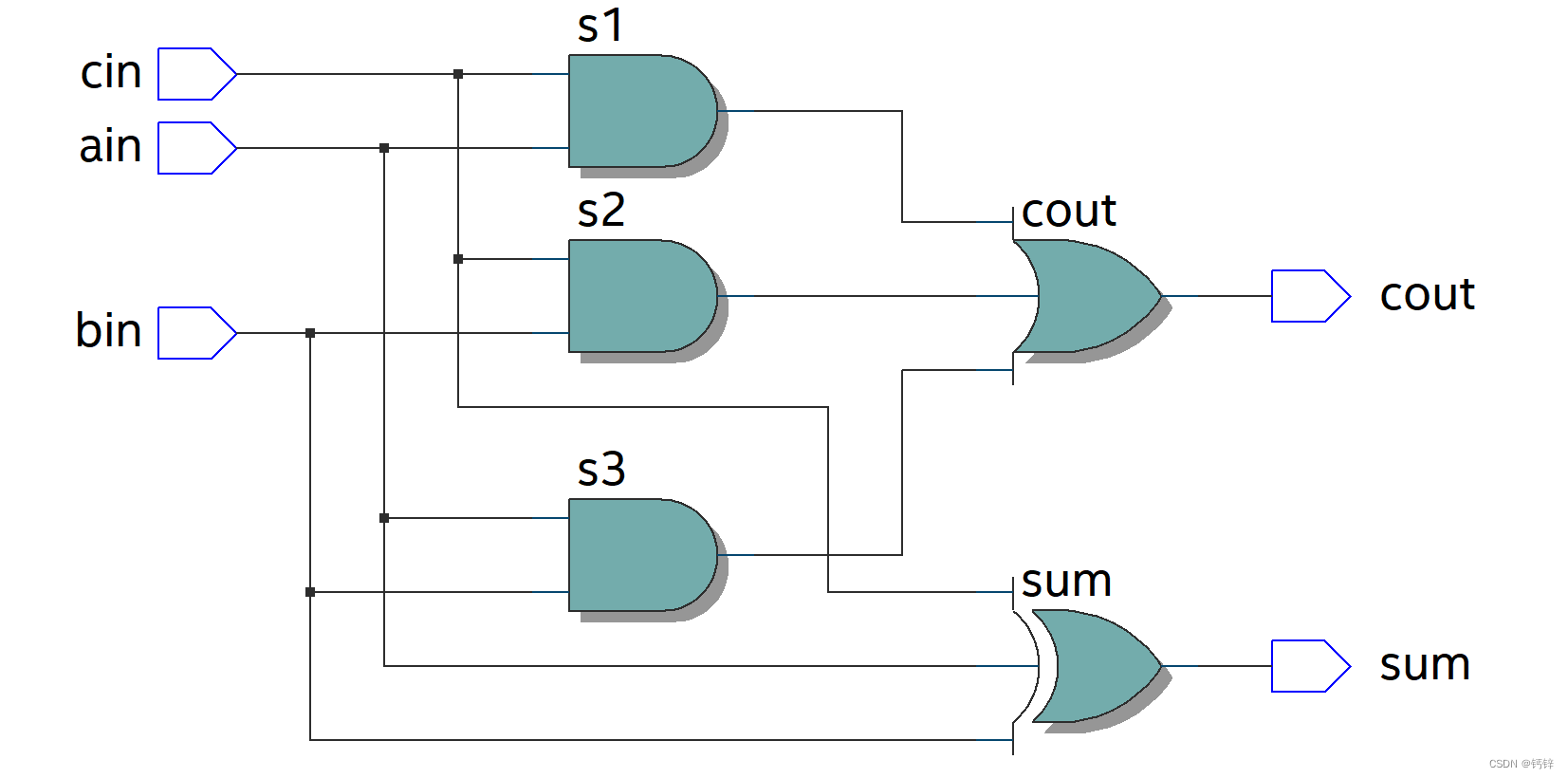

二、全加器设计

1、Logisim

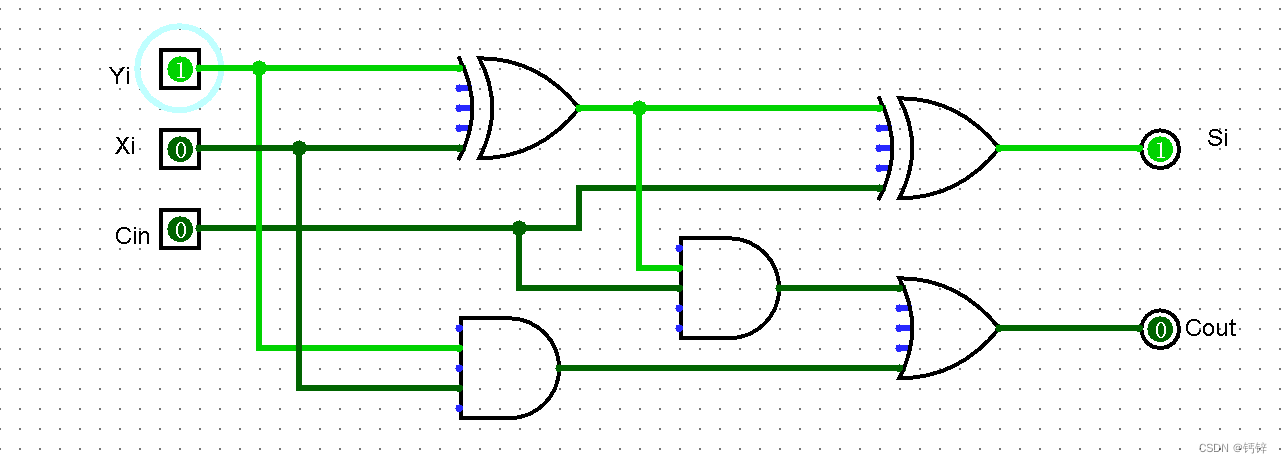

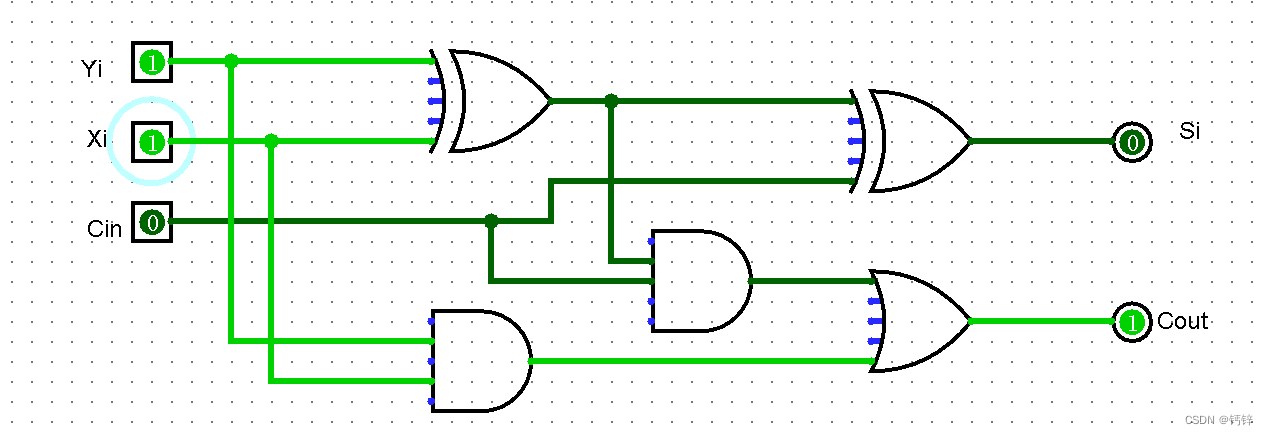

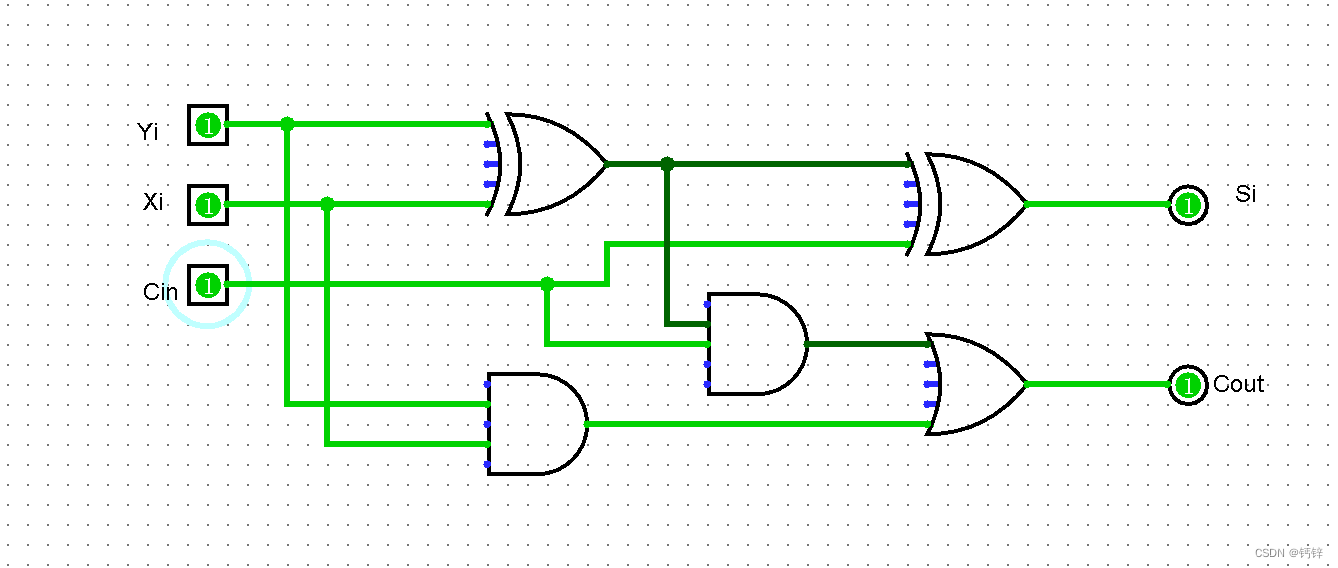

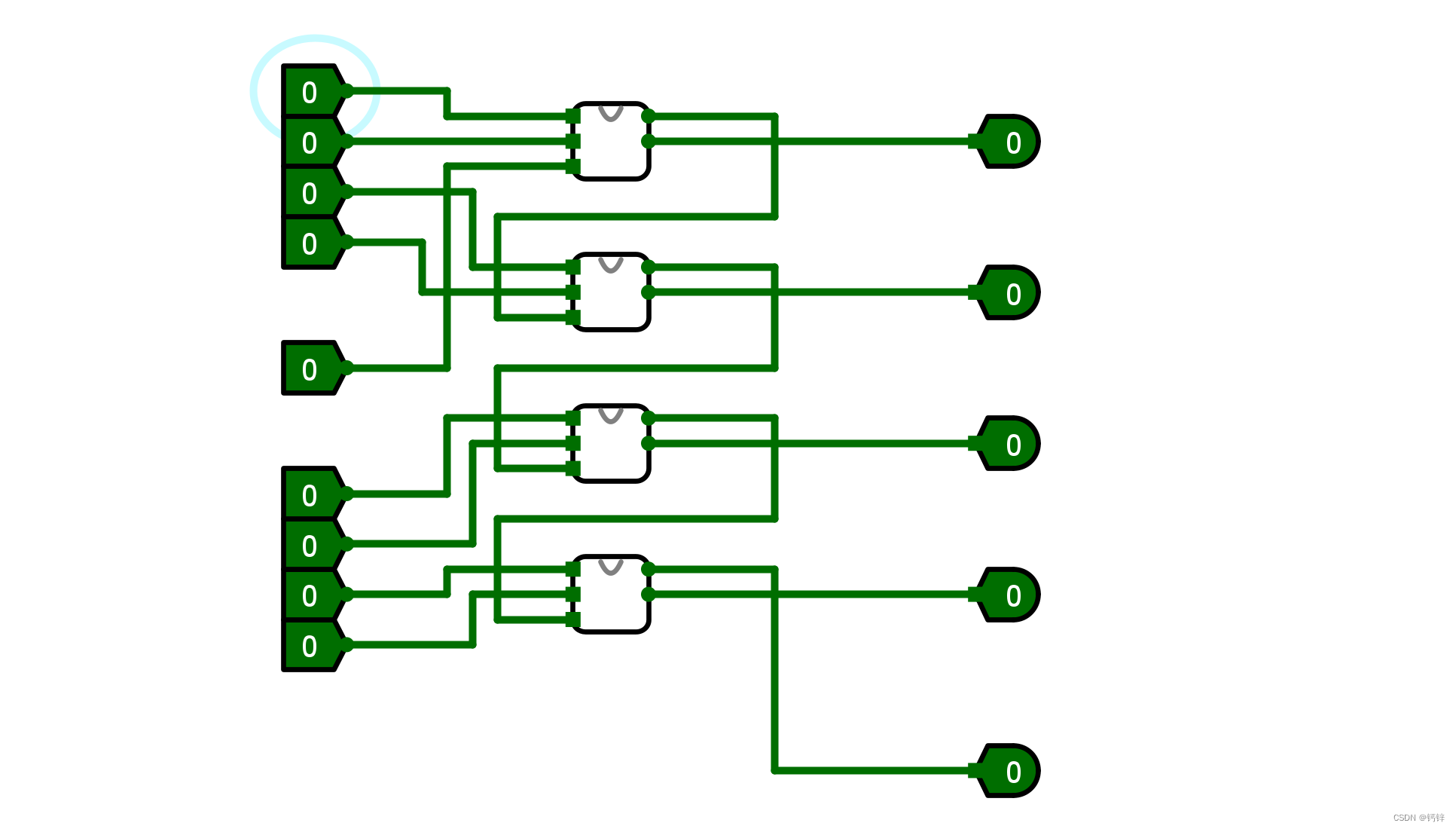

采用门电路组合电路方式完成一个1位全加器的设计,并在Logisim中进行测试。然后封装这个1位全加器为自定义的一个子电路模块(比如名称为OneAdder),然后新建一个项目,用1位全加器串行级联方式完成一个4位全加器的设计,并进行功能测试。

一位全加器,验证

四位全加器

效果

4位全加器

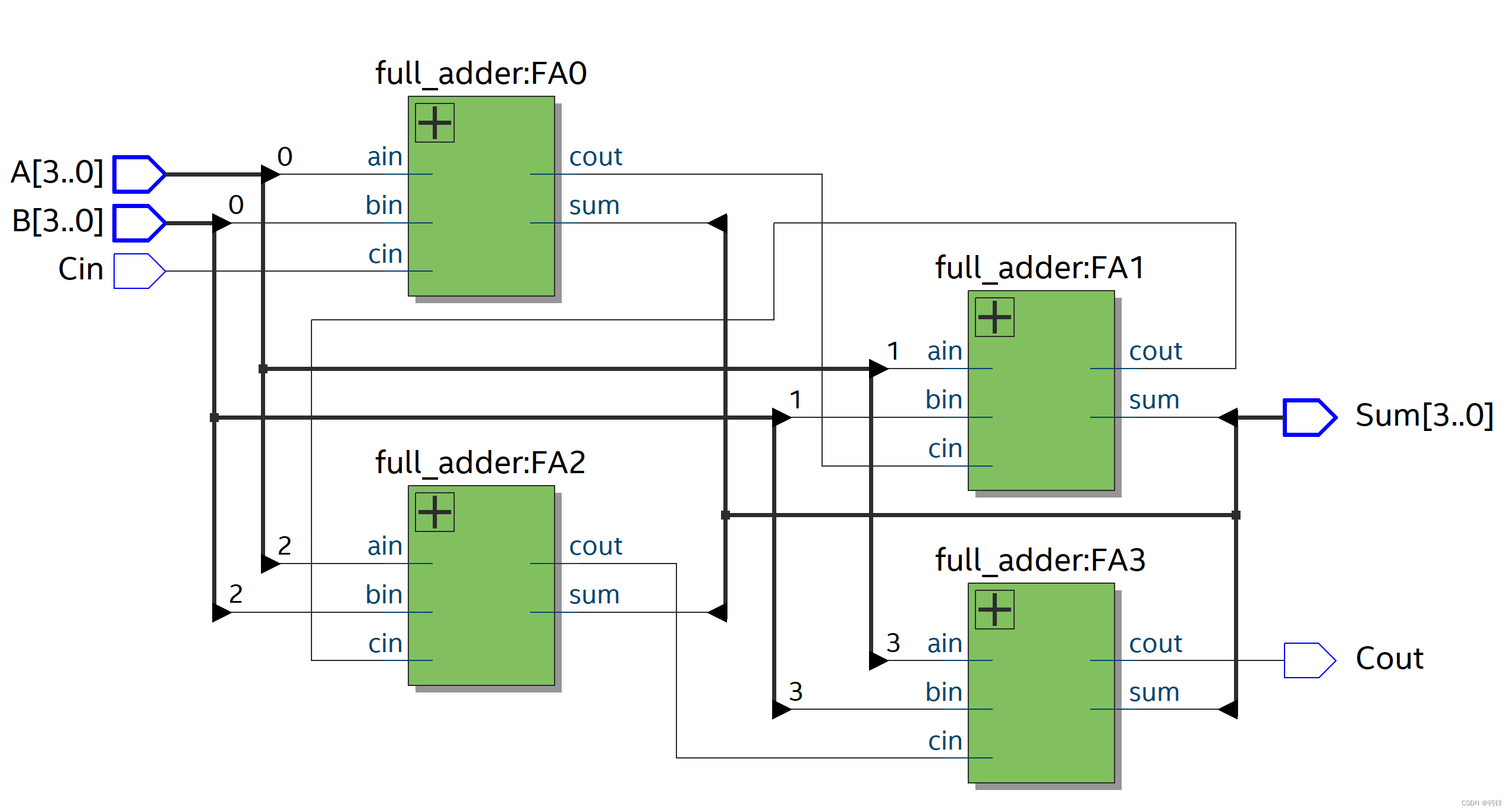

2、Quartus

首先基于Quartus 软件完成一个1位全加器的设计。分别采用原理图输入以及 Verilog编程 这两种设计方法。然后通过4个1位全加器的串行级联,完成一个4位全加器的 原理图设计;再改用 Verilog编程(3种模式:门电路、数据流和行为级描述),完成这个4位全加器设计,并观察Verilog代码编译综合后生成的 RTL电路,与之前电路图设计的4位全加器电路进行对比 。

1)Verilog代码,一位全加器

module full_adder(

//输入信号,ain表示被加数,bin表示加数,cin表示低位向高位的进位

input ain,bin,cin,

//输出信号,cout表示向高位的进位,sum表示本位的相加和

output reg cout,sum

);

reg s1,s2,s3;

always @(ain or bin or cin) begin

sum=(ain^bin)^cin;//本位和输出表达式

s1=ain&cin;

s2=bin&cin;

s3=ain&bin;

cout=(s1|s2)|s3;//高位进位输出表达式

end

endmodule

四位全加器

module Four_Adder(

input [3:0] A, B,

input Cin,

output [3:0] Sum,

output Cout

);

wire c1, c2, c3;

full_adder FA0 (.ain(A[0]), .bin(B[0]), .cin(Cin), .sum(Sum[0]), .cout(c1));

full_adder FA1 (.ain(A[1]), .bin(B[1]), .cin(c1), .sum(Sum[1]), .cout(c2));

full_adder FA2 (.ain(A[2]), .bin(B[2]), .cin(c2), .sum(Sum[2]), .cout(c3));

full_adder FA3 (.ain(A[3]), .bin(B[3]), .cin(c3), .sum(Sum[3]), .cout(Cout));

endmodule

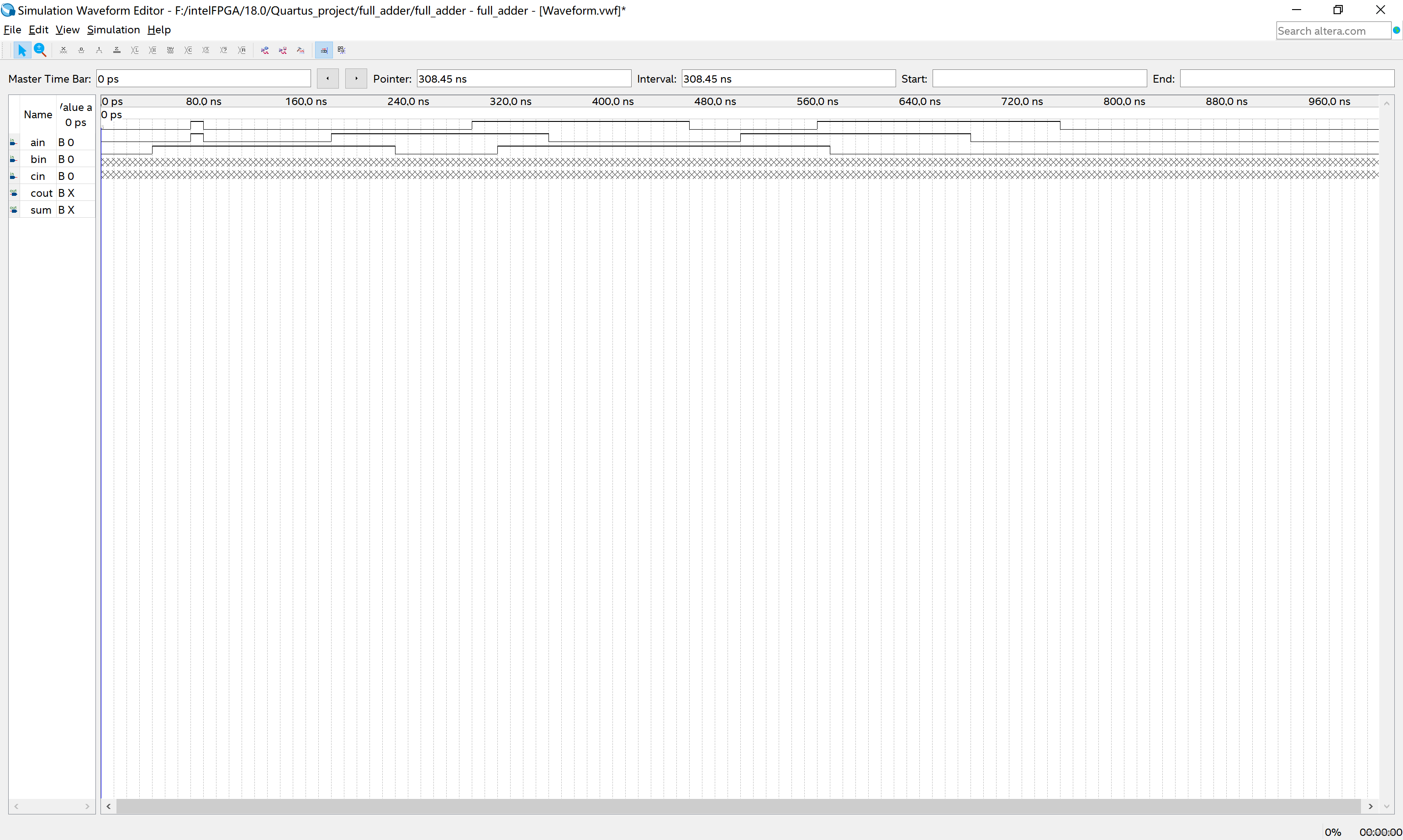

3、仿真及验证

编写 测试激励Verilog模块,用Modelsim 对4位全加器 Verilog模块进行仿真测试,观察仿真波形图。如果仿真波形的逻辑功能正确,就连接的实验室 DE2-115开发板硬件上,完成引脚绑定,烧录,再拨动按钮开关,进行加法器 正确性的验证。

下为一位加法器仿真及验证

验证

一位全加器

1303

1303

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?