定义了CPU和内存之间的传输接口。当CPU和Mem位于不同的chip中,该通道走的是CXL的链路层和物理层,该协议可用于多个不同的内存连接选项,包括当内存控制器位于主机CPU中时,或当内存控制器位于加速器设备内时,或当内存控制器移动到单独的存储芯片时

主机管理设备内存 (HDM) 地址区域提供 3种基本一致性模型:

• HDM-H(仅主机相干):仅用于第 3 类设备

• HDM-D(设备一致性):仅用于依赖 CXL.cache 管理与主机一致性的传统2 型设备。

• HDM-DB(使用反向无效的设备一致性):可用于 2 类设备或 3 类设备

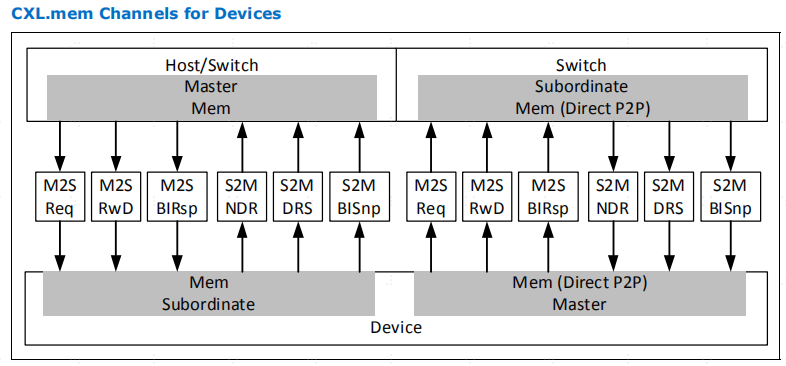

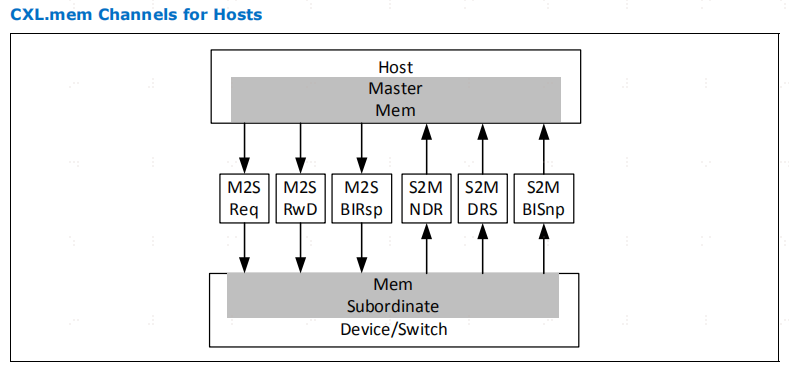

CPU中的一致性引擎认为是CXL.mem协议中的Master(主),Mem device认为是CXL.mem协议中的Suboridinate(从)。Master主要是发起读或写请求,Suboridinate主要是响应这些请求,返回数据或告知写完成。

当Suboridinate是一个加速器的时候,比如GPU,就认为它内部有一个自己的一致性引擎(device coherency engine,DCOH)。DCOH就会用来负责一致性相关的工作,比如基于CXL.mem通道的指令监听device的缓存并且更新元数据(Meta data)字段。

从Master到Suboridinate的事务叫做M2S,从Suboridinate到Master的事务叫做S2M。

在 M2S 事务中,有三种报文类别:

• 不含数据的请求--通称为请求(Req)

• 带数据的申请--(RwD)

• 反向无效响应 - (BIRsp)

同样,在 S2M 事务中,有三种报文类别:

• 无数据响应 - 一般称为无数据响应 (NDR)

• 带数据的响应--一般称为数据响应(DRS)

• 反向无效窥探--(BISnp)

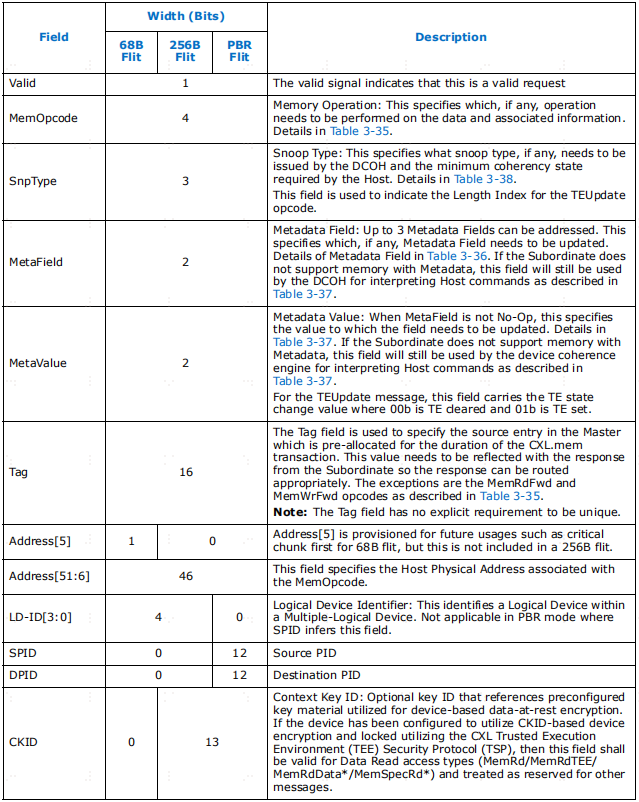

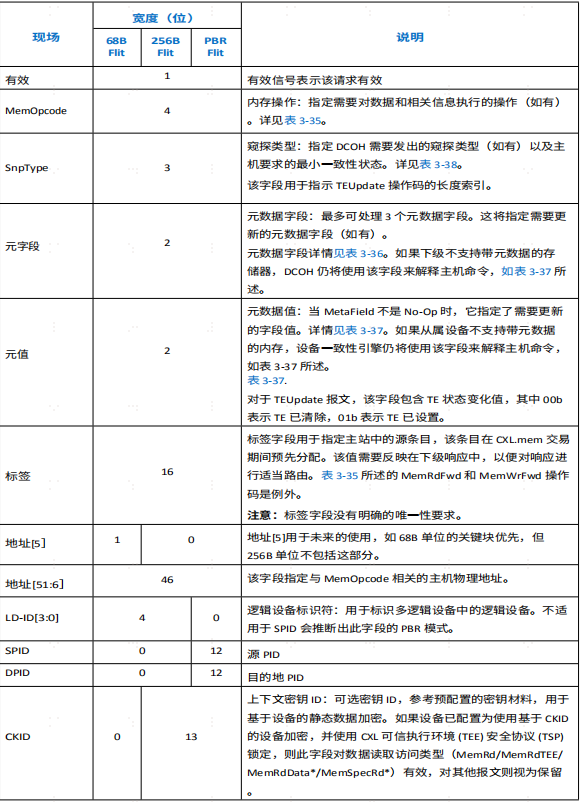

每种报文将支持 3 种变体:68B Flit、256B Flit 和 PBR Flit

CXL.mem Channel

CXL.mem 各通道相互独立工作,以确保向前推进。

支持 HDM-DB 的设备必须支持 BI* 通道(S2M BISnp 和 M2S BIRsp)

用于加速器的直接 P2P CXL.mem

一组额外的 CXL.mem 通道为此类通信提供了支持,其方向与传统的 CXL.mem 相反。这些通道只存在于设备与连接该链路的交换机下游端口之间的链路上。排序要求、报文格式和通道语义与传统 CXL.mem 相同

支持直接P2P.mem 的拓扑要求加速器(请求者设备)和目标 3 型对等存储器设备都直接连接到 PBR 边缘 DSP

之所以需要 PBR 路由,是因为并非所有 CXL.mem 信息都包含足够的信息,HBR 交换机无法确定是在设备与主机之间还是在设备与对等设 备 之间进行路由

使用直接 P2P CXL.mem 进行窥探

使用直接 P2P CXL.mem 接口的设备有可能在 H2D Req 上接收到设备先前通过其 P2P CXL.mem 接口请求的地址的窥探。

例如,如果主机禁用了窥探过滤,就会出现这种情况。反之,设备可能会从对等设备收到 S2M BISnp,以获取其通过主机通过CXL.cache 获取的线路。

使用直接 P2P CXL.mem 接口的设备必须跟踪请求缓存行时使用的接口,并正常响应使用此通道的窥探。如果设备接收到不同接口上的窥探,则应将其视为没有返回 RspIHitI 或 BIRspI 的缓存地址,并且不得更改缓存行状态。

Back-Invalidat Snoop反向无效窥探

为使设备能够实施用于跟踪主机缓存设备内存的包容性窥探过滤器(Snoop Filter),可从设备启动 Back-Invalidate Snoop (BISnp),以改变主机的缓存状态。

"包容性窥探过滤器 "的定义是一种设备结构,用于跟踪高速缓存线粒度主机高速缓存,其大小有限,是设备支持的主机物理地址空间总量的一小部分

在 68B 单位中,只有 CXL.cache D2H 请求流可用于设备连接的内存,以管理与主机的一致性。该流程用于具有 HDM-D 内存属性的地址。该流程的一个主要限制因素是,D2H 请求通道可能会被阻塞,等待 M2S 请求通道的向前推进,这就不允许采用包容性窥探过滤器架构。

对于 HDM-DB 内存区域,BISnp 通道(而不是 CXL.cache)用于解决一致性问题。CXL 主机实施可能会在根端口下面混合使用 HDM-DB 和 HDM-D 设备。

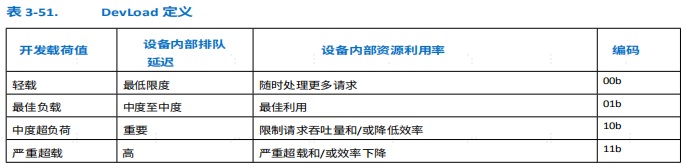

内存QoS遥测

内存QoS遥测是内存设备的一种机制,用于在CXL.mem请求的每个响应消息中指示其当前负载级别(DevLoad)。这使主机能够根据负载级别来衡量对部分设备、单个设备或设备组的CXL.mem请求的速率,从而优化这些内存设备的性能,同时限制结构拥塞。

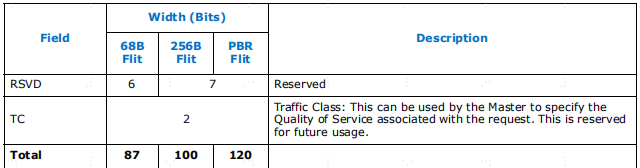

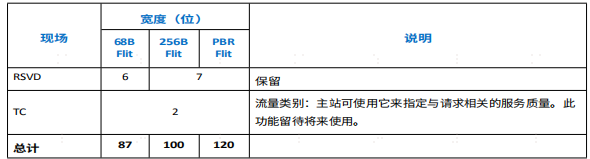

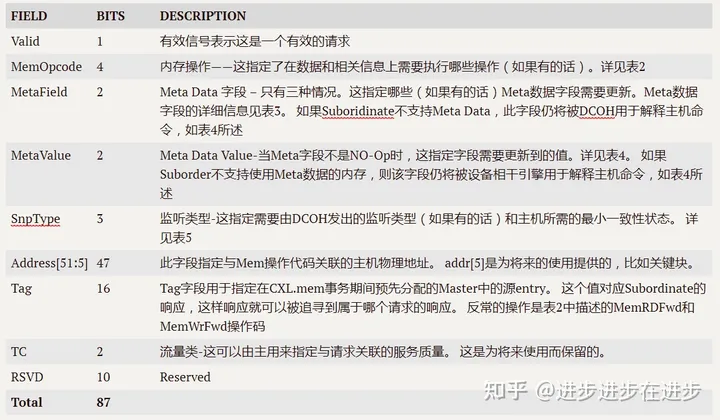

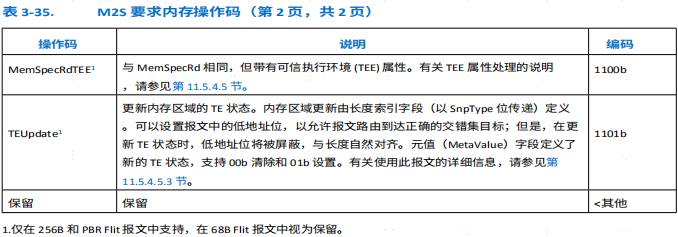

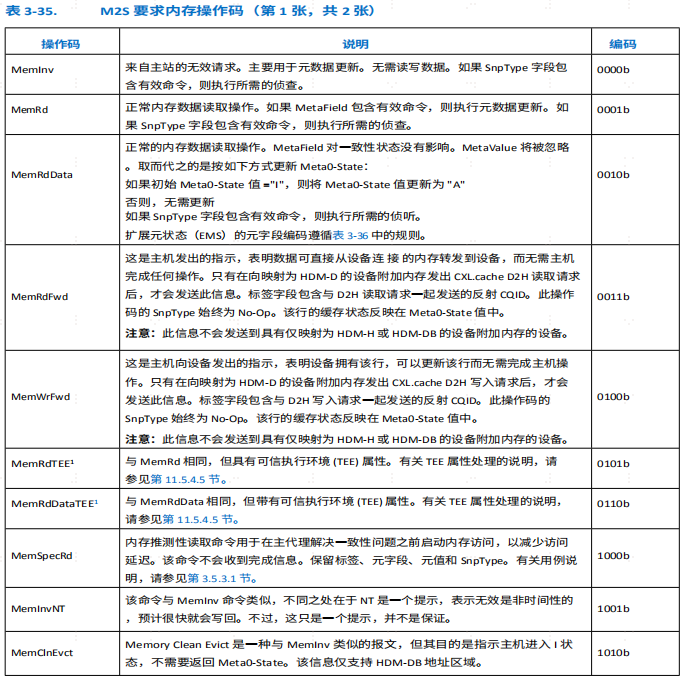

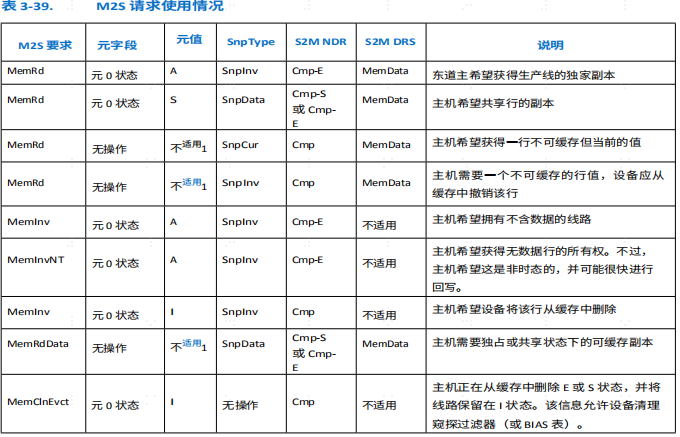

M2S Request (Req)

Req 报文类一般包含从主机到从机的读取、失效和信号

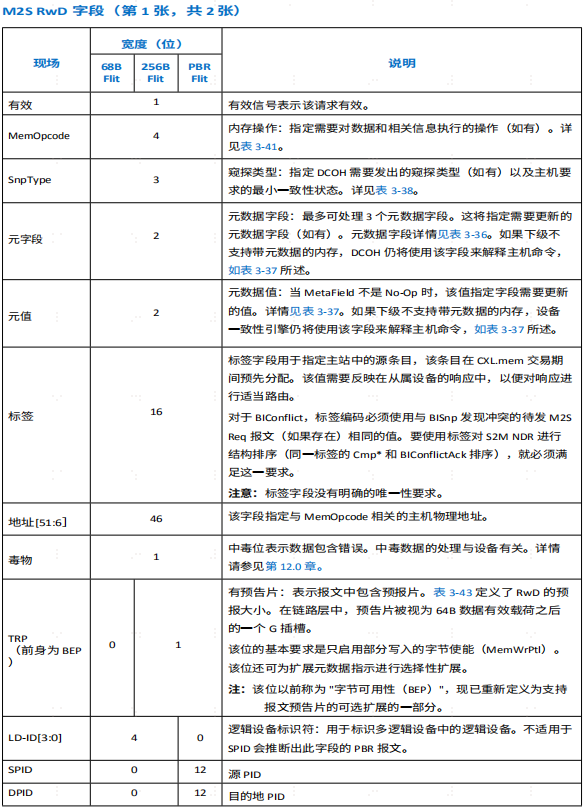

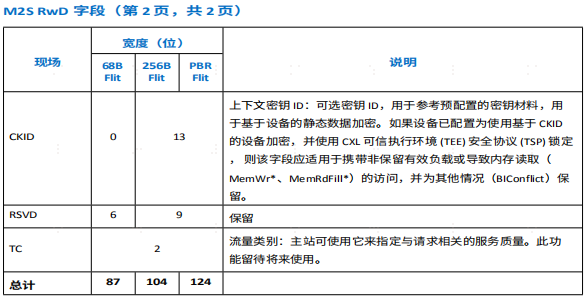

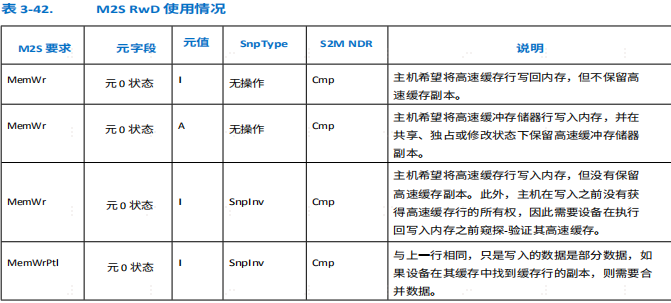

M2S Request with Data(RwD)

带数据的请求(RwD)报文类通常包含主机写给从机的内容。

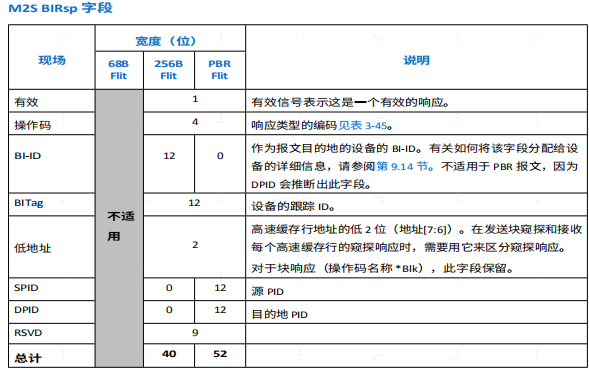

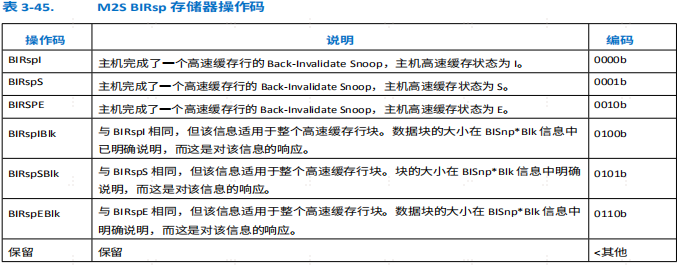

M2S Back-Invalidate Response (BIRsp)

包含主站因 Back-Invalidate Snoops 而发给从属站的响应报文。

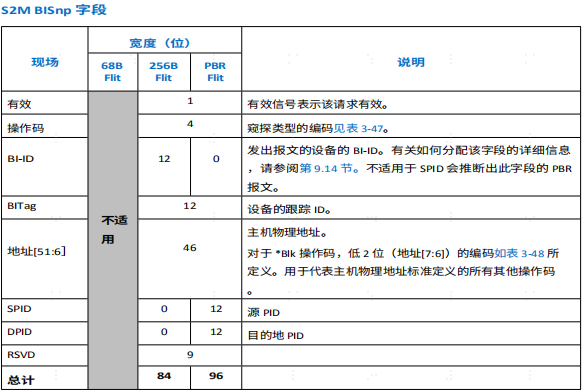

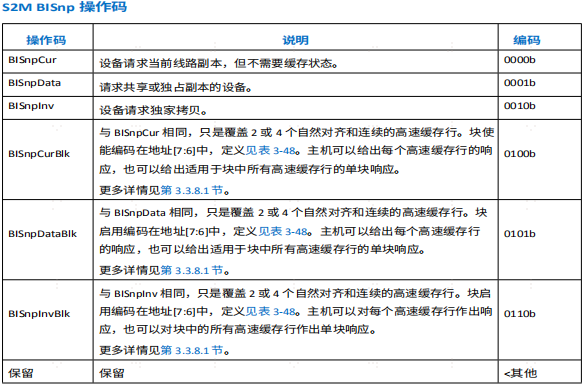

S2M Back-Invalidate Snoop (BISnp)

包含从属设备发送给主设备的 Snoop 报文

Block Back-Invalidate Snoop 阻止反向无效窥探适用于多个自然对齐的连续高速缓存行(2 或 4 个高速缓存行)。主机必须确保为每一行解决一致性问题,并可以任意顺序为每一行发送组合或单独响应。如果存在地址冲突,主机必须分别解决每个高速缓存行的冲突。这种特殊的地址编码仅适用于 BISnp*Blk 报文。

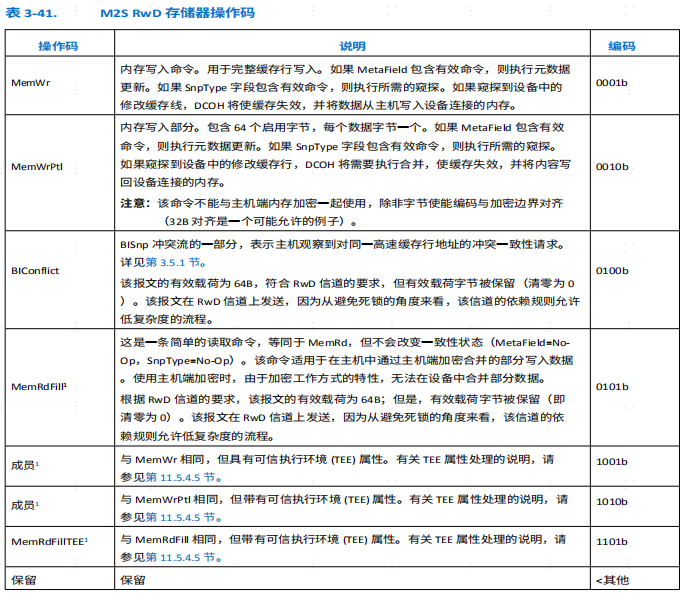

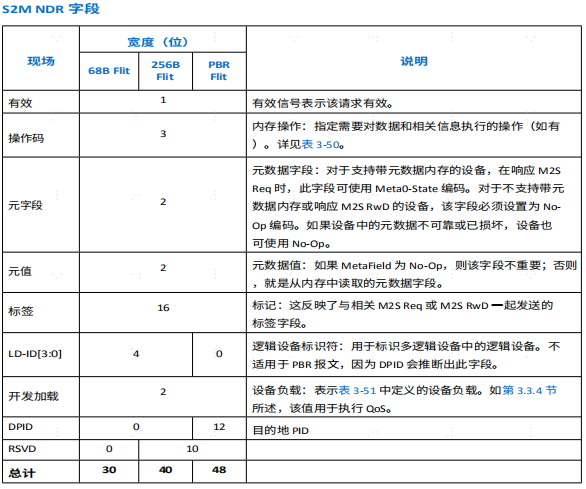

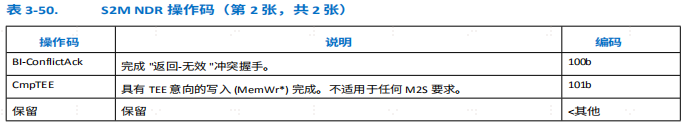

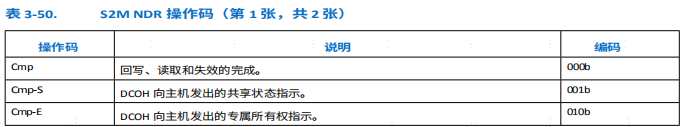

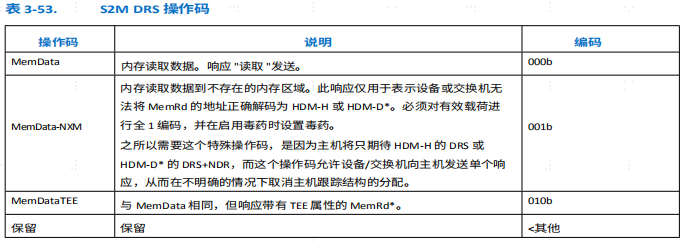

S2M No Data Response (NDR)

NDR 报文类包含从属设备向主设备发送的完成和指示。

![]()

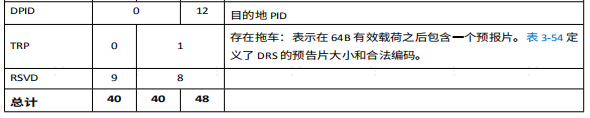

S2M Data Response (DRS)

DRS 报文类包含从属设备向主设备发送的内存读取数据。

![]()

Forward Progress and Ordering Rules

Req 可由 BISnp 对主机进行阻断,但 RwD 不能由 BISnp 对主机进行阻断

Req和RwD消息的每一跳都需要信用值

如果请求和MemRdFwd或MemWrFwd指向相同的缓存行地址,则M2S Req通道中的CXL.mem请求不能发送MemRdFwd或MemWrFwd

NDR和DRS消息需要在源位置预先分配

在CXL.mem上,只有在写入完成后,写入数据才能保证对以后的访问可见

CXL.mem请求需要在设备上进行转发,而不依赖于任何设备启动请求

缓存行的M2S和S2M数据传输不能与其它缓存行交织

"埋藏缓存状态 "是指主站的主代理逻辑(HA)在发送新的 Req 或RwD 消息时为缓存行地址注册的缓存线状态。这种高速缓存状态可能是由主机控制的高速缓存、但不包括 HDM-D/HDM-DB 内存所有者设备的高速缓存。对于允许同一地址有多个未处理请求的实现,必须将可能的未来缓存状态作为埋藏缓存状态的一部分。为避免这种复杂性,建议将每个高速缓存行地址的 Req/RwD 限制为一个

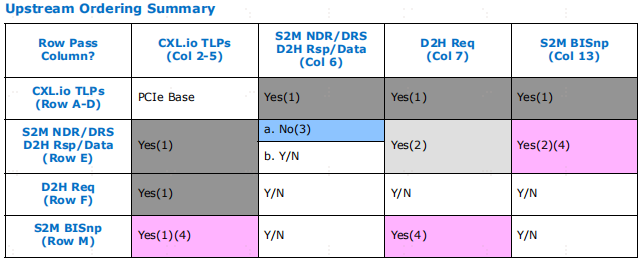

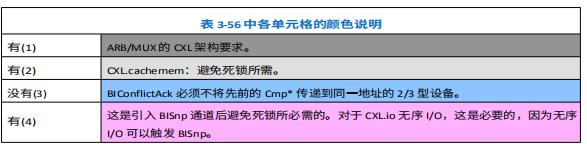

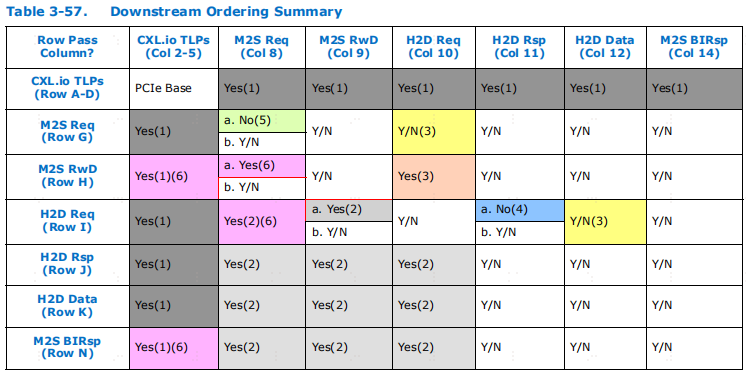

Transaction Ordering Summary

CXL 排序规则

对于 CXL.mem 和 CXL.cache,"上游 "一词指所有 S2M 和 D2H 报文类别的流量,"下游 "一词指所有 M2S 和 H2D 报文类别的流量,与物理传 输 方向无关。

列表示首次发出的报文,行表示随后发出的报文。表项表示两个报文之间的排序关系。

• yes:必须允许第二个报文(行)通过第一个报文(列),以避免死锁。(当阻塞发生时,第二个报文必须通过第一个报文)。

• Y/N: 没有排序要求。第二个报文可以选择通过第一个报文,也可以被第一个报文阻止。

• no:第二个报文不得通过第一个报文。这是支持协议排序模型的要求

Transaction Flows to Device-attached Memory

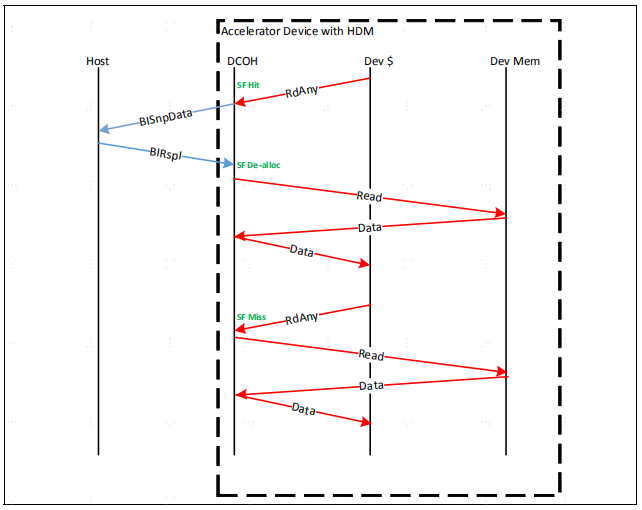

"窥探过滤器"(Snoop Filter,SF)是设备中的一种结构,用于跟踪主机对设备内存的缓存,其大小可能小于主机可能缓存的总和。

在主机缓存满时,通过向主机发送 "Back-Invalidate Snoops "来实现主机缓存。这种强制 BISnp 的满触发被称为 "SF 受害者"。

由 M2S 请求引起的 "SF 缺失 "意味着,如果主机请求线路的缓存副本,设备还必须分配一个新的 SF 条目。在分配SF 条目时,如果 SF 已满,还可能触发不同缓存行地址的 SF 受害者

Type 1和Type 2的事务流

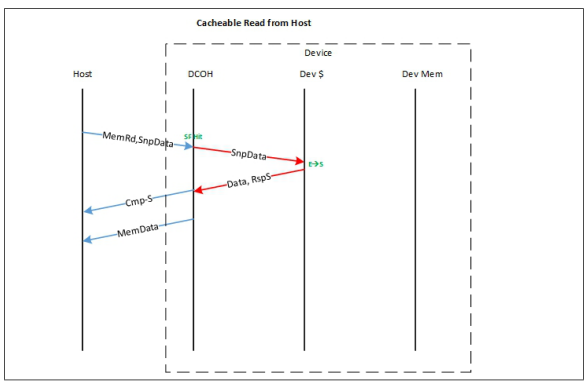

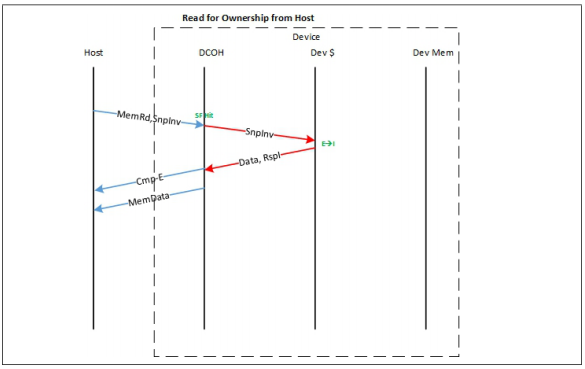

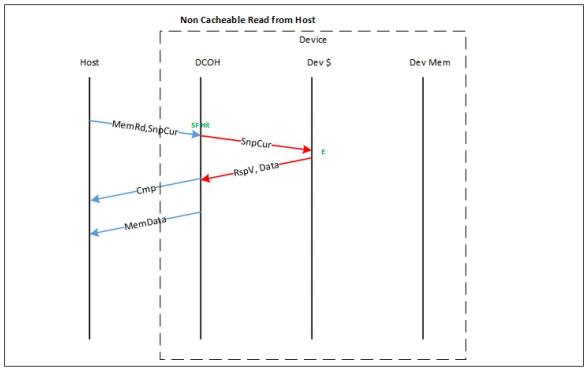

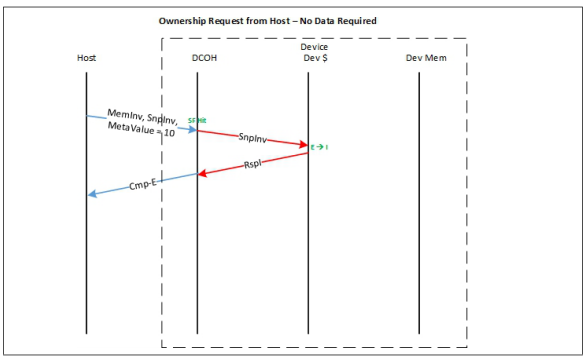

设备内部有一个设备一致性引擎,称作DCOH

DCOH里包含一个监听过滤器,是用来追踪监听设备的缓存

DCOH有一个偏置表查找机制,包含设备连接内存的主机一致性跟踪逻辑,具体实现依赖于设备

主机请求

设备需要向主机提供一致的响应

-

主机发起了一个读请求,去读取device中的某个cacheline,要求该cacheline是非独占的状态。使用的监听类型是SnpData,使用的读取命令是MemRd。在device的DCOH中,看到了该请求,DCOH对应该地址查看是否在device的cache中,如果在,SF Hit(snoop filter 命中)。接着红色箭头的流程是发生在device内部的,将device的该cacheline有E->S(独占状态变为共享状态)。之后将数据和响应发给DCOH,DCOH收到之后,使用Cmp-S回复host,该cacheline在device中目前是shared状态。之后使用MemData将数据发送给host。

-

主机请求获得该行的可缓存独占副本。请求的独占性是通过"SnpInv "语义传达的,该语义要求设备使其缓存失效。在本例中,如果该缓存行出现在device的chche中,设备缓存将状态从 "独占 "降级为 "无效"E->I,并将 "独占 "数据副本返回主机。Cmp-E 语义用于向主机传达线路状态,该cacheline在device中目前是状态。

-

在上面的示例中,主机请求获得该行的不可缓存副本。请求的不可缓存性通过"SnpCur "语义来传达。host要读的数据并不会缓存在host里面的cache中,host只用这数据一次,用完就丢了。在本例中,如果该缓存行出现在device的chche中,设备缓存无需改变其缓存状态,但会提供当前的数据快照。主机被告知不允许使用 Cmp 语义缓存该行。

-

主机要求独占一条线路,而不要求设备发送数据。请求是MemInv类型,监听类型是SnpInv,MetaValue是‘10’(any),主机使用 MetaValue 为10b(任意)的 MemInv 操作码向设备传达了这一要求。缓存访问通过DCOH命中后,device中对应的cacheline由独占状态变为无效状态。它还使用 SnpInv 命令要求设备使其缓存失效。设备将其缓 存作废,并按照 Cmp-E 语义将独占权交给主机。

-

主机希望将包括设备缓存在内的所有缓存中的一行刷新到设备内存中。监听类型是SnpInv和MetaValue 为 00b(无效)的 MemInv 操作码,使缓存无效掉,缓存行由状态M变为无效状态。该缓存数据就会被从缓存中写入到内存中。写入完成之后,回复Cmp响应消息,不需要回复数据给host

-

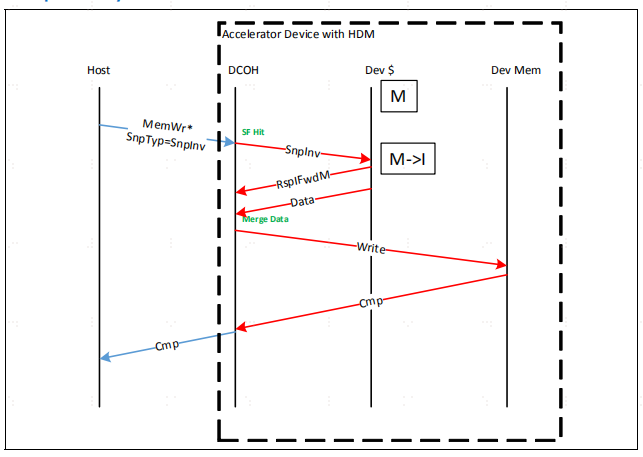

主机发出了弱排序写入(部分或整行)。监听类型是SnpInv类型。设备缓存了该行的副本,导致在将其写回内存并向主机发送 Cmp 指示之前,设备内部进行了合并。这里的 "弱排序 "指的是主机 CPU 中的预期使用模型,即在收到 Cmp 消息后才能保证数据的排序。如果是部分写,则需要合并数据之后将缓存行写入到内存中。写完之后回复完成消息给host。如果是全cacheline的写,用全新的数据代替之前的数据写入到内存中

-

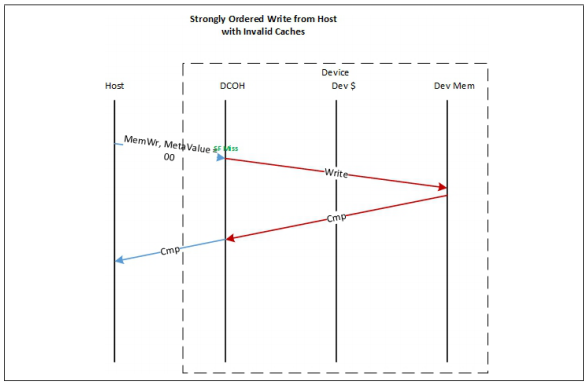

主机在执行写操作时,向设备保证它不再拥有该行的有效缓存副本主机无需窥探设备的缓存,这意味着主机先前已获得了该行的独占副本。元值00b(无效)时,表示保证没有有效的缓存副本。之后该数据会不经过device的cache,而直接被写入到device的内存中。该被写的数据地址,不在device的cache中,也不在host的cache中。与弱指令的最大区别是,不会有DCOH对数据的合并操作

-

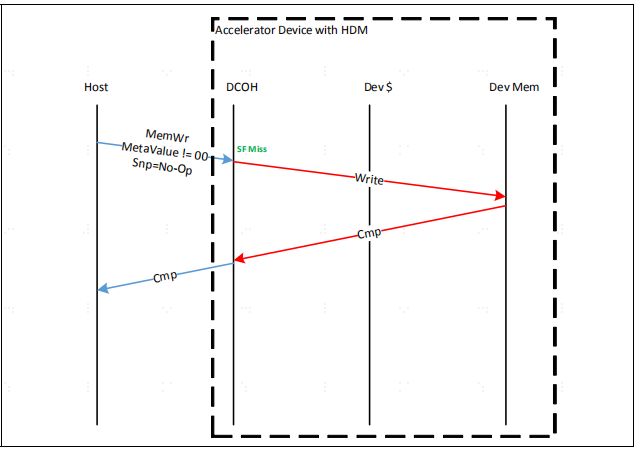

与前一示例相同,只是主机选择在写入后保留行的有效缓存副本。这将通过非 00b(无效)的元值传达给设备

设备请求(主机偏向和设备偏向)

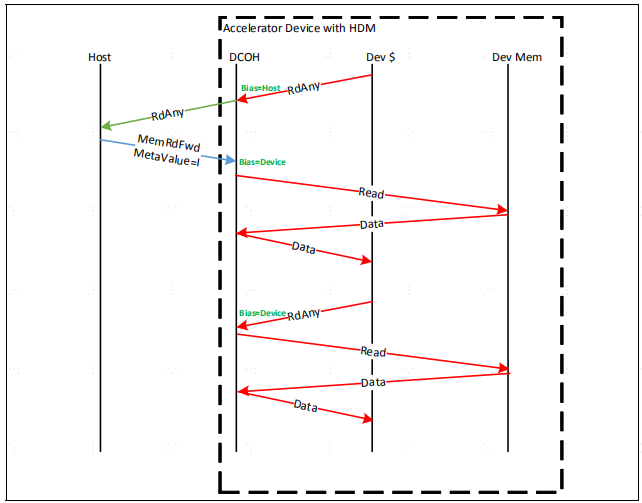

第一个,设备向设备挂载的内存发起读请求,由于配置成主机偏向(图中的紫色字体),设备要向主机发送一致性请求。主机在解析完一致性后,在CXL.mem上发送MemRdFwd以完成事务,此时设备可以在内部完成读取。第二个,配置成设备偏向,设备读取可以在设备内完成,不需要向主机发送请求。

-

设备device发起了一个读请求,去读取设备附属的存储,但是由于该存储处于host偏置模型,所以DCOH接到该请求之后,会向host发起一个读请求,之后host回复一个读请求MemRdFwd,表示device可以直接去读取device附属或挂载存储中的内容了。从存储中读取的数据会直接给device,不会再经过host。

-

由于是device偏置类型,device访问挂载在自己下面的存储不需要经过host,所以可以直接进行读取

-

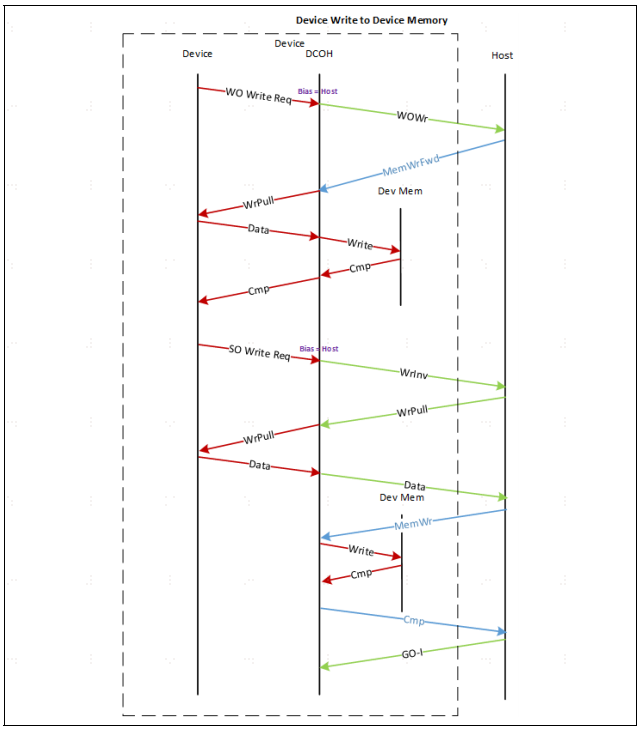

处于host偏置,即device挂载的存储由host管理。上面是弱规则写,下面是强规则写。

主机不再阻止今后对同一行的访问,因此这被视为弱命令写入。在第二个流程中,写入是强有序的。为了保持强有序语义,主机可以在写入完成时阻止对同一行的未来访问

弱规则的写device 存储。具体的写操作必须有host来完成。如果device要访问的地址数据在host的缓存中有副本,那么在写存储之前,device发出写附属存储的请求,经过DCOH,变为CXL.cache D2H通道里的WOWrInv*相关的请求消息,将host的副本无效掉,之后在CXL.cache D2H 数据通道将数据发送到host的缓存中。之后host回应一个写请求,类型是MemWrFwd,意思是host同意了去更新设备附属的存储,接着,device可以通过DCOH直接将数据写到存储中,而数据不需要经过host。此时,可以保证设备挂载的存储中与host缓存中的数据是一致的。

强指令的写device存储。与上面不一样的是,感觉host的参与会更多一点,会由host自己去更新设备附属存储中的内容,而不需要device的参与。device发起写存储的请求,之后DCOH变为CXL.cache D2H通道的写无效请求WrInv,host收到该消息之后,在H2D 响应通道回复WrPull消息,让device直接把数据发给host,host收到数据之后,更新cache中的内容,同时在CXL.mem通道发出请求MemWr,去写设备附属的存储,待host收到写完成消息之后,同过CXL.cache H2D 响应通道回复GO-I消息,表示这样一个写事务彻底完成。此时,host中缓存的数据和设备附属存储中的数据是一致的。

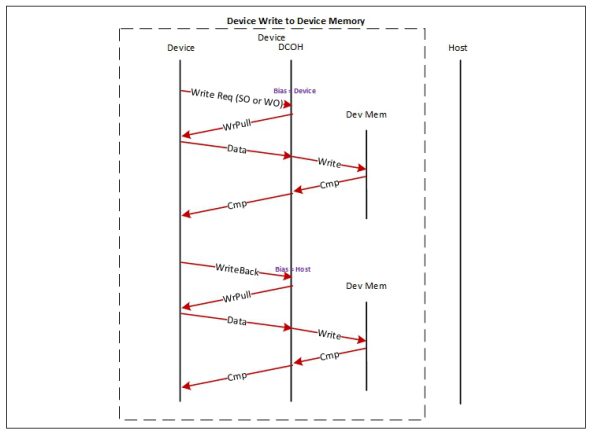

-

在第一种情况下,如果弱序或强序写入发现线路处于"设备偏置"(Device Bias)状态,则写入可完全在设备内完成,无需向主机发送任何指示。第二个流程显示的是设备对设备相连内存的回写。请注意,如果设备正在向设备连接的内存回写,无论偏置状态如何,请求都可以在设备内完成,而无需向主机发送请求。

-

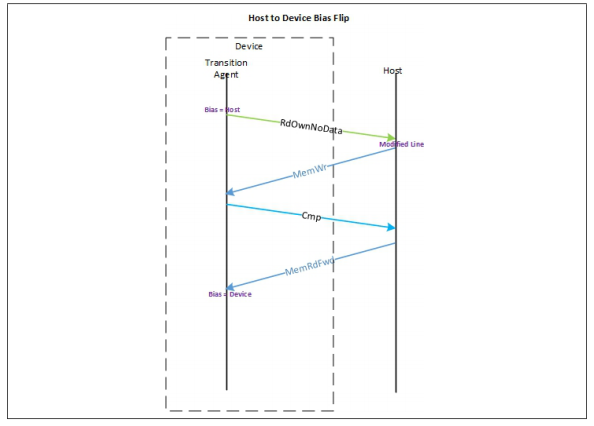

HDM-D 内存的 "偏置翻转 "流程。MemRdFwd 将携带标签中 RdOwnNoData 事务的 CQID。之所以将 RdOwnNoData 完成 (MemRdFwd) 放在 CXL.mem 上,是为了确保主机对同一地址的后续 M2S Req Channel 请求排序在 MemRdFwd 之后。一旦设备收到 MemRdFwd,就能立即获得线路的所有权,而无需监控主机的请求。

Type 2和Type 3的事务流

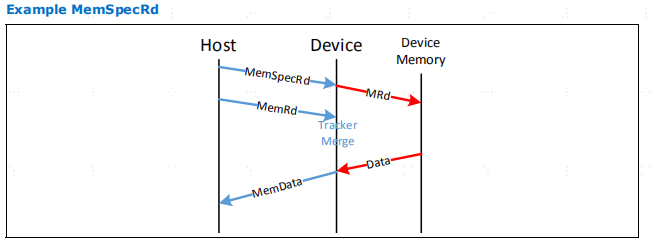

CXL.mem包含一个推测性内存读取命令(MemSpecRd),用于在主代理解决一致性之前启动内存访问。解决完一致性问题后,主机可能会发出请求读取(MemRd,MemRdOwn),设备应与较早的MemSpecRd合并以节省延迟。

当设备正在对同一高速缓存行地址进行另一次内存访问时,可能会观察到MemSpecRd 命令。在这种情况下,建议设备放弃 MemSpecRd。

为了避免性能影响,建议将MemSpecRd命令视为低优先级,以避免其它正常请求访问增加延迟。

在加载条件下,MemSpecRd 可能会影响性能,因为它会增加带宽在检测到内存加载或 CXL 链路加载时,应丢弃所消耗的数据。DevLoad 字段显示的QoS 遥测数据是检测主机或交换机内存加载的一种方法。

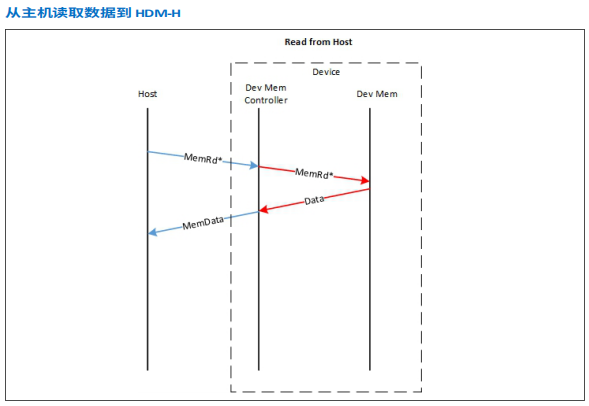

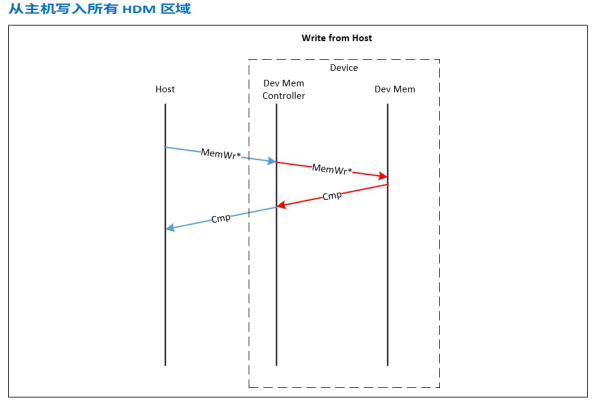

Type 3的事务流

Type 3设备是内存扩展器,它既不缓存主机内存,也不需要主机主动管理设备缓存。因此,Type 3设备没有DCOH代理。主机将这些设备视为分解的内存控制器。到Type 3设备的事务流简化为两个类,即读和写。

M2S读取Type 2设备与Type 3设备的关键区别在于,Type 3设备没有S2M NDR响应消息。

与Type 2设备一样,向Type 3设备的写入完成也需要S2M NDR Cmp消息

1326

1326

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?