1.for循环

循环体为多条语句用begin<循环语句>end

2.while循环

3.forever-disable循环(详细见上图)

4.repeat循环

若repeat表达式中出现x或z,则表达式将被当成0,语句块不被执行。

repeat循环中出现disable立即结束循环,不管循环了几次或是否结束。

5.wait语句

使程序操作流程暂停,直到wait的表达式变为真后,再执行wait语句块

6.begin-end 包含多条语句,语句按顺序执行

fork-join 包含多条语句,语句并行执行

7.BCD加法器

当两数之和大于9时,需加0110进行修正

修正方法F=C4+(S2+S1)

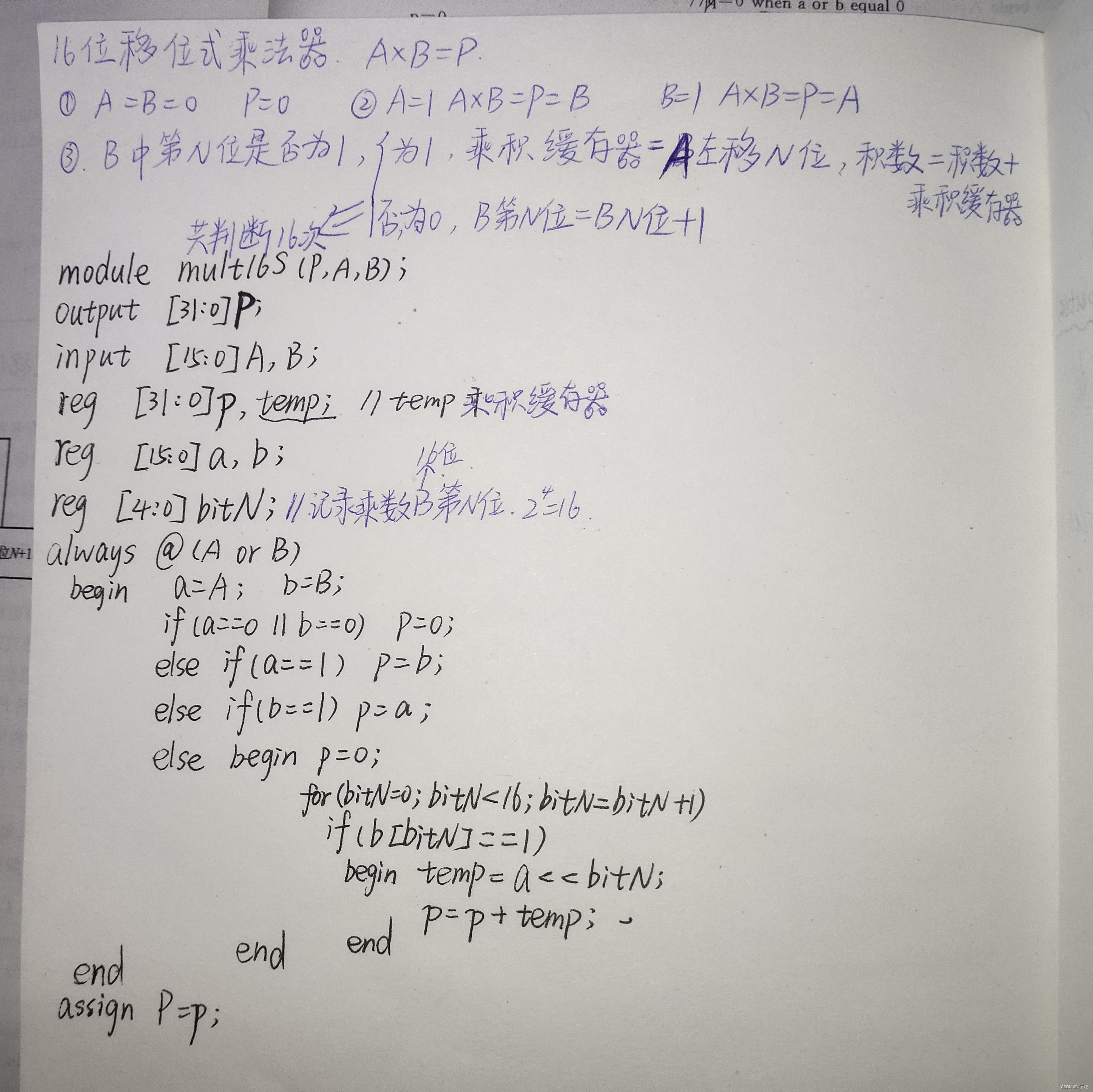

8.16位移位式乘法器

①先判断被乘数与乘数是否为0,若为0,积P为0

②判断被乘数与乘数是否为1,若一个为1,积P等于另一个数

③看乘数的第N位是否为1:

若为1,乘积缓存器等于被乘数左移N位, 乘积等于乘积数加乘积缓存器。

若为0,则乘数第N位等于第N位加1。

附:hdlbits题

循环结构与BCD加法器解析

循环结构与BCD加法器解析

本文介绍多种循环结构的使用方法,包括for、while、forever-disable、repeat等,并探讨了wait语句的功能及应用。此外,还详细解释了BCD加法器的工作原理及其修正方法。

本文介绍多种循环结构的使用方法,包括for、while、forever-disable、repeat等,并探讨了wait语句的功能及应用。此外,还详细解释了BCD加法器的工作原理及其修正方法。

1080

1080

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?