组合逻辑电路用阻塞赋值(=),时序、锁存器电路描述用非阻塞赋值(<=)。

阻塞是串行的,下一时钟几条语句对几个变量的赋值同时完成;非阻塞赋值是并行的,按语句顺序在时钟先后分步完成赋值,非阻塞赋值常用于always块中,不能在assign语句中用<=。

eg.阻塞和非阻塞

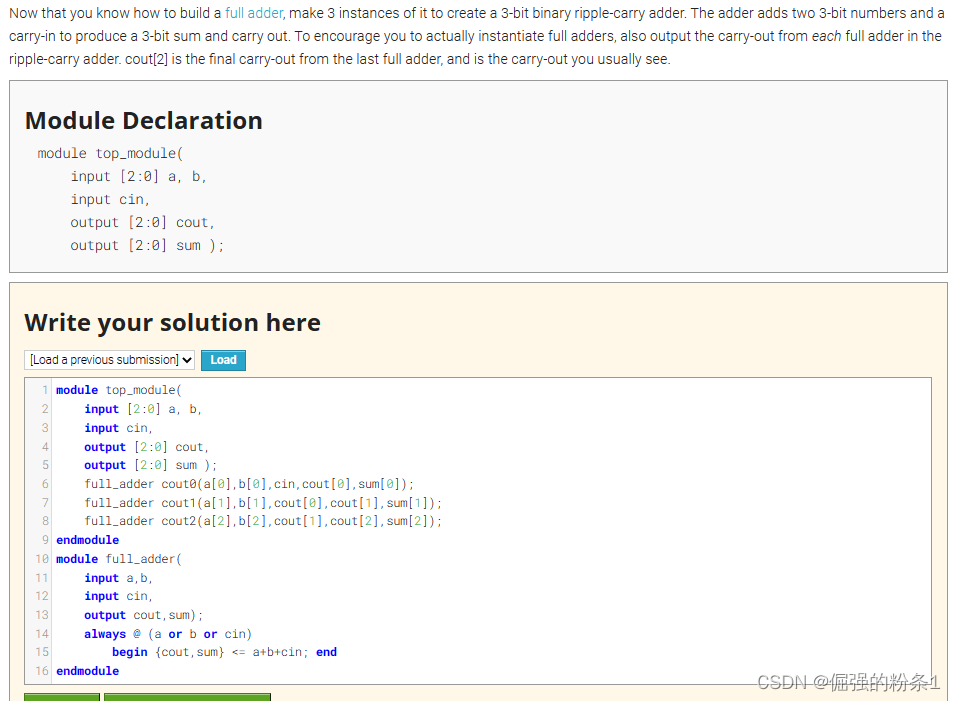

翻译:用一个全加器的3个例化来创建一个3位加法器,其中的cout[3:0]就是记录3个全加器的进位信息(例:cout[2]代表a[2]和b[2]相加是否进位,非所有加数的最终进位)。

在主模块中3条语句需要按顺序一条一条执行(因为cout从低位到高位在不停变化,加法结果受cout变化影响),所以在设计加法器模块时需要用非阻塞语句赋值,而不能直接assign {cout,sum}=a+b+cin.

assign 可以将一种类型变量赋给另一类型变量,不能出现在always语句块中

例:当有一定触发时才想使某一变量值变化,此时须要用reg类型,而这一变量与其他模块实现连接时却是wire类型。

module mem(……

output wire mem_we_o,

……);

……

reg mem_we;

……

assign mem_we_o = mem_we;

always @ (*) begin

if(rst == `Enable) begin

mem_we <= `Disable;

……end

……

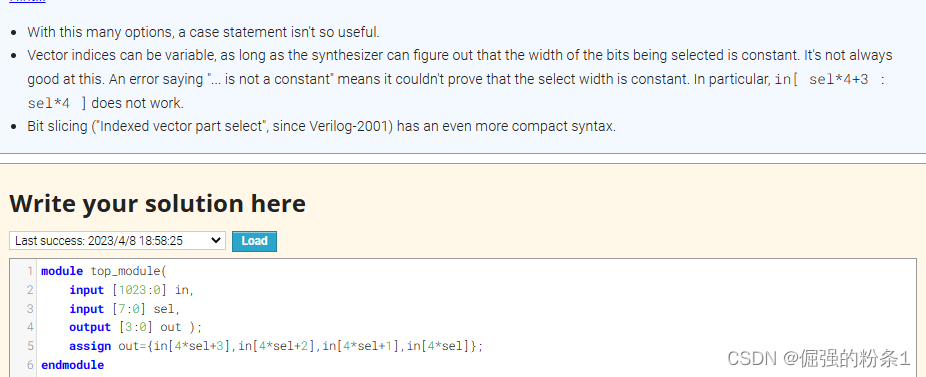

多位宽变量赋值时,位宽必须是常量。

HDLbits Mux256to1v

不能用in[sel*4+3:sel*4]给out赋值

中间变量类型的定义。

一般为wire型。

但如果你想在输出处寄存一下,则必须声明为reg类型;或者使用always时序语句,让信号在时钟边沿才变化,也需要reg类型了。

如果你想assign的话就是直接连接,就是用wire型

1323

1323

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?