文章目录

Circuits:Combinational Logic:Arithmetic Circuits

一、Half adder

设计一个半加器

- RTL代码

module top_module(

input a, b,

output cout, sum );

assign {cout,sum} = a + b;

endmodule

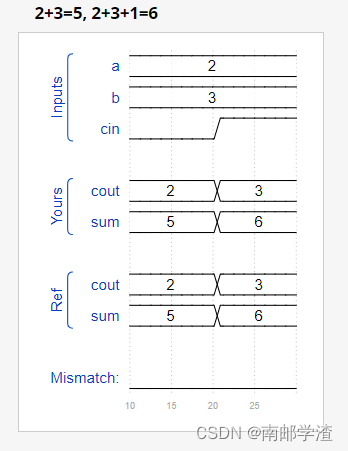

二、Full adder

设计一个全加器,相比较于半加器,全加器有一个进位输入

- RTL代码

module top_module(

input a, b, cin,

output cout, sum );

assign {cout,sum} = a + b + cin;

endmodule

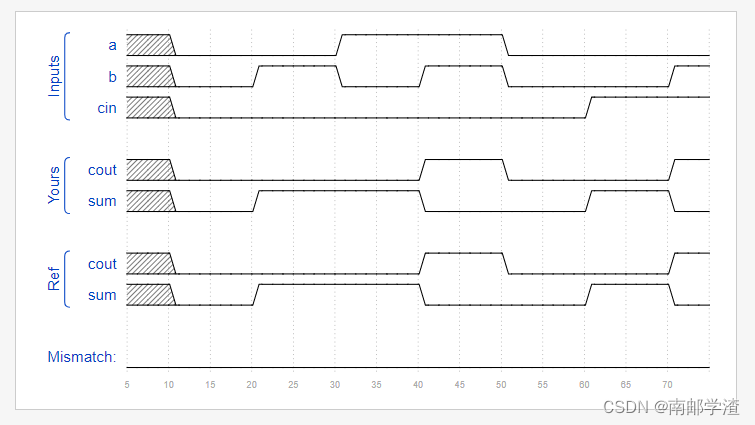

- 仿真波形图

三、3-bit binary adder

设计一个完整加法器

- RTL代码

module top_module(

input [2:0] a, b,

input cin,

output [2:0] cout,

output [2:0] sum );

integer i;

always @(*)begin

cout = 0;

sum = 0;

for(i=0;i<3;i=i+1)

if(i==0)

{cout[0],sum[0]} = a[0] + b[0] +cin;

else

{cout[i],sum[i]} = a[i] + b[i] + cout[i-1];

end

endmodule

- 仿真波形图

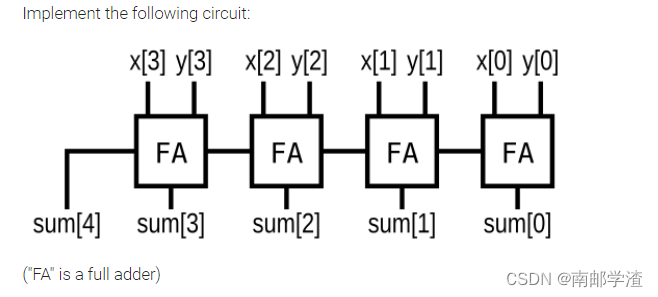

四、Adder

- RTL代码

module top_module (

input [3:0] x,

input [3:0] y,

output [4:0] sum);

wire [2:0]cout;

FA FA_inst1( .a(x[0]), .b(y[0]), .cin(1'b0), .cout(cout[0]), .sum(sum[0]) );

FA FA_inst2( .a(x[1]), .b(y[1]), .cin(cout[0]), .cout(cout[1]), .sum(sum[1]) );

FA FA_inst3( .a(x[2]), .b(y[2]), .cin(cout[1]), .cout(cout[2]), .sum(sum[2]) );

FA FA_inst4( .a(x[3]), .b(y[3]), .cin(cout[2]), .cout(sum[4]), .sum(sum[3]) );

endmodule

module FA(

input a, b, cin,

output cout, sum );

assign {cout,sum} = a + b + cin;

endmodule

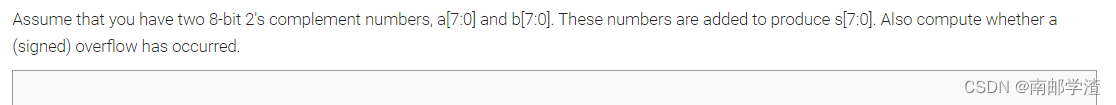

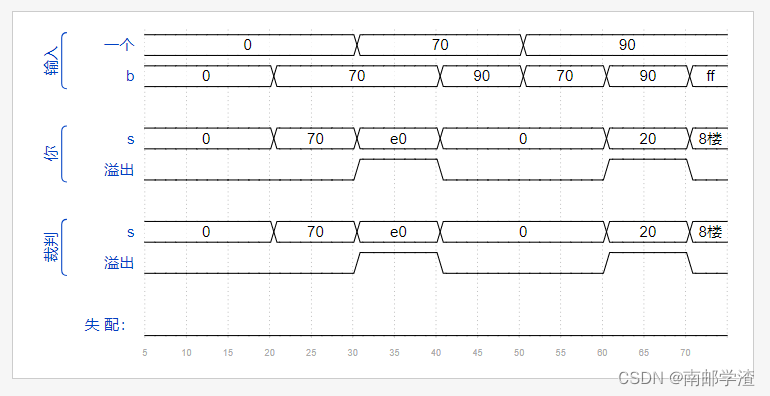

五、Signed addition overflow

设计一个有符号数的加法器,同时判断是否溢出

判断溢出的方法:两个加数最高位相同,且与和数最高位不同

- RTL代码

module top_module (

input [7:0] a,

input [7:0] b,

output [7:0] s,

output overflow

); //

assign s = a + b;

assign overflow = (a[7] & b[7] & ~s[7]) | (~a[7] & ~b[7] & s[7]);

endmodule

- 仿真波形图

六、100-bit binary adder

设计一个一百位的二进制加法器

- RTL代码

module top_module(

input [99:0] a, b,

input cin,

output cout,

output [99:0] sum );

assign {cout,sum} = a + b + cin;

endmodule

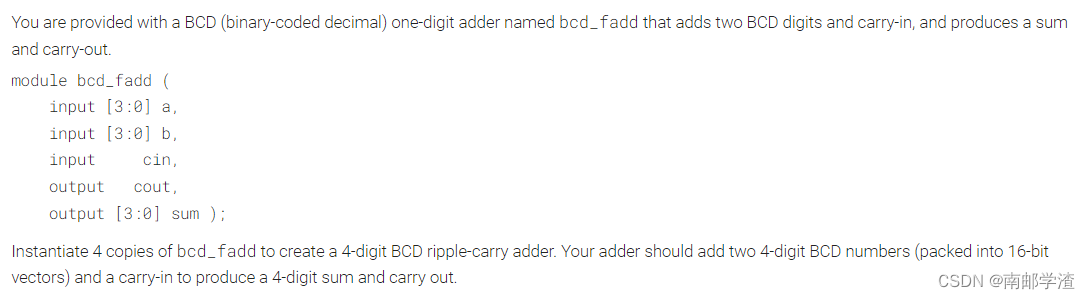

七、4-digit BCD adder

使用已经编辑好的一位BCD码加法器实例化进行四位BCD码加法器设计

- RTL代码

module top_module (

input [15:0] a, b,

input cin,

output cout,

output [15:0] sum );

wire cout1,cout2,cout3;

bcd_fadd adder_inst1(.a(a[3:0]), .b(b[3:0]), .cin(cin), .cout(cout1), .sum(sum[3:0]) );

bcd_fadd adder_inst2(.a(a[7:4]), .b(b[7:4]), .cin(cout1), .cout(cout2), .sum(sum[7:4]) );

bcd_fadd adder_inst3(.a(a[11:8]), .b(b[11:8]), .cin(cout2), .cout(cout3), .sum(sum[11:8]) );

bcd_fadd adder_inst4(.a(a[15:12]), .b(b[15:12]), .cin(cout3), .cout(cout), .sum(sum[15:12]) );

endmodule

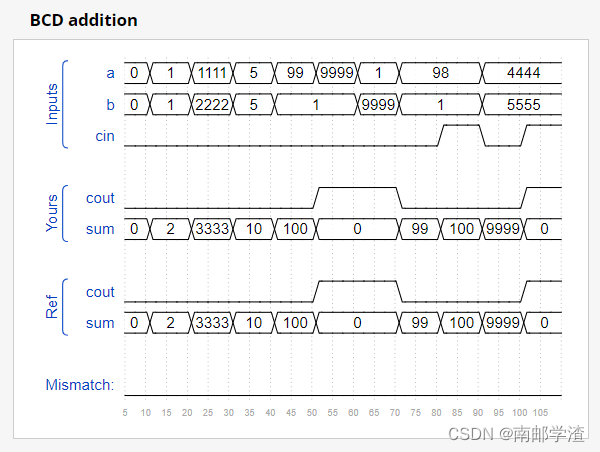

- 仿真波形图

6825

6825

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?