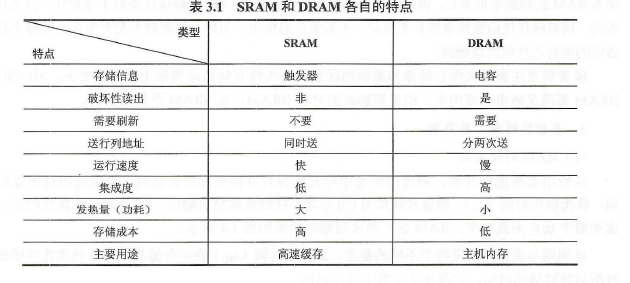

SRAM和DRAM

静态随机存储器(SRAM)的存储单元是使用双稳态触发器来记忆信息,因此信息被读出后,它仍保持原状态(非破坏性读出)。

动态随机存储(DRAM)利用的是电路栅极上的电容来存储信息,通过充放电来实现信息记录。

DRAM电容上的电荷一般只能维持1-2ms,因此每隔一段时间必须刷新,不然数据就会丢失。一般取刷新周期为2ms。

假设DRAM内部结构排列为128×128,即有128行×128列存储单元,读写周期为0.5μs。现在有如下几种方法来实现刷新:

方法一,每次读写完都刷新1行→此时存取周期成1μs

方法二,2ms内集中安排全部刷新→存取周期还是0.5μs,有一段时间专门用于刷新(1936μs读写,64μs刷新)

方法三(异步刷新),2ms内每行刷新一次即可→2ms内产生128次刷新请求,2ms/128=15.6μs,15.6μs内又有0.5μs死时间(刷新时无法访问寄存器,叫死时间)

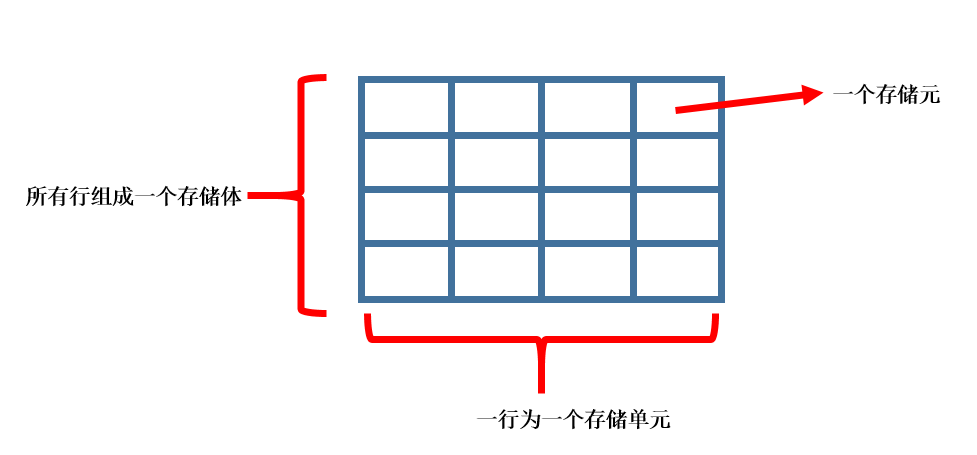

单体多字存储器和多体并行存储器

上图为简单的单体多字存储器示意。每一个存储元存储一个字,一个存储单元存储若干个字,但实际只有一个存储体。(这里存储一个字并不一定指32bit数据,每一个存储元存储的数据长度都可以叫一个存储字,都是byte的整数倍)

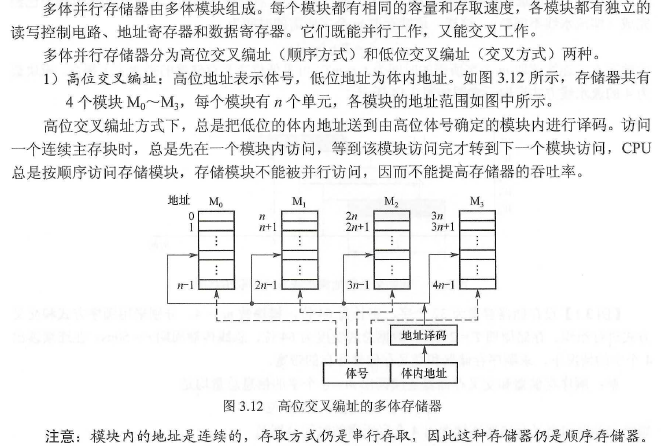

对于多体并行存储器,主要分为以下两类:

由于计算机中地址的访问都是连续的,所以,对于高位交叉编址,总是先访问完一个存储体,才能继续访问下一个存储体。而对于低位交叉编址,可以并行访问不同的存储体,采用流水线的方式可以极大提高带宽。

一些零散点

复杂指令系统计算机CISC(complex instruction system computer),常见于pc,笔记本电脑;

精简指令系统计算机RISC(reduced instruction system computer),常见于手机。

984

984

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?