Vector

向量用于使用一个名称对相关信号进行分组,以便于操作。例如,wire [7:0] w;声明一个名为 w 的 8 位向量,相当于有 8 条单独的连线。

Declaring vectors

![]()

常用类型为wire或者reg;如果有需要可以在前面加入端口类型input或output。如:

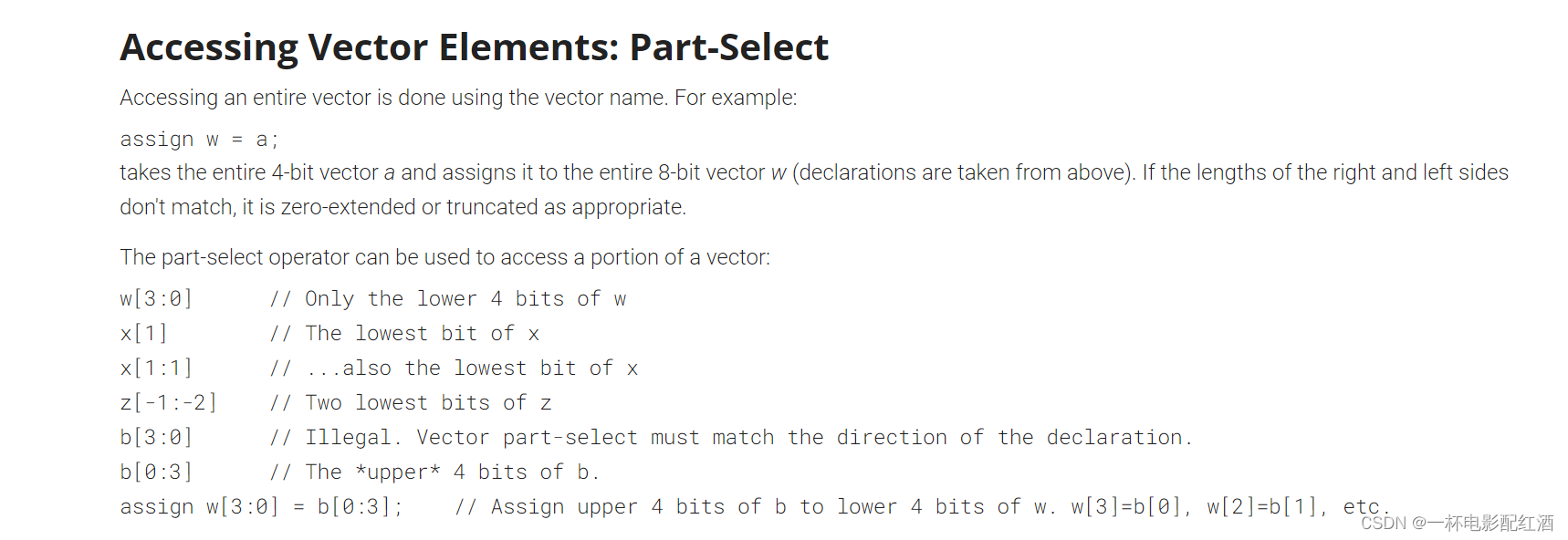

vector里的任一字节都可以赋值给变量

长的数组不能被赋值到短的数组,短数组赋值到长数组时,如果右侧和左侧的长度不匹配,则将其零扩展或截断。

例题1:

例题1:

程序1:

Timing diagram 1:

字节顺序交换

一个32比特的vector可以看做包含4字节。

这种操作常用于交换数据片段字节顺序,例如在小端 x86系统和许多 Internet 协议中使用的大端格式之间。

程序2:

Timing diagram2:

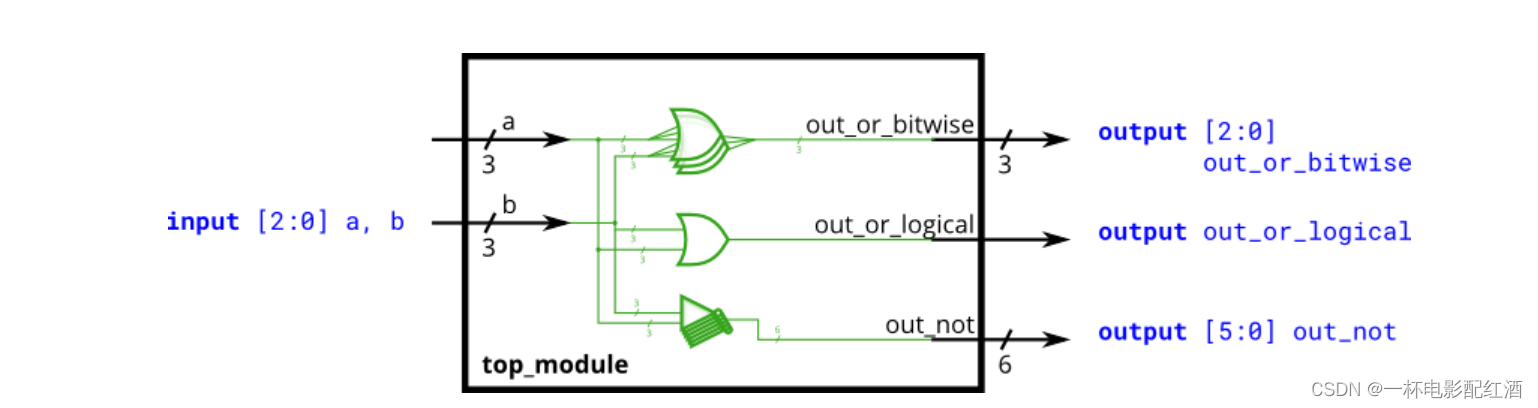

按位运算和逻辑运算的区别

两个N比特的按位运算是通过运算vector的每一位来得到一位N比特的输出。逻辑运算则是通过布尔逻辑代数(真为1,假为0)得到一个1比特的输出。

题目3:

代码3:

Timing diagram3:

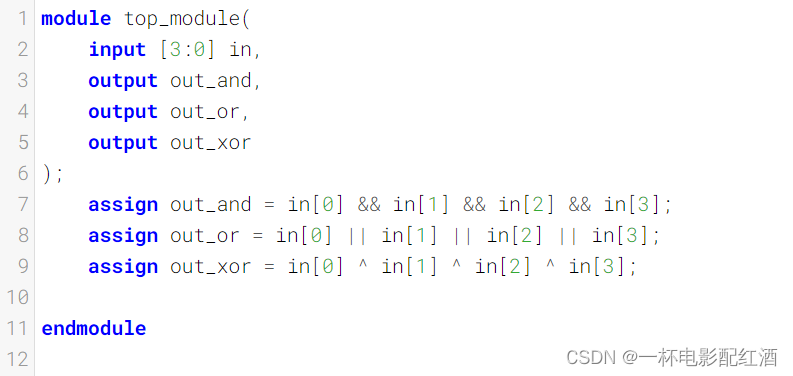

四输入组合电路逻辑运算

题目4:

代码4:

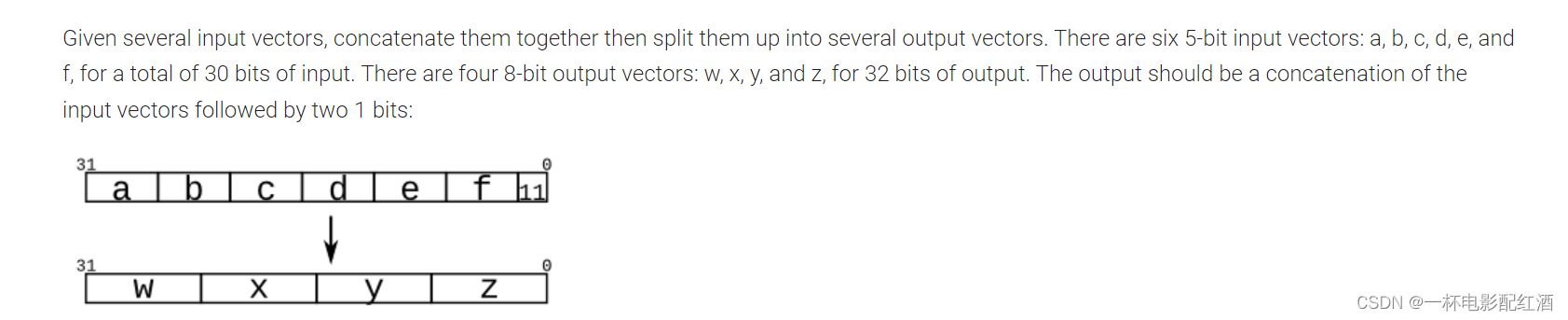

连接运算符( { } )concatenation operator

连接运算符是把位于大括号({})中的两个或两个以上信号或数值用逗号(,)分隔的小表达式按位连接在一起,最后用大括号括起来表示一个整体信号,形成一个大的表达式。

如:

题目5:

代码5:

Timing diagram5:

6169

6169

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?