编写一个序列检测模块,检测输入信号a是否满足011XXX110序列(长度为9位数据,前三位是011,后三位是110,中间三位不做要求),当信号满足该序列,给出指示信号match。

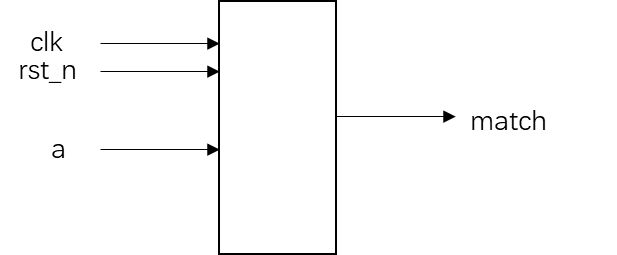

程序的接口信号图如下

代码如下:

(CSDN代码块不支持Verilog,代码复制到notepad++编辑器中,语言选择Verilog,看得更清楚)

`timescale 1ns/1ns

module sequence_detect(

input clk,

input rst_n,

input a,

output match

);

reg [8:0] a_tem;

reg match_f;

reg match_b;

always @(posedge clk or negedge rst_n)

if (!rst_n)

begin

match_f <= 1'b0;

end

else if (a_tem[8:6] == 3'b011)

begin

match_f <= 1'b1;

end

else

begin

match_f <= 1'b0;

end

always @(posedge clk or negedge rst_n)

if (!rst_n)

begin

match_b <= 1'b0;

end

else if (a_tem[2:0] == 3'b110)

begin

match_b <= 1'b1;

end

else

begin

match_b <= 1'b0;

end

always @(posedge clk or negedge rst_n)

if (!rst_n)

begin

a_tem <= 9'b0;

end

else

begin

a_tem <= {a_tem[7:0],a};

end

assign match = match_b && match_f;

endmodule

4557

4557

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?