描述

从A时钟域提取一个单时钟周期宽度脉冲,然后在新的时钟域B建立另一个单时钟宽度的脉冲。

A时钟域的频率是B时钟域的10倍;A时钟域脉冲之间的间隔很大,无需考虑脉冲间隔太小的问题。

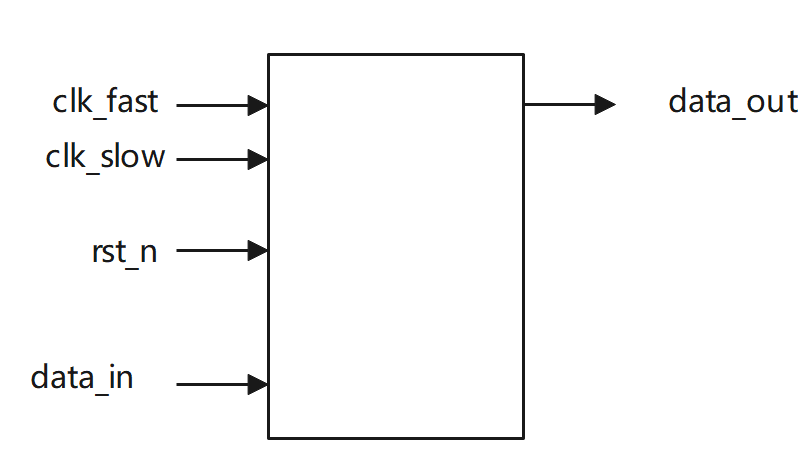

电路的接口如下图所示。data_in是脉冲输入信号,data_out是新的脉冲信号;clk_fast是A时钟域时钟信号,clk_slow是B时钟域时钟信号;rst_n是异步复位信号。

输入描述:

input clk_fast ,

input clk_slow ,

input rst_n ,

input data_in

输出描述:

output dataout

参考代码

`timescale 1ns/1ns

module pulse_detect(

input clk_fast ,

input clk_slow ,

input rst_n ,

input data_in ,

output dataout

);

reg data_fast,data_slow1,data_slow2,data_slow3;

always@(posedge clk_fast or negedge rst_n)begin

if(!rst_n)

data_fast <= 'd0;

else

data_fast <= data_in ? ~data_fast : data_fast;

end

always@(posedge clk_slow or negedge rst_n)

begin

if(!rst_n)begin

data_slow1<='d0;

data_slow2<='d0;

data_slow3<='d0;

end

else begin

data_slow1<=data_fast;

data_slow2<=data_slow1;

data_slow3<=data_slow2;

end

end

assign dataout = data_slow2^ data_slow3;

endmodule

272

272

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?