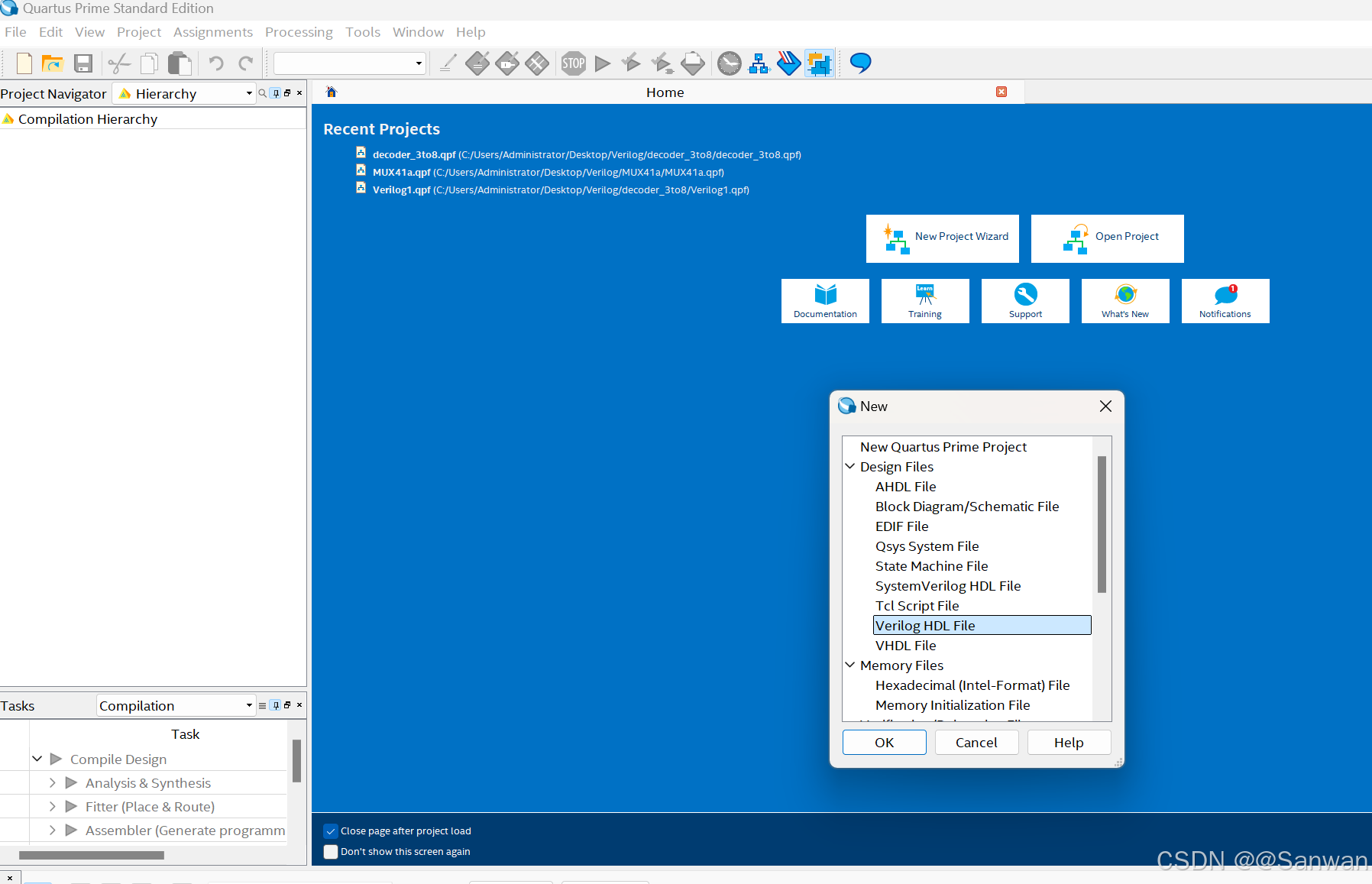

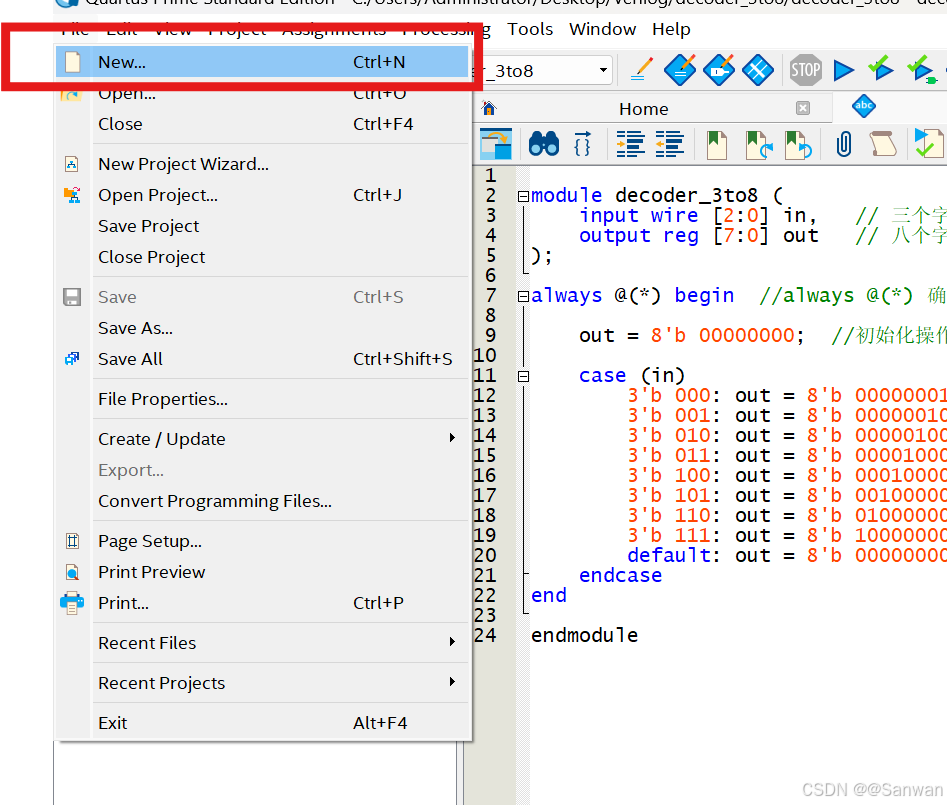

1. 进入软件页面,新建工程。点击File->New->Verilog HDL File

Verilog语言如下

module decoder_3to8 (

input wire [2:0] in, // 三个字节的输入

output reg [7:0] out // 八个字节的输出

);

always @(*) begin //always @(*) 确保每当 in 的值发生变化时,out 会立即根据 case 语句重新计算

out = 8'b 00000000; //初始化操作

case (in)

3'b 000: out = 8'b 00000001;

3'b 001: out = 8'b 00000010;

3'b 010: out = 8'b 00000100;

3'b 011: out = 8'b 00001000;

3'b 100: out = 8'b 00010000;

3'b 101: out = 8'b 00100000;

3'b 110: out = 8'b 01000000;

3'b 111: out = 8'b 10000000;

default: out = 8'b 00000000;

endcase

end

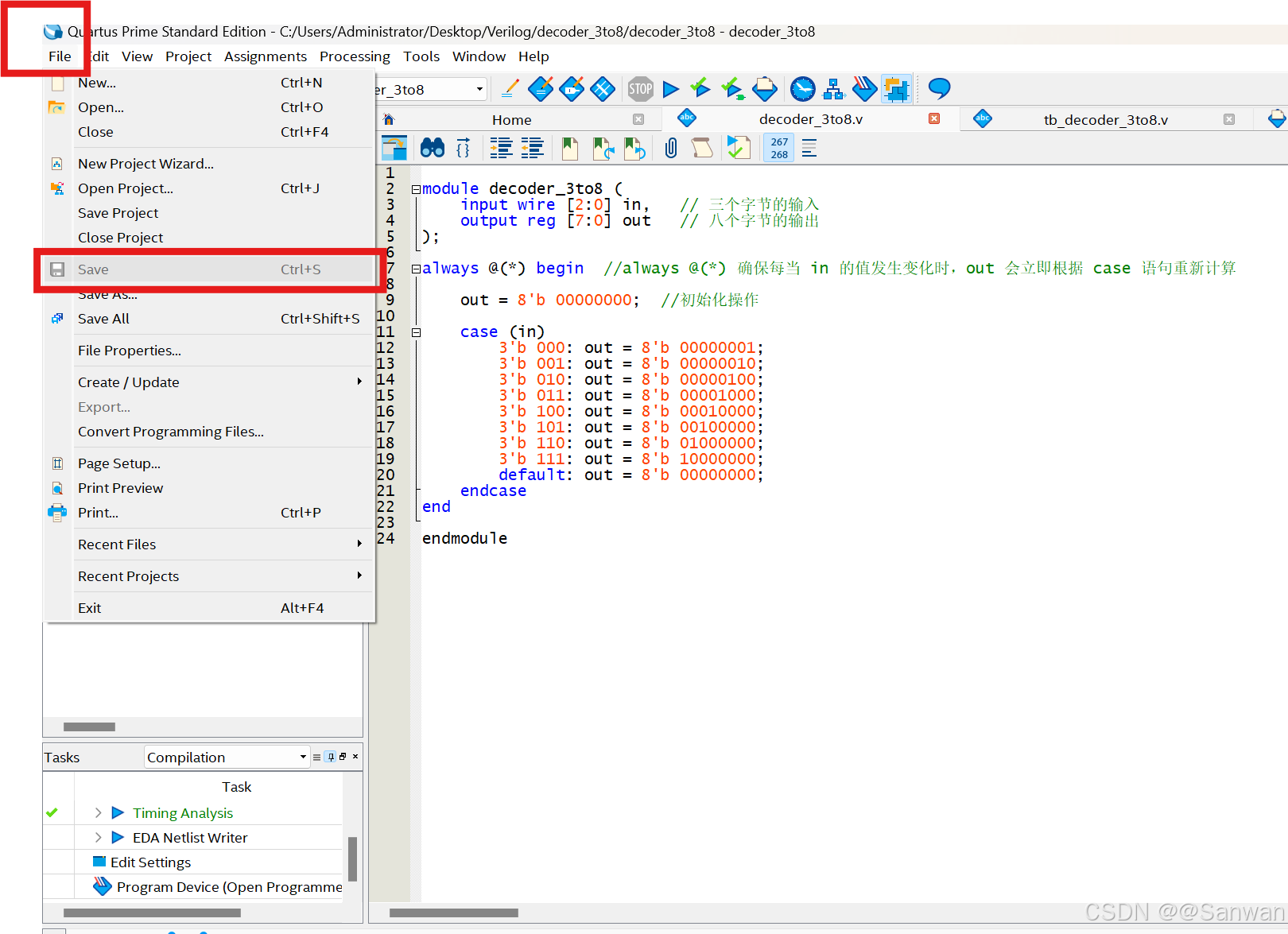

endmodule2.对代码进行保存和运行

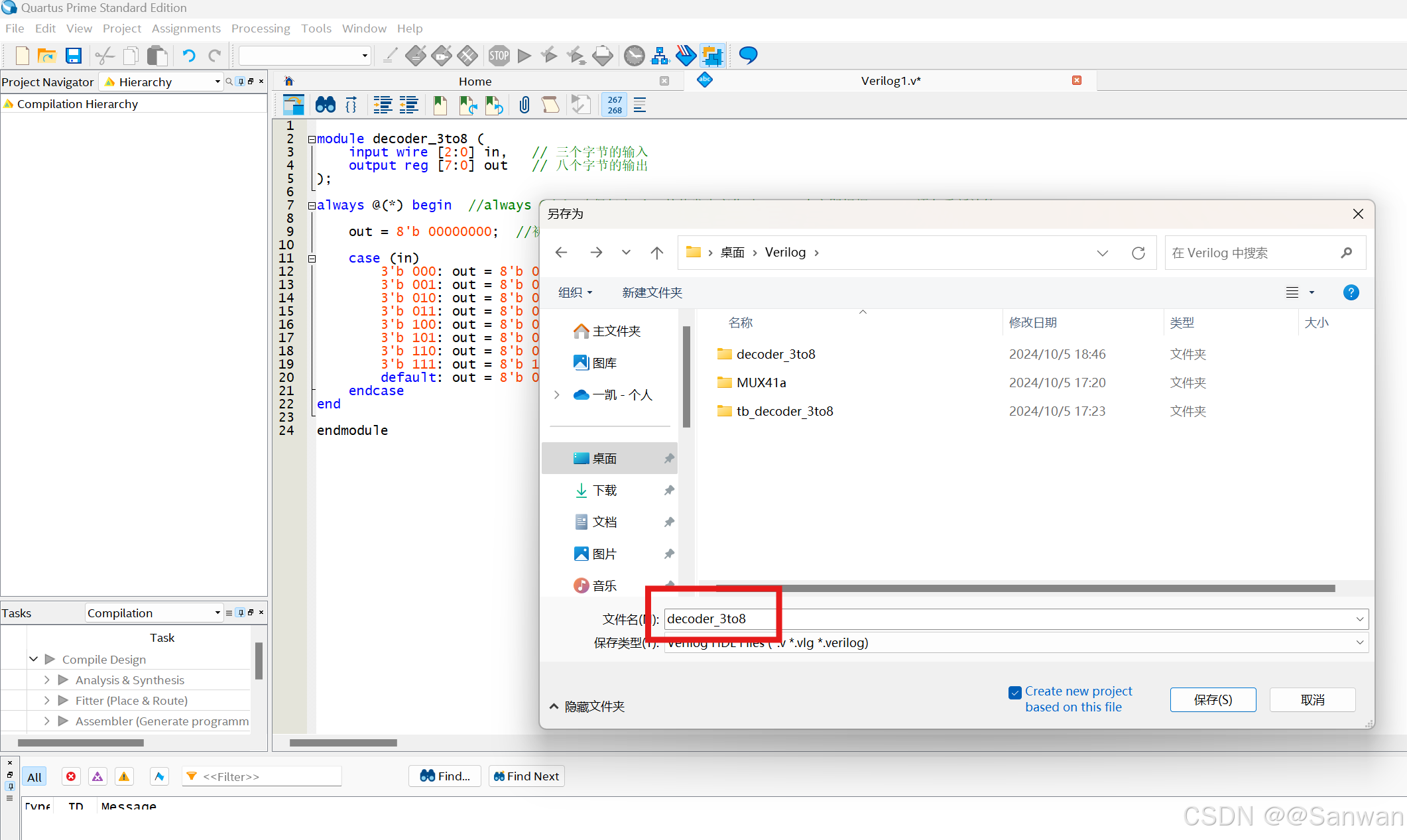

一定要把文件名改为decoder_3to8 不然后面运行不成功

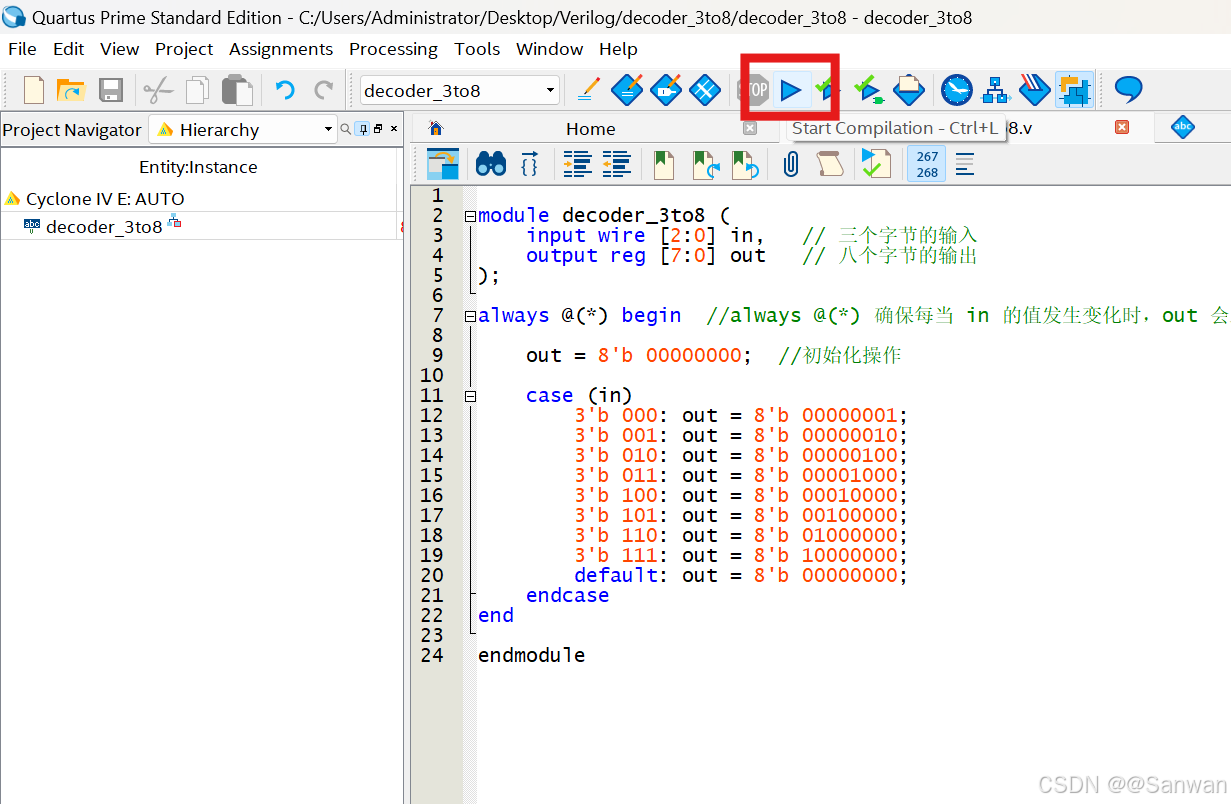

保存完毕后进行运行(start compliation)

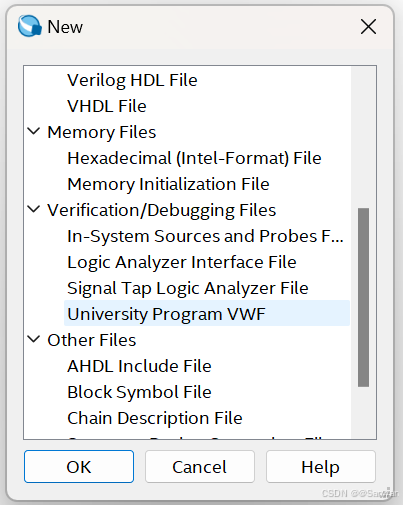

3.运行结束后建立University Program VWF,如图

选择University Program VWF

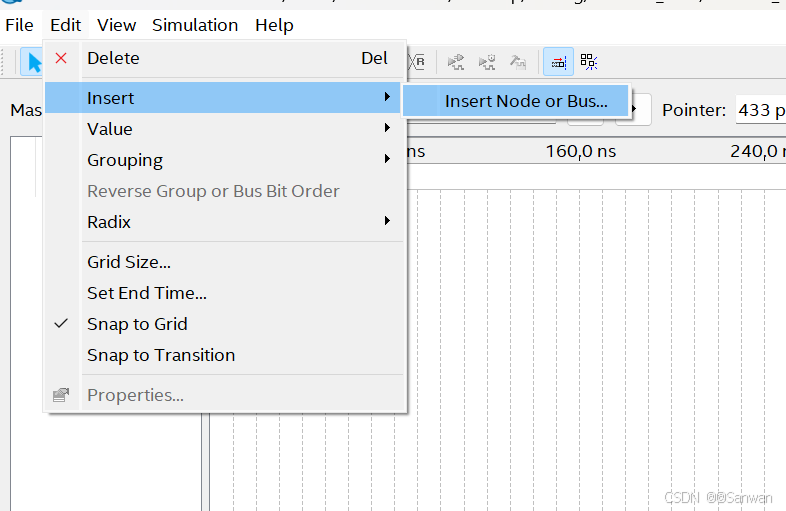

4.之后在新界面点击Edit -> Insert -> Insert Node or Bus

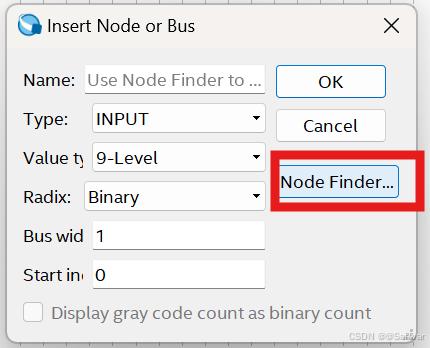

点击 Node Finder

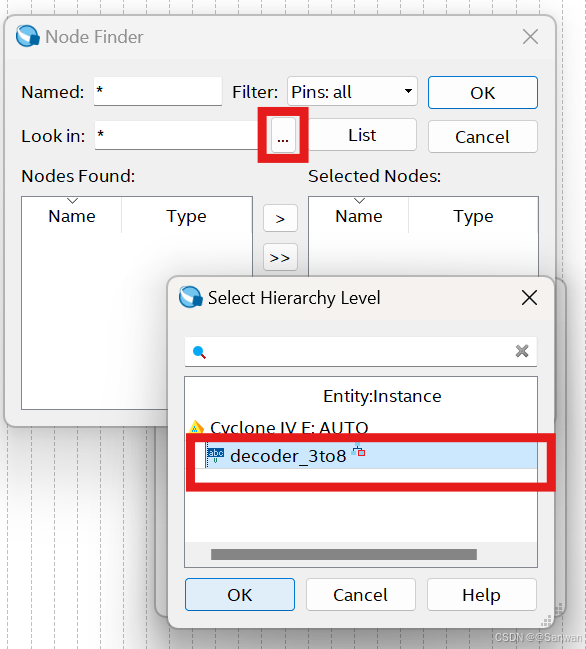

之后按照下图所示点击... 再点击创建的工程decoder_3to8

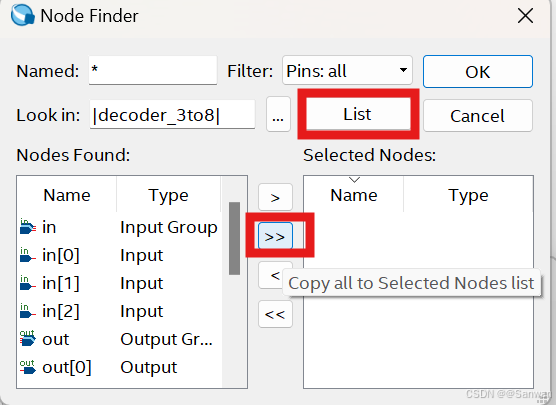

点击List 再点击 >>将所有输入输出移到Selecter Nodes,连续退出界面点击 两次 OK,不点OK创建不成功。

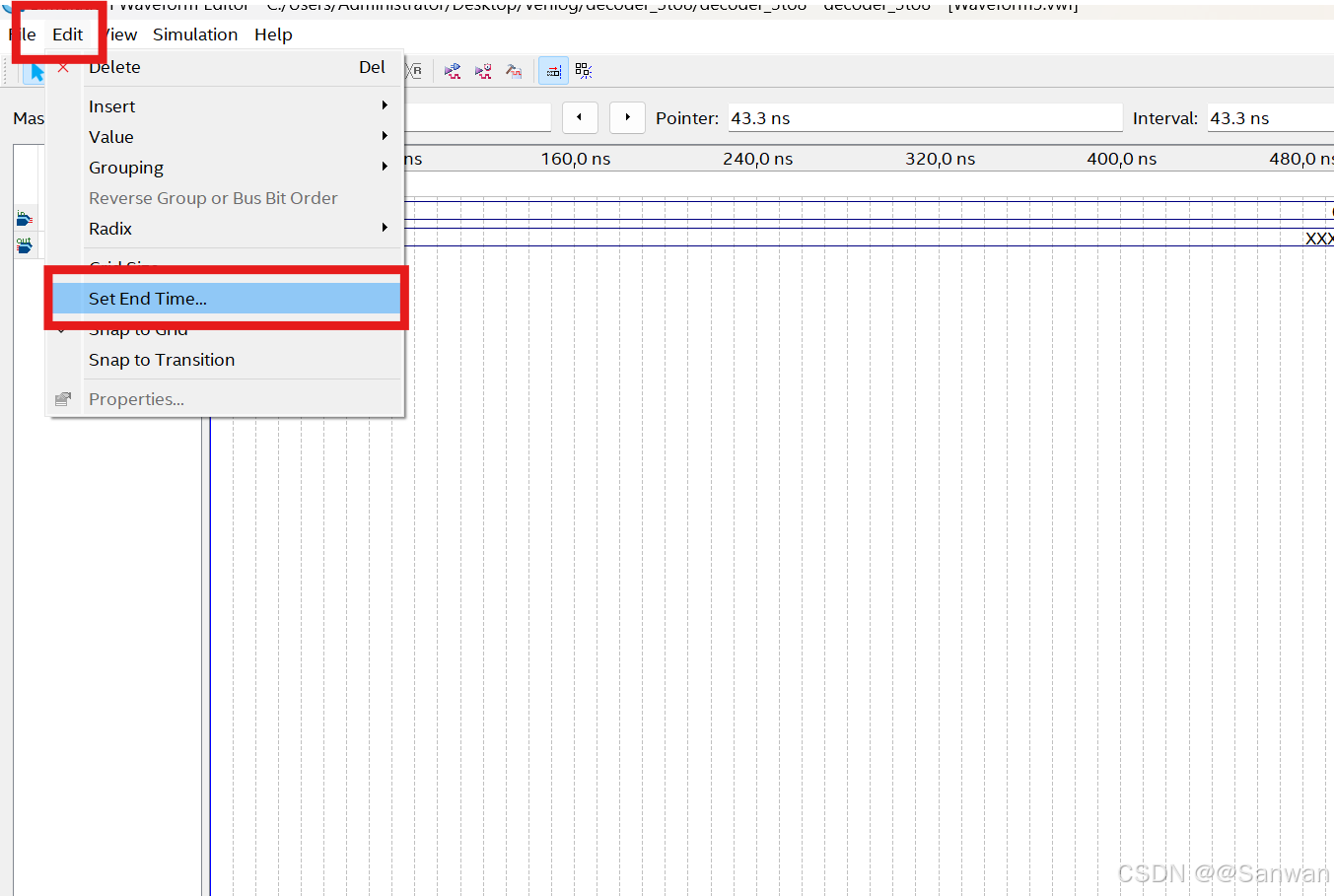

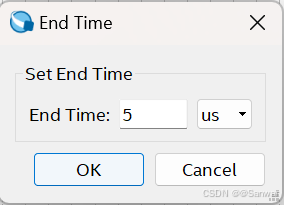

5.调整参数

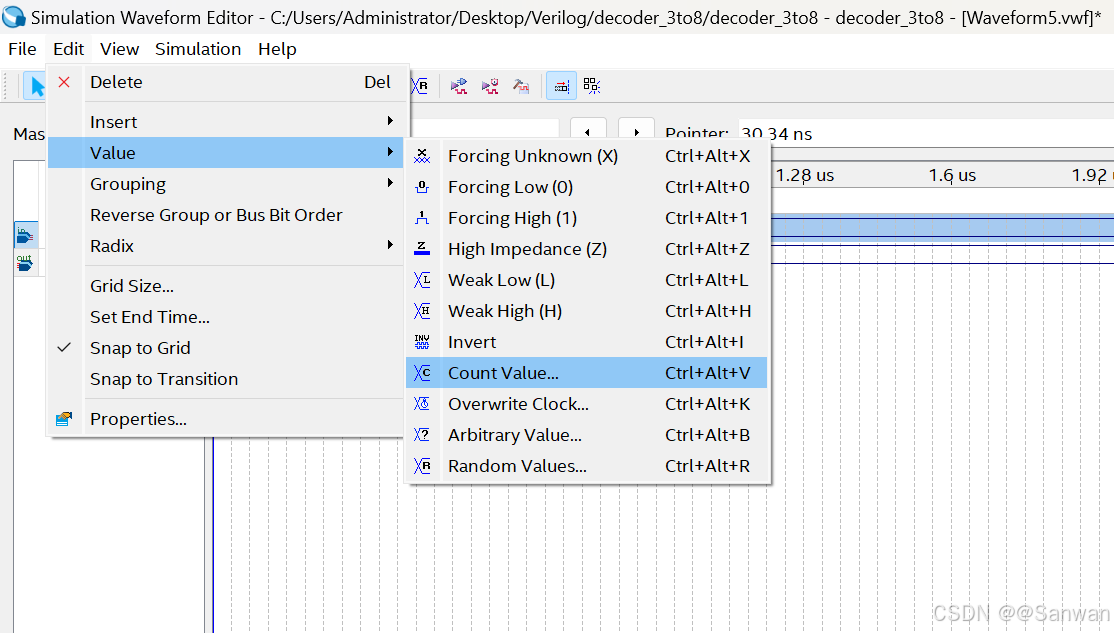

先点击输入量in,再点击Edit->Value->Count Value

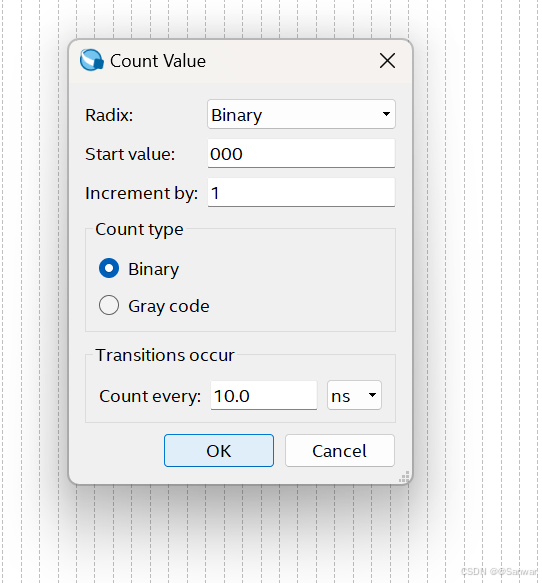

参数设置如下点击OK

6.进行仿真

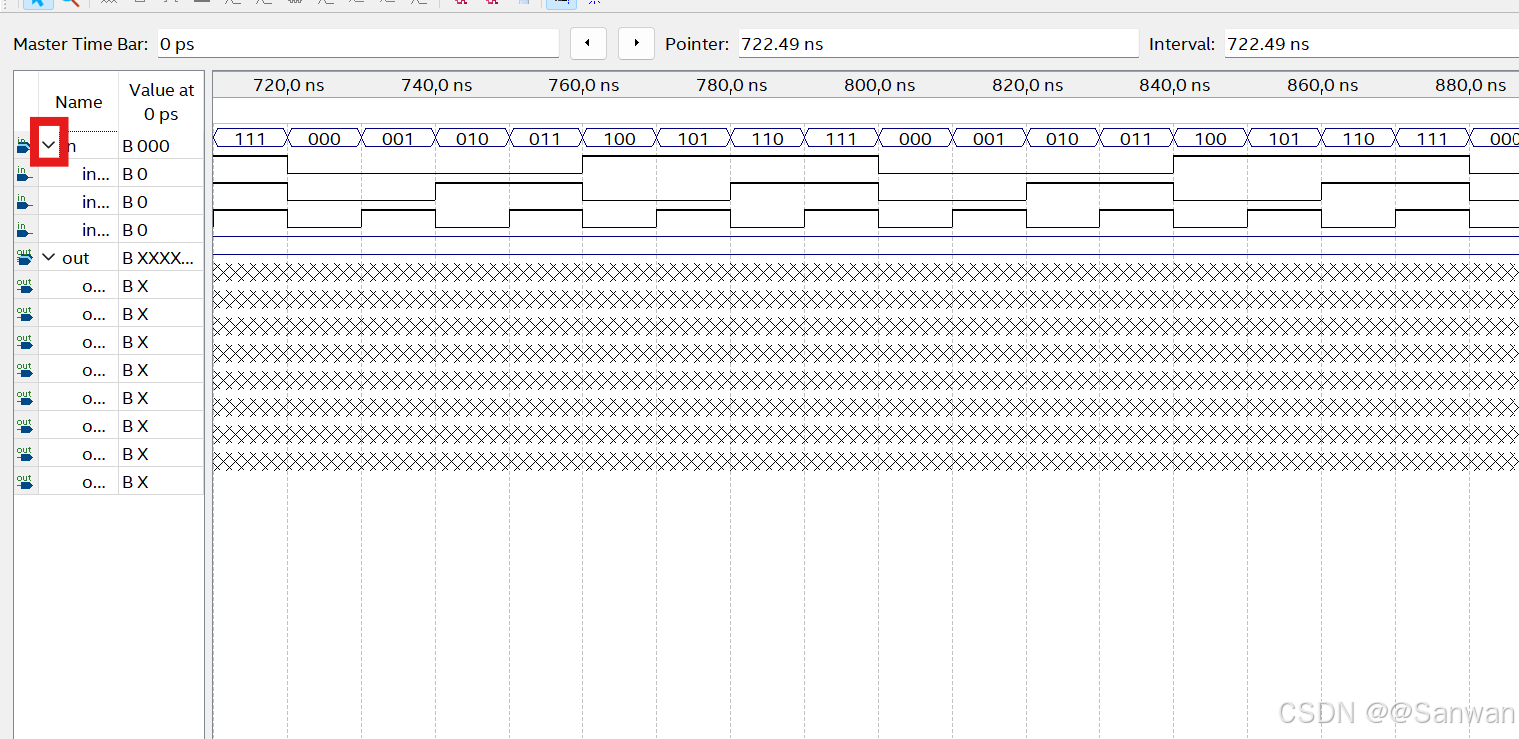

点击箭头可以展开输入量In 如下图所示

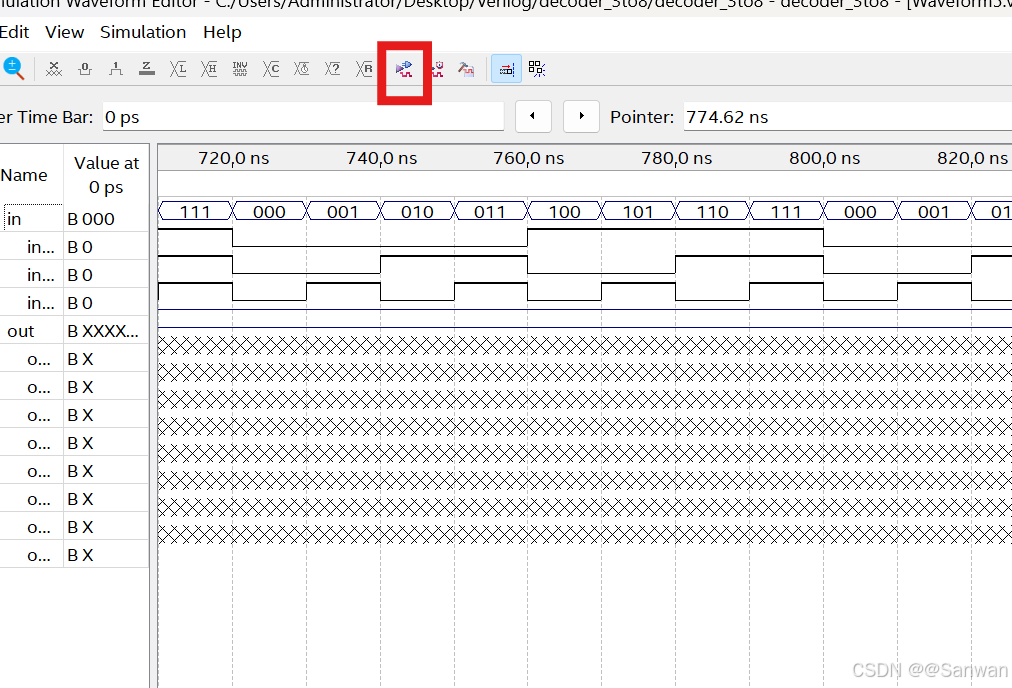

之后点击Run Functional Simulation -> Yes ->保存

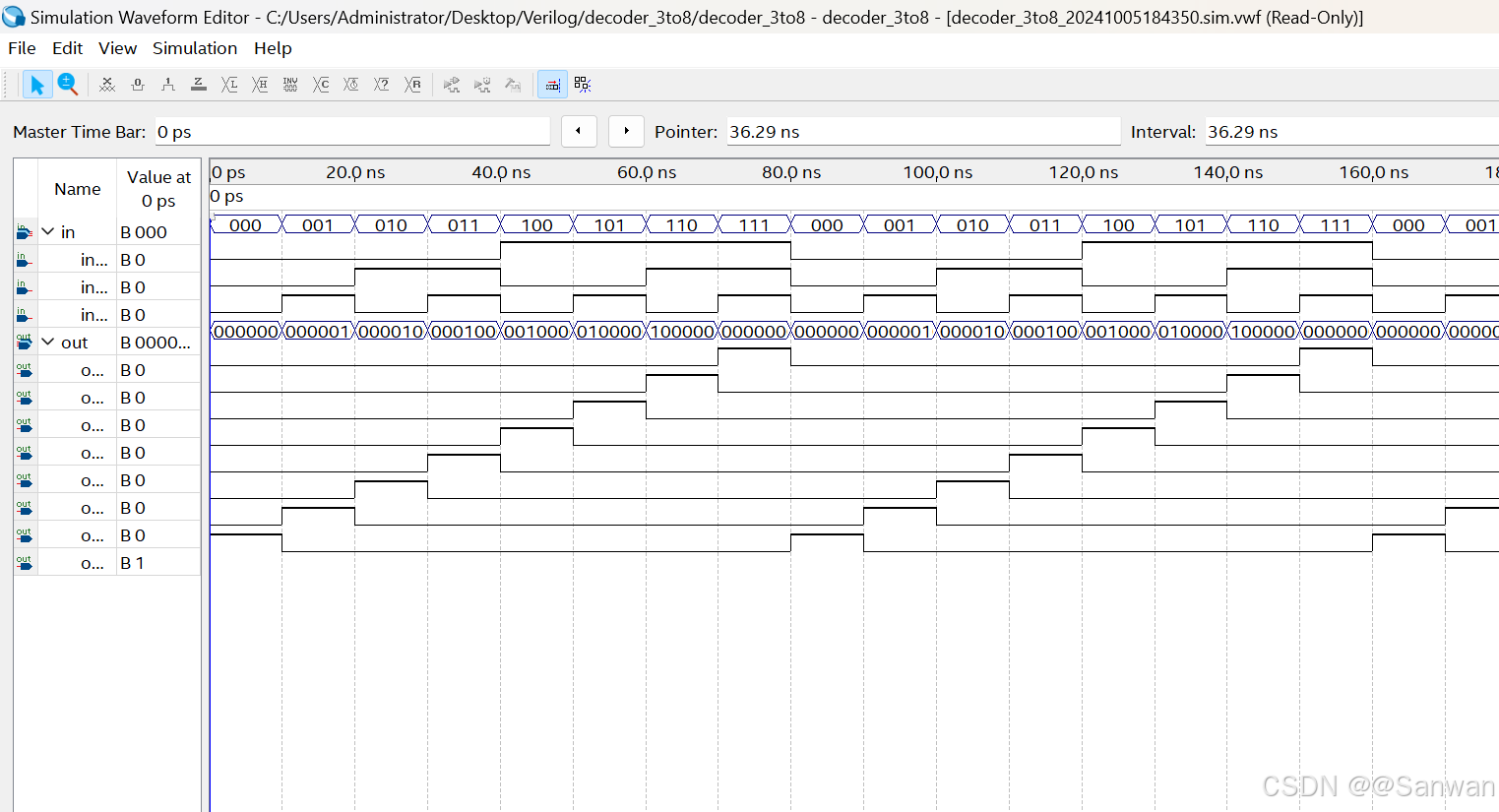

仿真结果如下,ctrl+滑动滚轮可以缩放页面大小查看波形。

用University Program VWF实现三-八译码器verilog语言的仿真结束

5135

5135

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?