目录

1.安装配置Quartus和ModelSim软件后,进行以下操作。

1)首先使用Logsim绘制一个3-8译码器电路图,列出3-8译码器的逻辑真值表。然后采用Verilog编程(if-else或者case)设计一个3-8译码器,生成RTL原理电路图。

2)编写一个仿真测试文件,对3-8译码器进行仿真测试,输出测试波形图。

1)Verilog 综合生成的3-8译码器电路原理图与原始设计电路存在什么差异? 仿真测试生成的结果是否与真值表一致?

2) Verilog代码设计的3-8译码器模块的输出信号 为何要定义为 reg类型而不用默认wire(导线)类型?改成wire型是否可以?

2.在logsim中完成 “1位全加器”和“4位全加器”逻辑门电路

1)用Verilog的门级描述方式写一个“1位全加器”, 生成RTL电路,与Logsim的“1位全加器”进行对比。

2)采用Verilog模块调用子模块的方式,用4个上面的“1位全加器”级联方式,构成一个“4位全加器”(即串行全加器),生成RTL电路,与Logsim的“4位全加器”电路进行对比.

3)采用Verilog的行为级方式重新完成上面的1)和2)。

基础练习A

1.安装配置Quartus和ModelSim软件后,进行以下操作。

1)首先使用Logsim绘制一个3-8译码器电路图,列出3-8译码器的逻辑真值表。然后采用Verilog编程(if-else或者case)设计一个3-8译码器,生成RTL原理电路图。

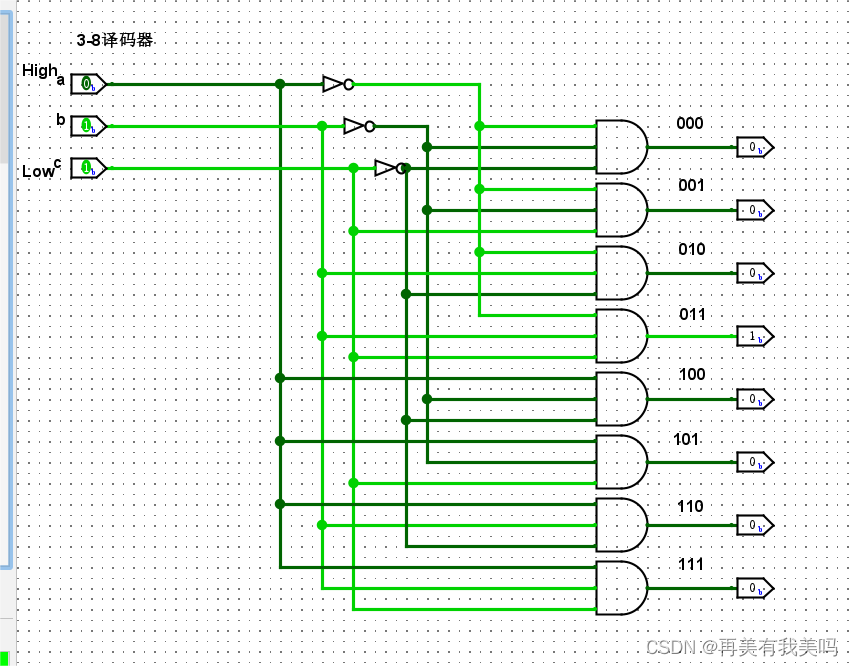

使用Logsim绘制一个3-8译码器电路图:

列出3-8译码器的逻辑真值表:

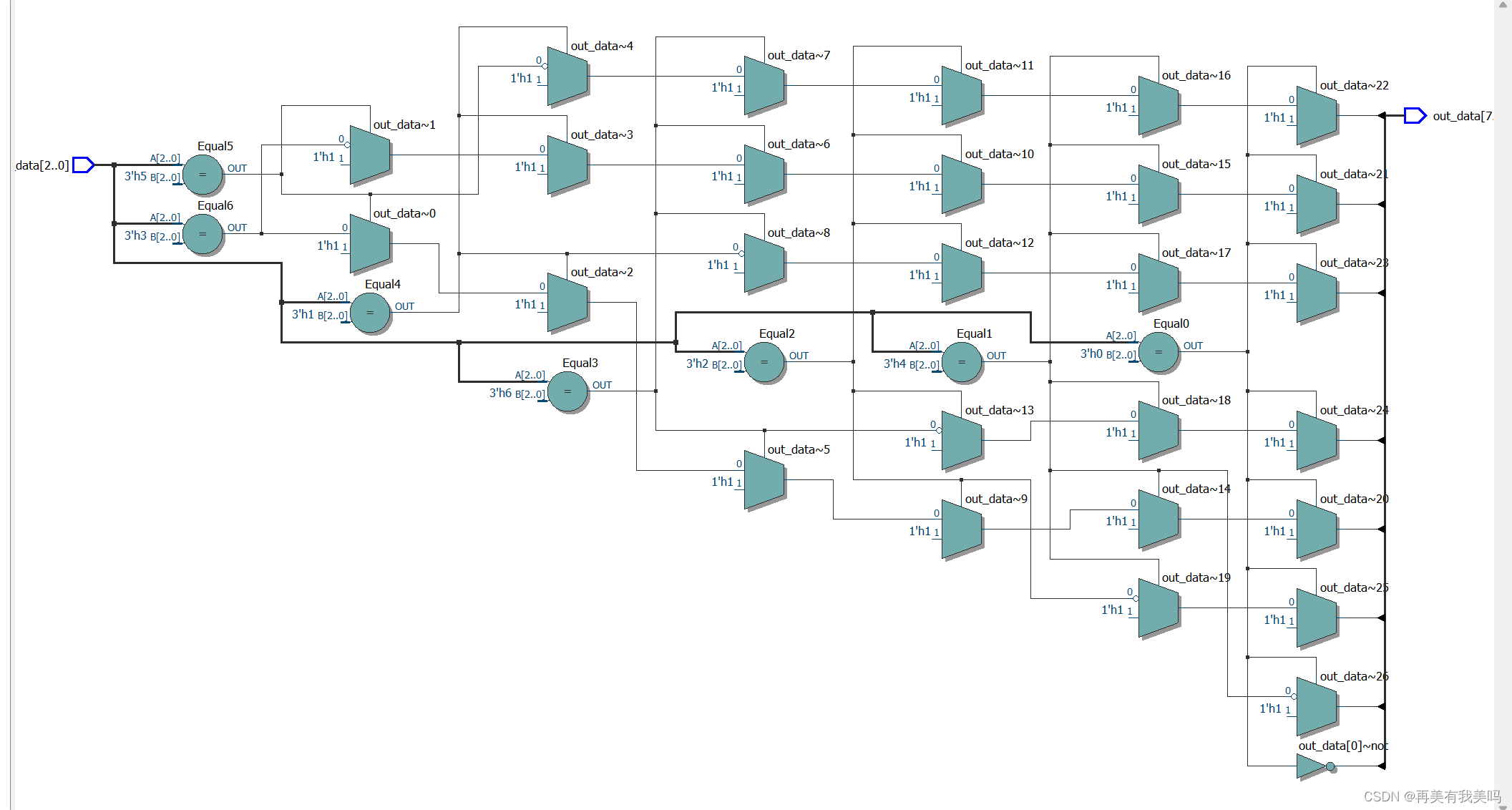

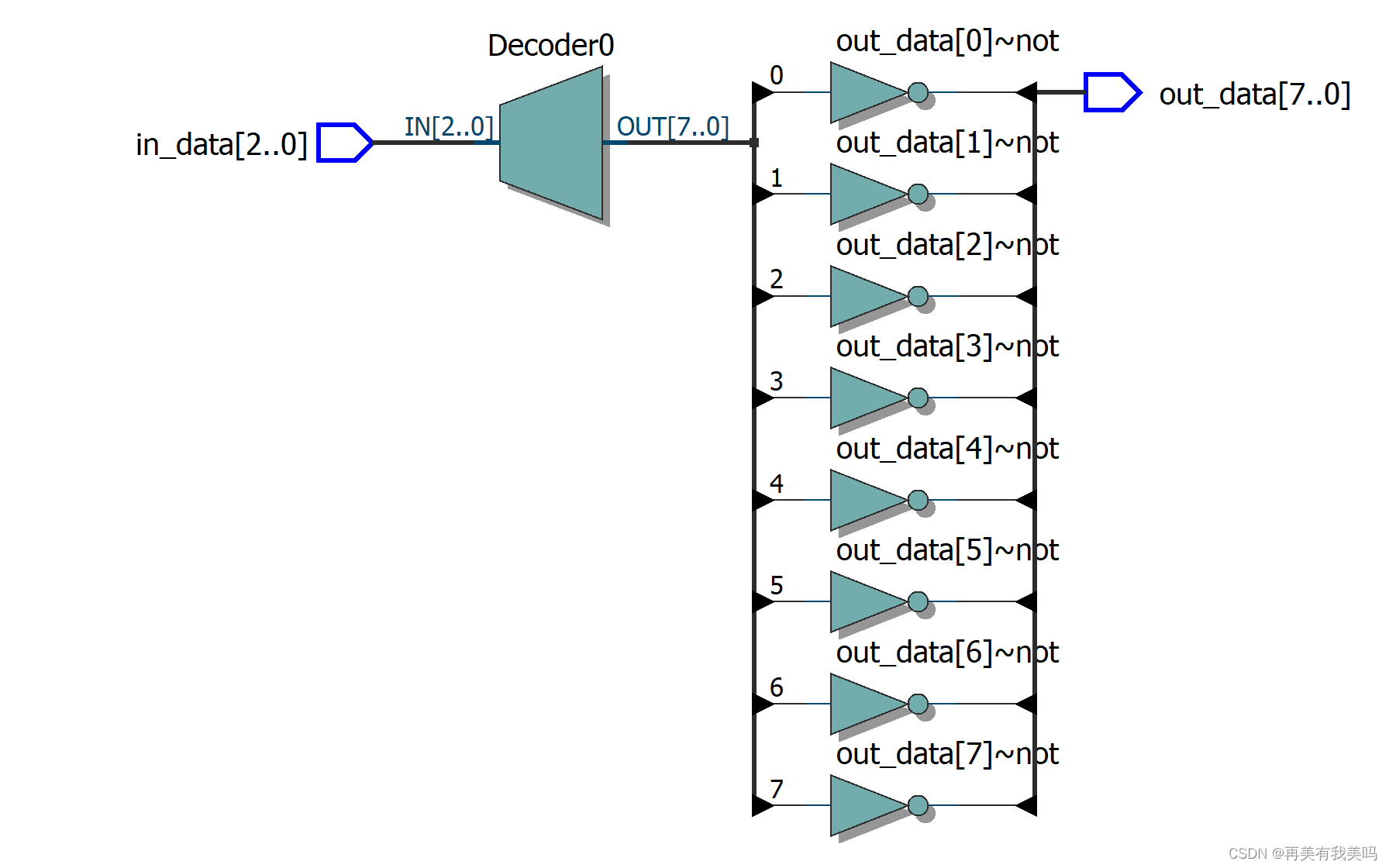

采用Verilog编程(if-else或者case)设计一个3-8译码器,生成RTL原理电路图:

if-else代码,RTL原理电路图:

module if_38 (in_data,out_data);

input wire [2:0] in_data;

output reg [7:0] out_data;

always @(*)

begin

if (in_data==3'b000) out_data<=8'b1111_1110;

else if (in_data==3'b001) out_data<=8'b1111_1101;

else if (in_data==3'b010) out_data<=8'b1111_1011;

else if (in_data==3'b011) out_data<=8'b1111_0111;

else if (in_data==3'b100) out_data<=8'b1110_1111;

else if (in_data==3'b101) out_data<=8'b1101_1111;

else if (in_data==3'b110) out_data<=8'b1011_1111;

else out_data<=8'b0111_1111;

end

endmodule

case代码,RTL原理电路图:

module case_38( in_data, out_data);

input wire [2:0] in_data;

output reg [7:0] out_data;

always @(in_data)

begin

case(in_data)

3'b000: out_data<=8'b1111_1110;

3'b001: out_data<=8'b1111_1101;

3'b010: out_data<=8'b1111_1011;

3'b011: out_data<=8'b1111_0111;

3'b100: out_data<=8'b1110_1111;

3'b101: out_data<=8'b1101_1111;

3'b110: out_data<=8'b1011_1111;

3'b111: out_data<=8'b0111_1111;

default:out_data<=8'b1111_1111;

endcase

end

endmodule

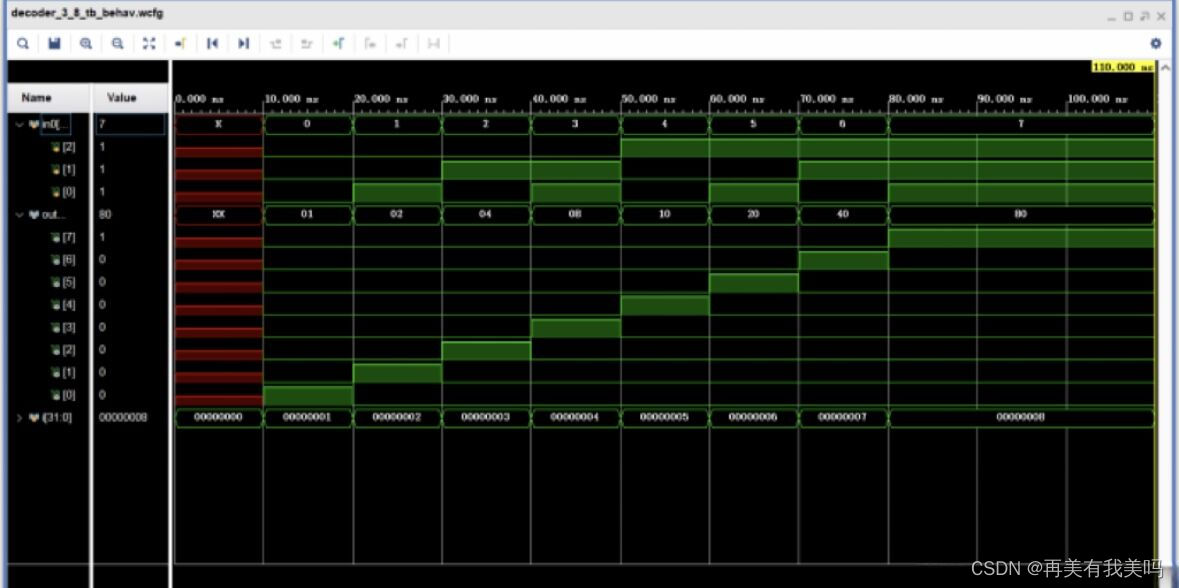

2)编写一个仿真测试文件,对3-8译码器进行仿真测试,输出测试波形图。

测试代码:

`timescale 1ns / 1ps

module decoder_3_8_tb();

reg [2:0]in0;

wire [7:0]out0;

decode_3_8 decoder_3_80(.in(in0),.out(out0));

integer i=0;

initial begin

for(i=0;i<=7;i=i+1)begin

# 10

in0=i;

end

# 30

$finish;

end

endmodule

波形图:

2.分析并回答下列问题:

1)Verilog 综合生成的3-8译码器电路原理图与原始设计电路存在什么差异? 仿真测试生成的结果是否与真值表一致?

答:Verilog 综合生成的3-8译码器电路原理图与logisim设计电路存在一定差异。这是因为Verilog综合生成的电路是由逻辑门和触发器等基本元件组成的,而logisim设计电路则是由逻辑门和连线等基本元件组成的。因此,两者的内部结构和实现方式存在一定的差异。但是,无论是Verilog综合生成的电路还是logisim设计电路,它们的功能都是一样的,都可以将3位二进制数译码为8位输出信号;经检验,仿真测试生成的结果与真值表相一致。

2) Verilog代码设计的3-8译码器模块的输出信号 为何要定义为 reg类型而不用默认wire(导线)类型?改成wire型是否可以?

答:在Verilog代码设计的3-8译码器模块中,输出信号需要定义为reg类型而不是默认的wire类型。这是因为reg类型可以存储值,而wire类型只能传递值。在3-8译码器中,输出信号需要存储一个值,以便将其传递到下一个模块中。因此,需要使用reg类型来存储输出信号的值。如果将输出信号定义为wire类型,则无法存储值,因此无法传递到下一个模块中。

如果将输出信号定义为wire类型,会导致编译错误。因为在3-8译码器中,输出信号需要存储一个值,而wire类型无法存储值,因此无法满足这个要求。因此,必须使用reg类型来定义输出信号。

基础练习B

2.在logsim中完成 “1位全加器”和“4位全加器”逻辑门电路

1)用Verilog的门级描述方式写一个“1位全加器”, 生成RTL电路,与Logsim的“1位全加器”进行对比。

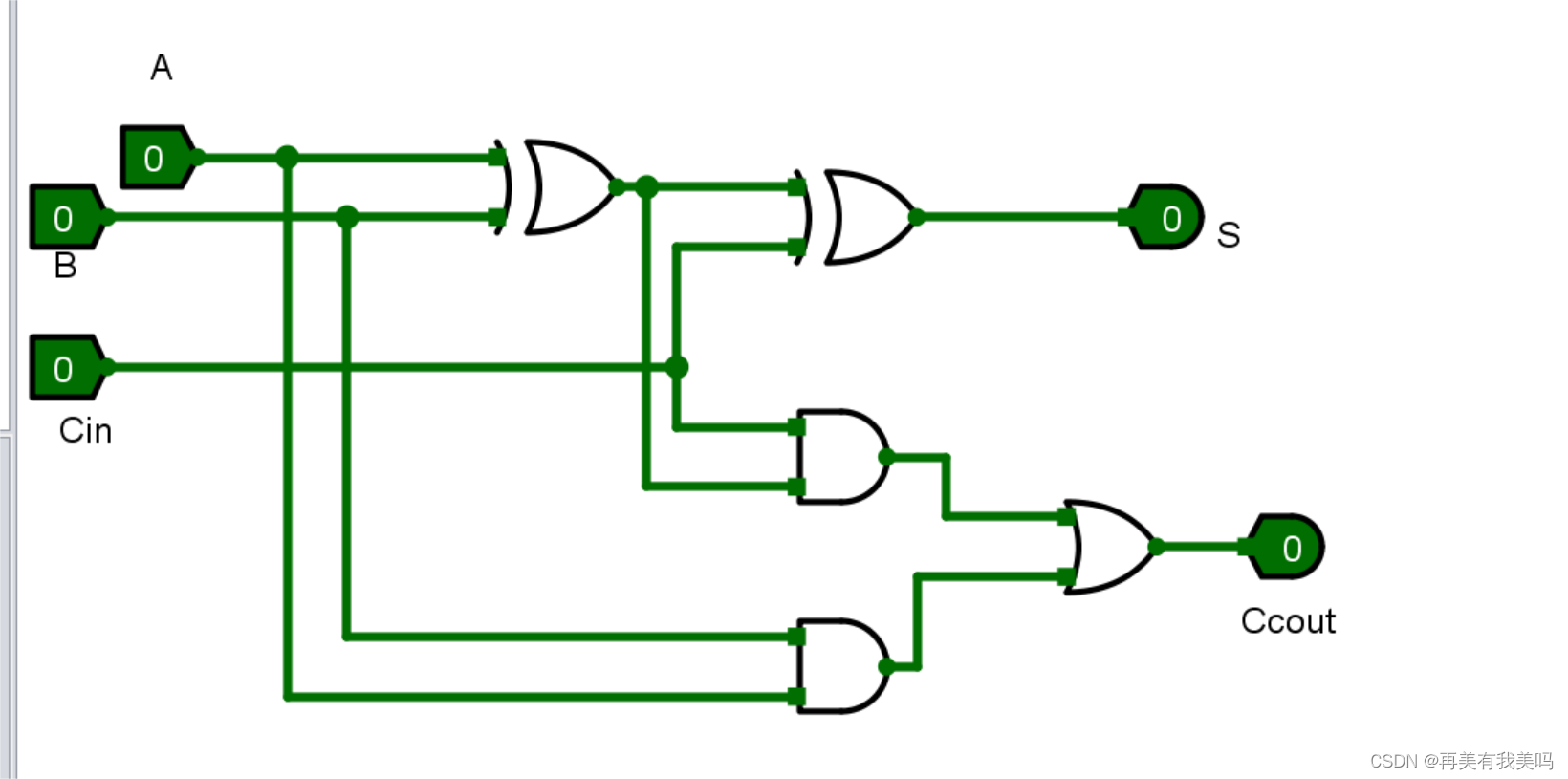

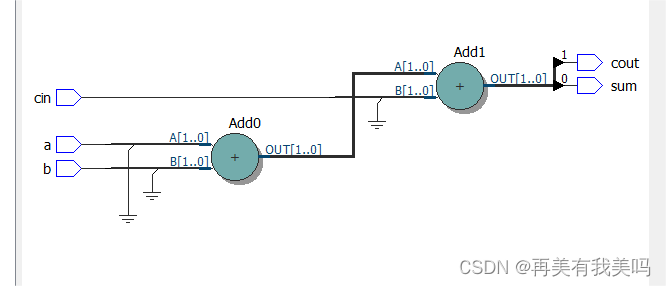

Logsim的“1位全加器”:

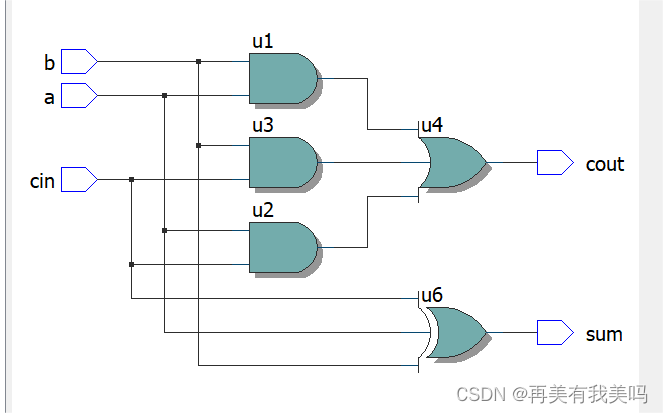

Verilog的门级描述方式写一个“1位全加器”:

module adder_structural(a,b,cin,sum,cout);

input a,b,cin;

output sum,cout;

wire t1,t2,t3,t4;

and u1(t1,a,b);

and u2(t2,a,cin);

and u3(t3,b,cin);

or u4(cout,t1,t2,t3);

xor u5(t4,a,b);

xor u6(sum,t4,cin);

endmodule

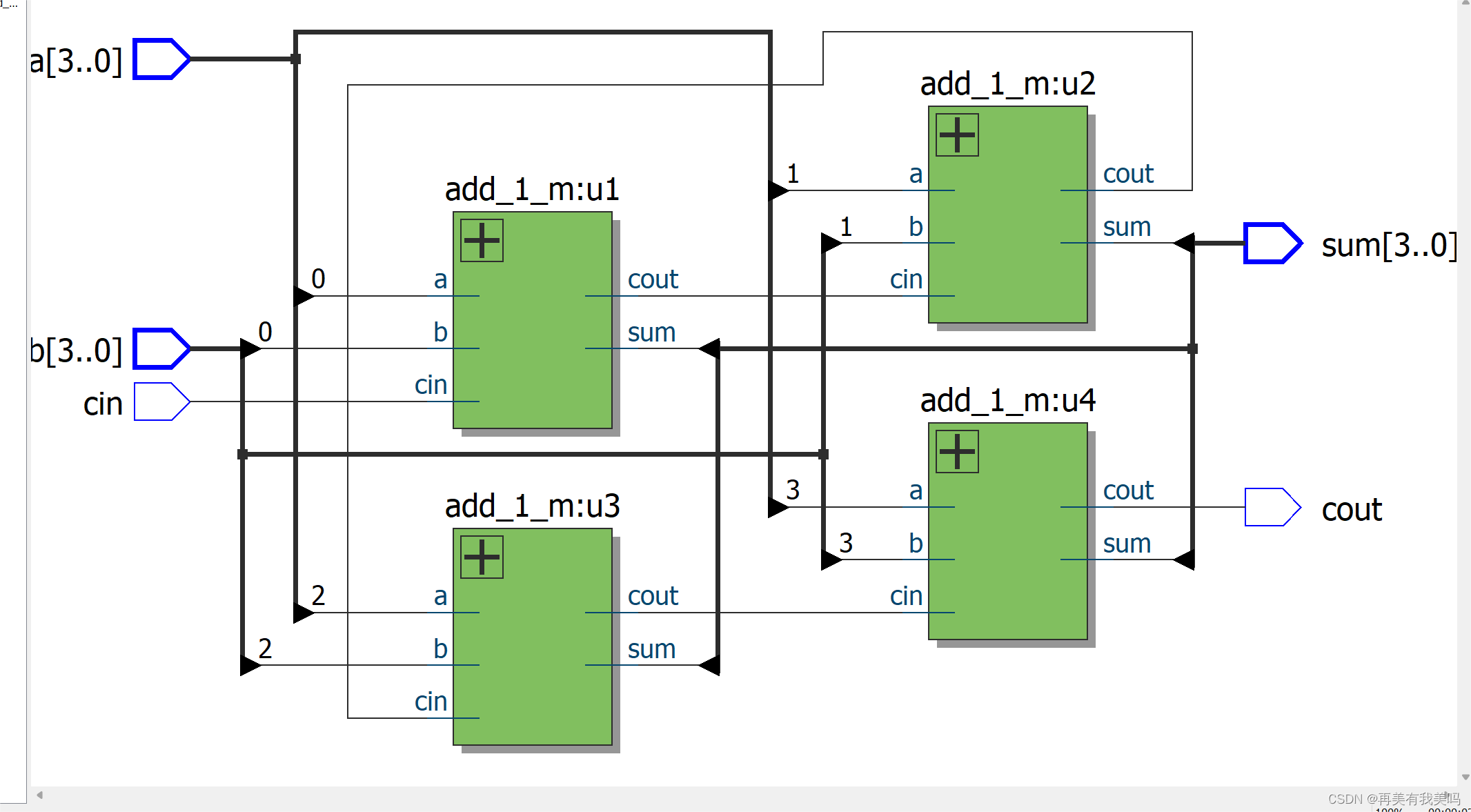

2)采用Verilog模块调用子模块的方式,用4个上面的“1位全加器”级联方式,构成一个“4位全加器”(即串行全加器),生成RTL电路,与Logsim的“4位全加器”电路进行对比.

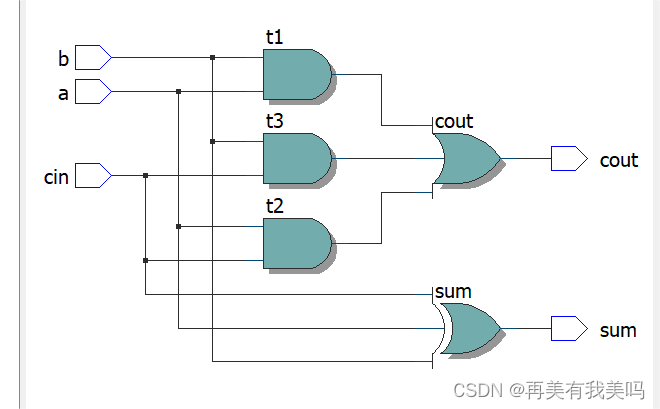

使用Verilog生成RTL电路:

module add_1_m (a,b,cin,cout,sum);

input a,b;

input cin;

output cout;

output sum;

wire [2:0] w;

and

a1(w[0],a,cin),

a2(w[1],a,b),

a3(w[2],b,cin);

xor a4(sum,a,b,cin);

or a5(cout,w[0],w[1],w[2]);

endmodule

//use add_1_m connect to add_4

module add_4_m (a,b,cin,cout,sum);

input [3:0] a,b;

input cin;

output cout;

output [3:0] sum;

wire [3:1] c;

add_1_m u1 (a[0],b[0],cin,c[1],sum[0]);

add_1_m u2 (a[1],b[1],c[1],c[2],sum[1]);

add_1_m u3 (a[2],b[2],c[2],c[3],sum[2]);

add_1_m u4 (a[3],b[3],c[3],cout,sum[3]);

endmodule

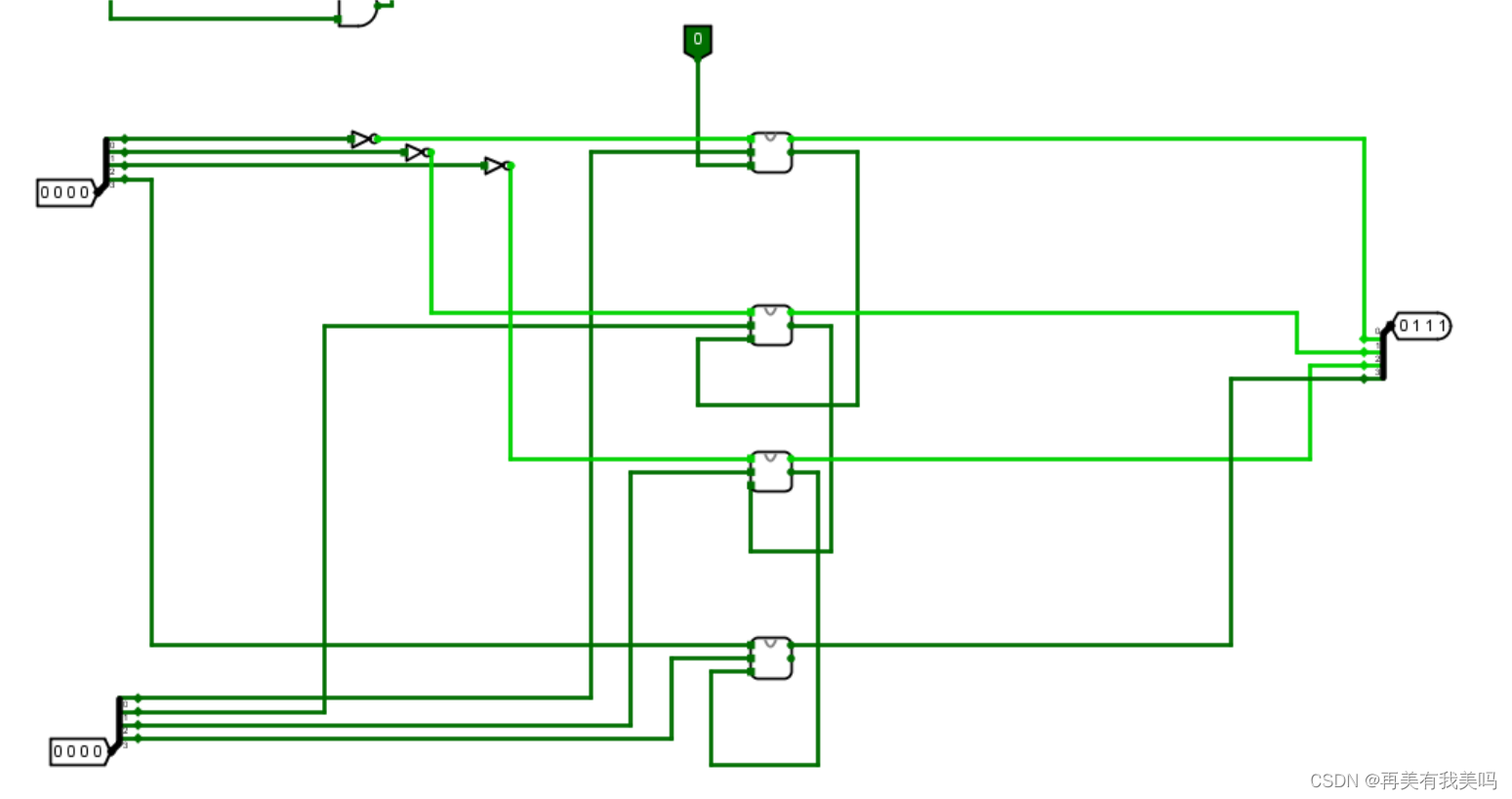

Logsim的“4位全加器”电路:

3)采用Verilog的行为级方式重新完成上面的1)和2)。

1)1bit全加器:

module adder_dataflow1(a,b,cin,sum,cout);

input a,b,cin;

output sum,cout;

wire t1,t2,t3;

assign sum=a^b^cin;

assign t1=a&b;

assign t2=a&cin;

assign t3=b&cin;

assign cout=t1|t2|t3;

endmodule

2)4bit全加器:

module adder1 (

input A, B, Cin,

output Sum, Cout

);

assign {Cout, Sum} = A + B + Cin;

endmodule

module adder4

(

input [3:0]A,B,

input cin,

output [3:0]sum,

output cout

);

wire[4:0]c;

assign c[0] = cin;

adder1 adder10(A[0],B[0],c[0],sum[0],c[1]);

adder1 adder11(A[1],B[1],c[1],sum[1],c[2]);

adder1 adder12(A[2],B[2],c[2],sum[2],c[3]);

adder1 adder13(A[3],B[3],c[3],sum[3],c[4]);

assign cout = c[4];

endmodule

4)采用Verilog设计一个8位全加器模块。

module adder_dataflow2(input a,b,cin,output sum,cout);

assign {cout,sum}=a+b+cin;

endmodule

1054

1054

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?