一、RS触发器实验

(一)RS触发器的定义

RS触发器是用一对交叉耦合的或非门或者与非门构成的储存元件,可以存储一位数据(0或者1)。其中,S是置位(set)输入端,R是复位(reset)输入端。输出值Q是触发器的状态值。

(二)RS触发器的图示、模拟电路图及其分析

1、RS触发器的结构

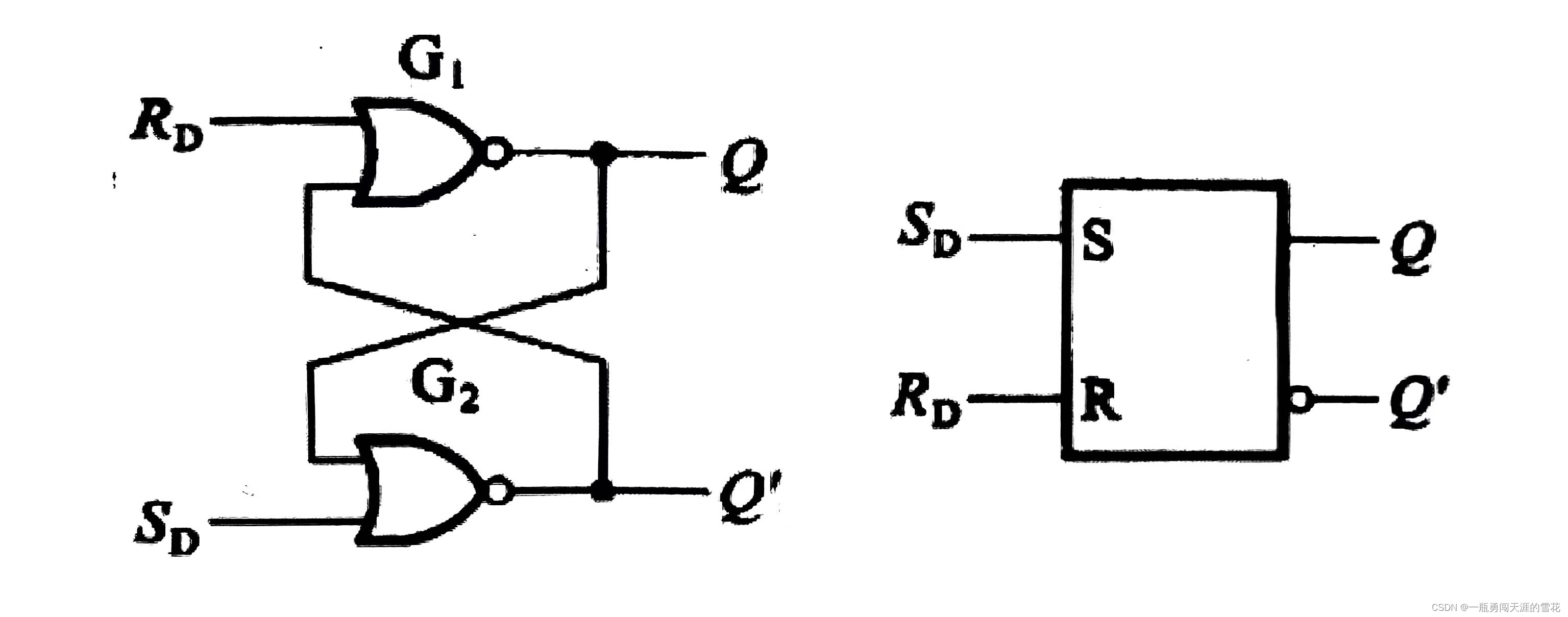

或非门组成的RS触发器

图1.电路结构 图2.图形符号

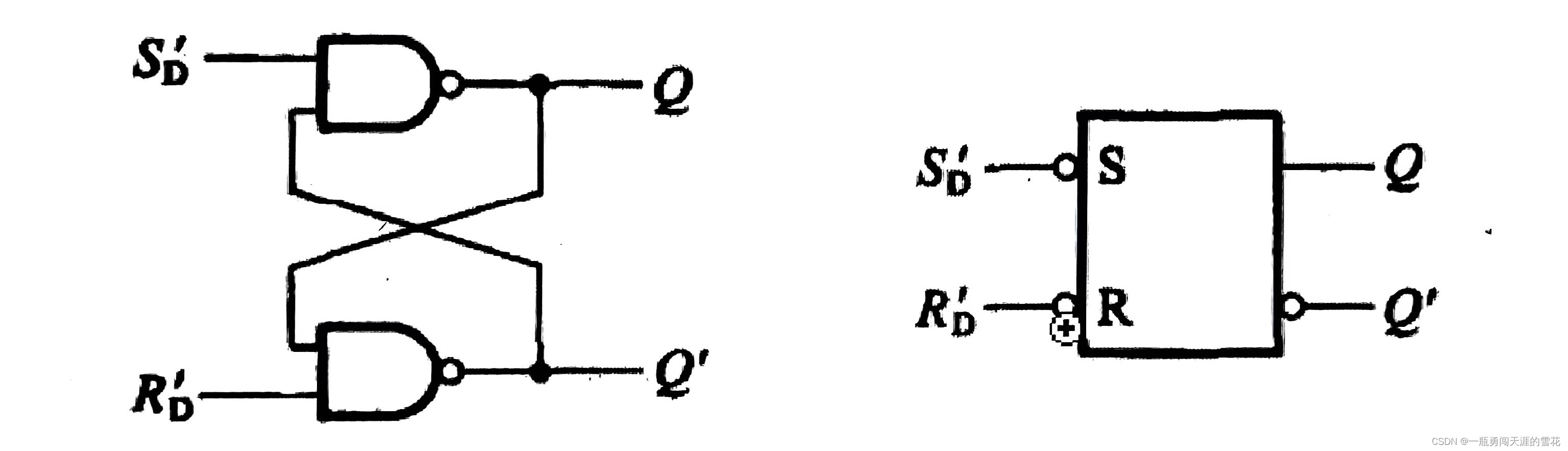

与非门组成的RS触发器

图3.电路结构 图4.图形符号

2、RS触发器在logisim中的模拟电路及其真值表

将两个输入端(S置位输入端和R复位端)按如下图所示连接在芯片的引脚位置

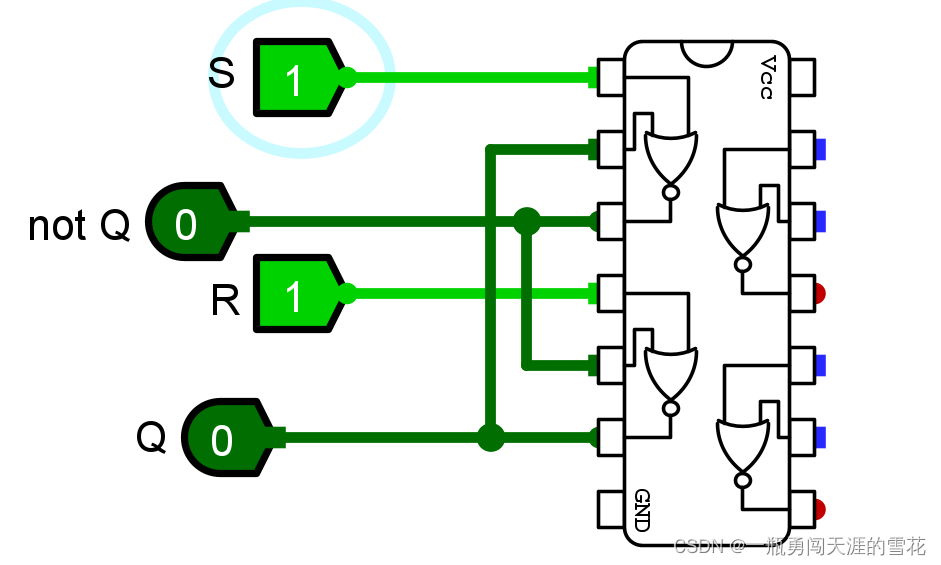

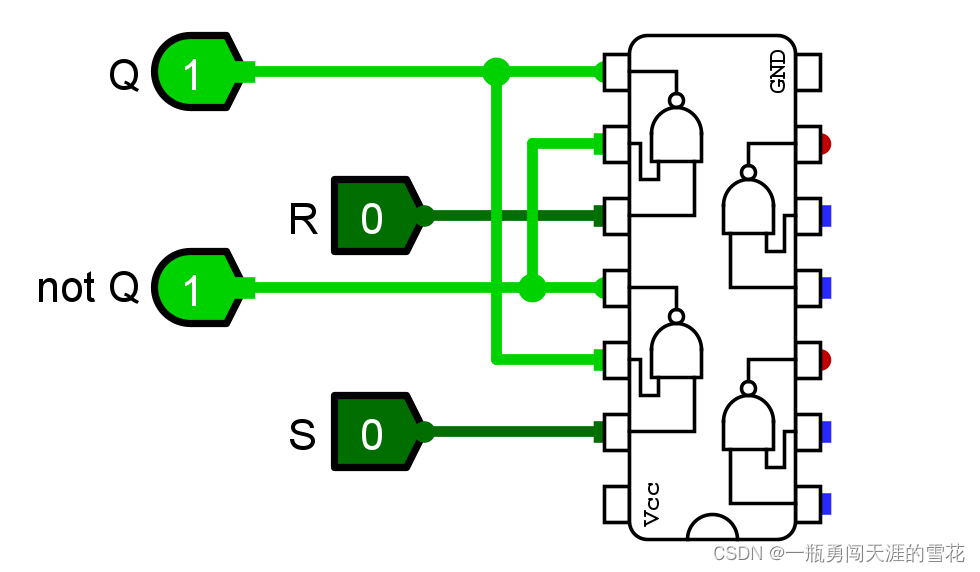

(1)或非门组成的RS触发器

我们在搭建模拟电路的过程中,利用芯片74LS02中的或非门IC来充当锁存器中的或非门,并按照RS触发器(或非门)的组成结构图连接电路:

图5.模拟电路图

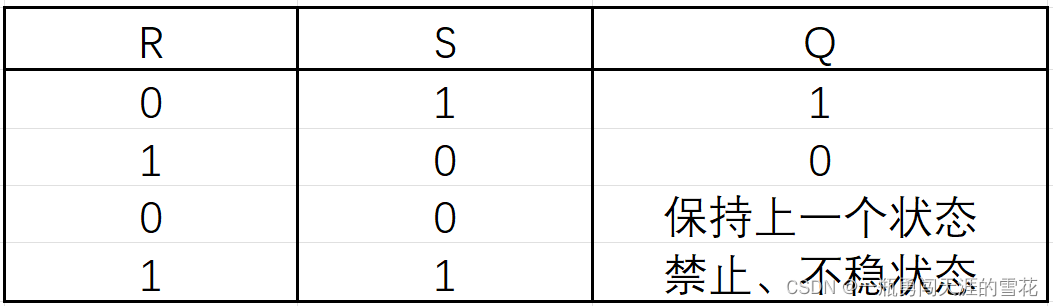

图6.RS触发器特征表

在上面的“RS触发器特征表”中:0表示低电平,1表示高电平。

对于或非门组成的触发器,存在以下规律:

- 当S=0,R=0时,电路能稳定保持原先的状态。

- 当S=1,R=0时,输出端Q为1,而输出端not Q为0,从而保持稳定的输出。

- 当S=0,R=1时,即有且仅当R输入为1时,即此前的稳定状态被复位,输出端Q变为0,而not Q输出为1.

- 当S=1,R=1时,这种情况是禁止、不稳定的状态。即当S=1,R=1时Q=not Q=0,此情况是禁止的。

(2)与非门组成的RS触发器

我们在搭建模拟电路的过程中,利用芯片74LS00中的与非门来充当锁存器中的与非门,并按照RS触发器(与非门)的组成结构图连接电路:

图7.模拟电路图

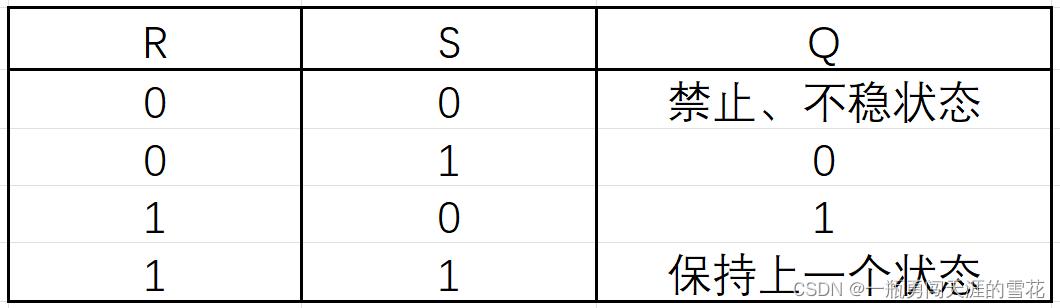

图8.RS触发器特征表

在上面的“RS触发器特征表”中:0表示低电平,1表示高电平。

对于与非门组成的触发器,存在以下规律:

- 当S=0,R=0时,这种情况是禁止、不稳定的状态。即当S=1,R=1时Q=not Q=0此情况是禁止的。

- 当S=0,R=1时,输出端Q为1,而输出端not Q为0,从而保持稳定的输出。

- 当S=1,R=0时,即有且仅当S输入为1时,即此前的稳定状态被复位,输出端Q变为0,而not Q输出为1。

- 当S=1,R=1时,电路能稳定保持原先的状态。

3.RS触发器总结:

与非门组成的触发器:

(1)不论是什么状态,

在R端施加低电平能将现在的状态强制转换到“0”态;

在S端施加低电平能将现在的状态强制转换到“1”态;

R与S输入端不能同时为低电平。

(2)R和S输入端的有效电平为低电平。

或非门组成的触发器:

(1)不论是什么状态,

在R端施加高电平能将现在的状态强制转化到“0”态。

在S端施加高电平能将现在的状态强制转化到“1”态。

R与S输入端不能同时为高电平。

(2)R和S输入端的有效电平为高电平。

二、D触发器实验

(一)D锁存器的定义

D锁存器是一种数字电路元件,用于存储和处理数据。它由一个数据输入端(D)和控制输入端(通常是时钟信号)构成。D锁存器有两个稳态:SET和RESET。

(二)D锁存器的图示、模拟电路图及其分析

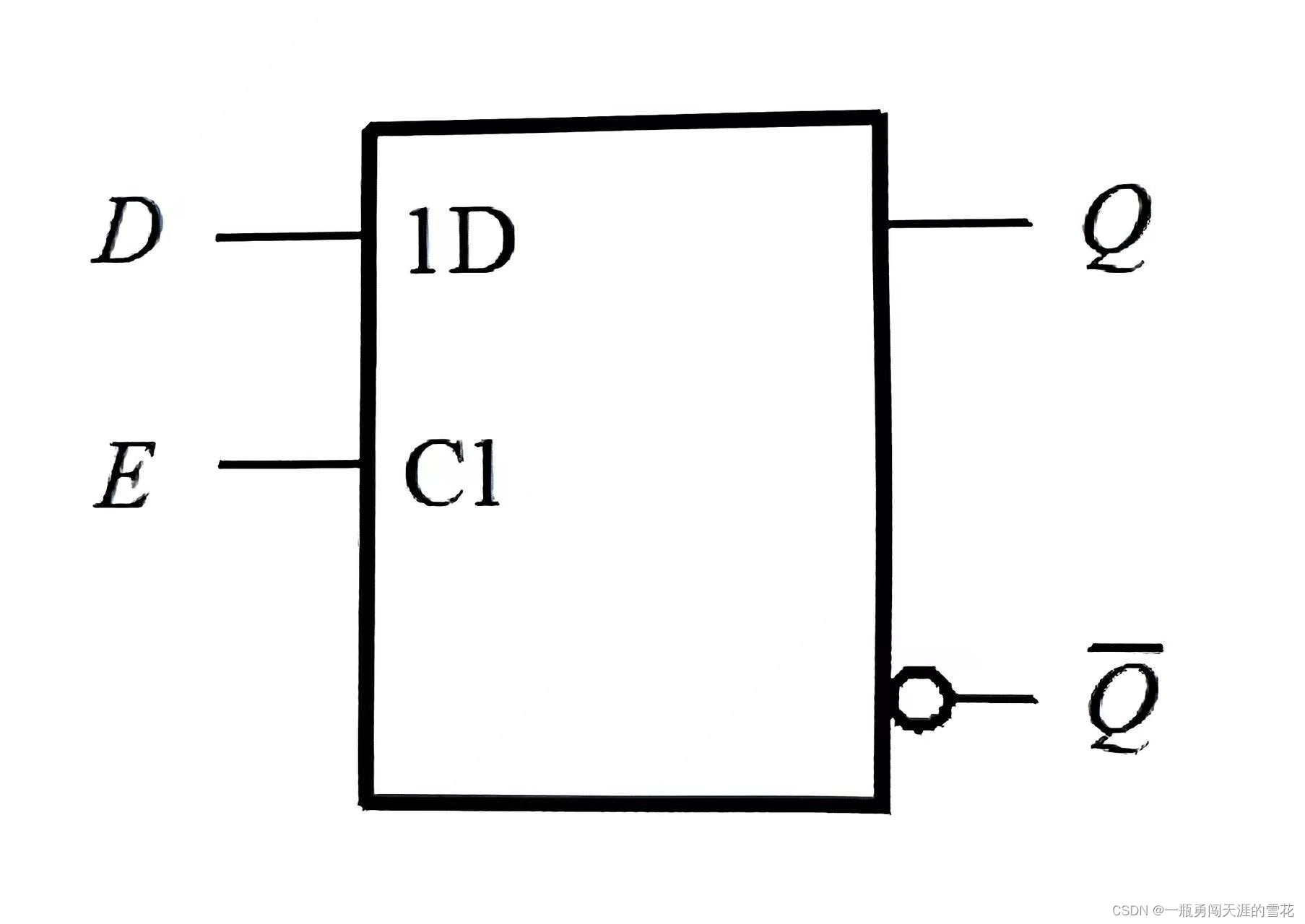

1.D锁存器的结构

图9.电路结构 图10.图形符号

2、D锁存器在logisim中的模拟电路及其特征表

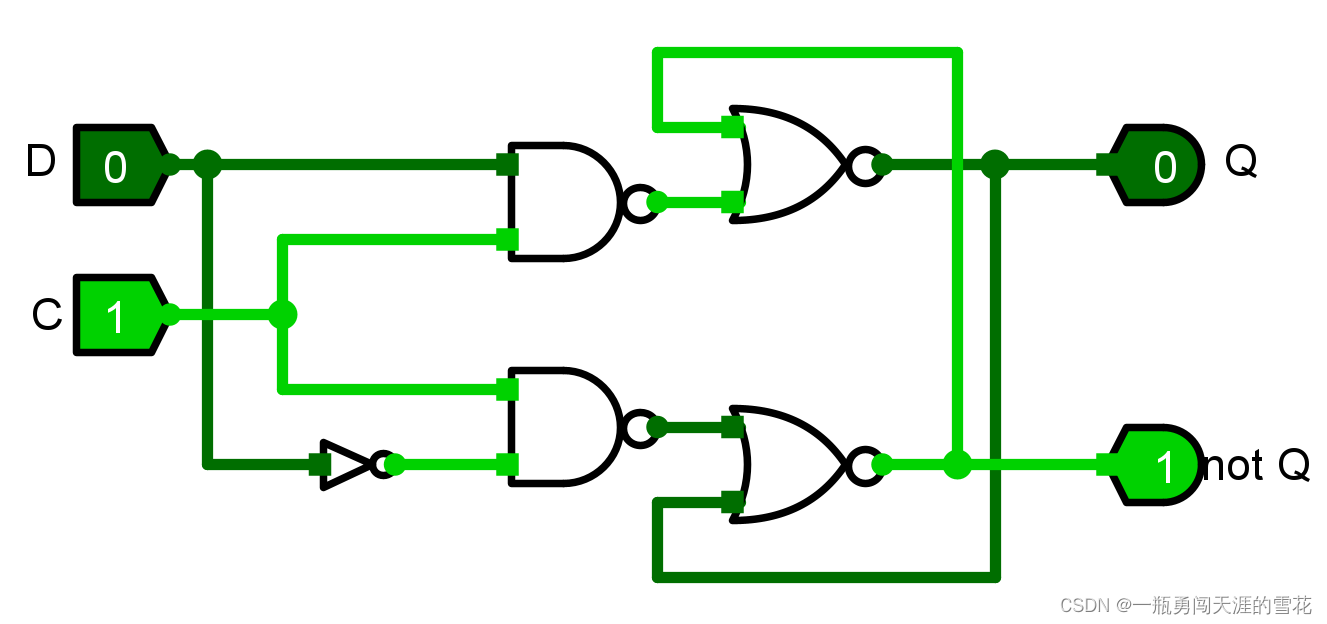

学习过程中了解到D锁存器是由使能信号控制门电路与简单的RS触发器组成的。按此连接成下图的模拟电路:

图11.模拟电路图

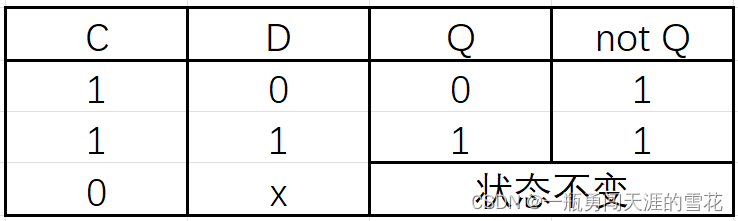

图12.D锁存器特征表

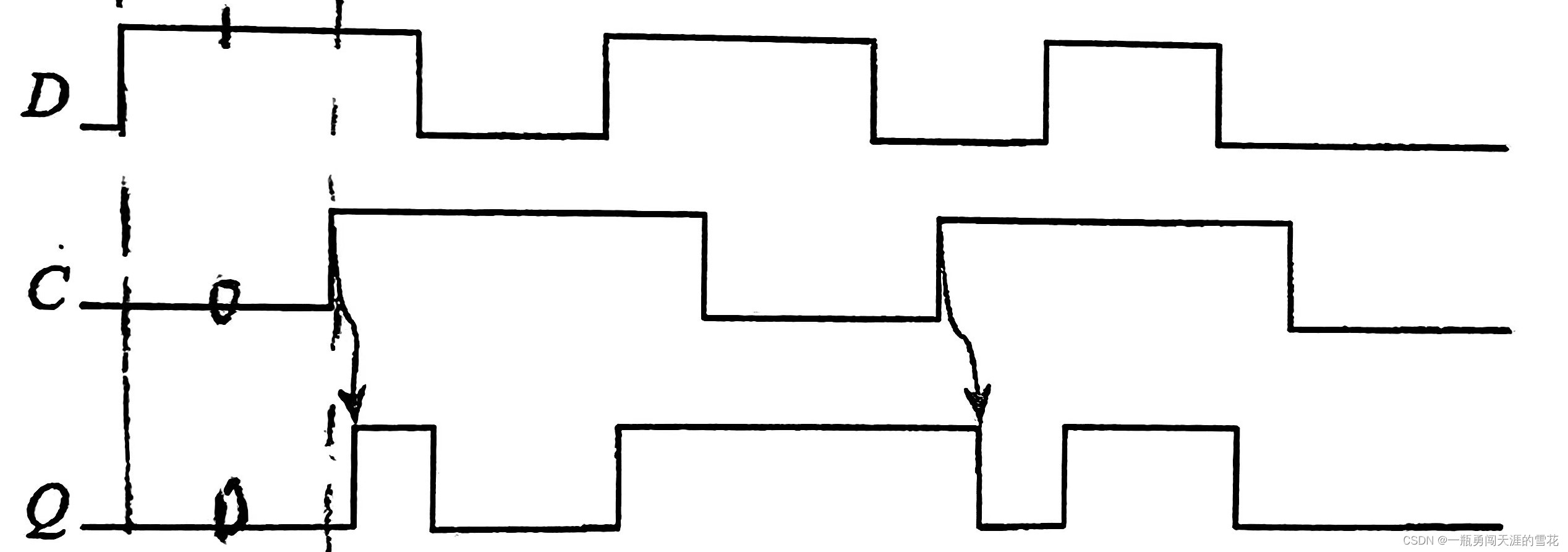

图13.D锁存器的时序图

在上面的“D锁存器特征表”中:0表示低电平,1表示高电平。

对于D锁存器,存在以下规律:

D锁存器存在两个输入端,其中,C端是控制电路锁存信息的使能信号,用于控制何时读取并锁存输入端D的信号。当C为1(信号有效)时,锁存器处于“开状态”,输出端Q的值等于输入端D的值;当C为0(信号无效)时,锁存器处于“关状态”,此时,无论输入端D如何变化,输出端Q都不发生改变。

(三)D触发器的定义

D触发器(D flip-flop)是一种数字电路元件,用于存储一个比特的数据。它是一种时序逻辑电路,具有两个稳定状态,通常称为SET(置位)和RESET(清零)状态。

(四)D触发器的图示、模拟电路图及其分析

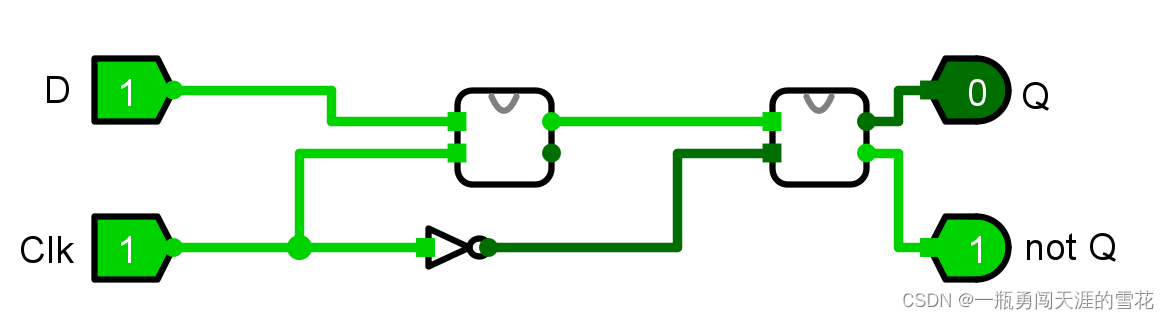

学习过程中了解D触发器是由两个D锁存器组成,而D锁存器是由使能信号控制门电路与简单的RS触发器组成的,此处我们选用由与非门组成的RS触发器来组成D锁存器从而组成D触发器。

图14.模拟电路图(D锁存器已进行封装)

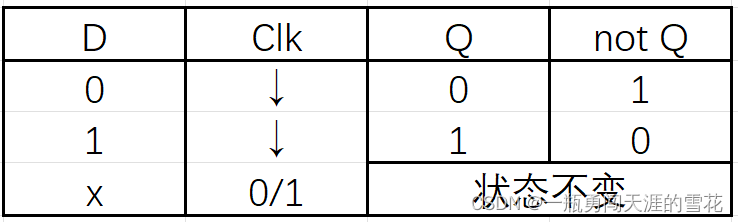

图15.D触发器特征表(箭头表示电平降低)

在上面的“D触发器特征表”中:0表示低电平,1表示高电平,“↓”表示电平降低。

对于D触发器,存在以下规律:

- Clk=1时,主锁存器(左端的锁存器)输出端Q会与输入端D信号变化一致,而从锁存器(右边的锁存器)处于闭状态,故总输出Q保持不变。

- Clk由高电平变为低电平时,主锁存器(左边的锁存器)锁存当前D的状态,传递至中间输出Q并保持不变。而从锁存器现在处于开状态,即最终输出Q与中间输出Q的状态保持一致。即最终输出Q输出的状态与输入D一致。

综上所述,D触发器最终输出Q只会在时钟Clk电平下降时,对D端进行信号的锁存,其余时间输出端信号具有保持的功能。

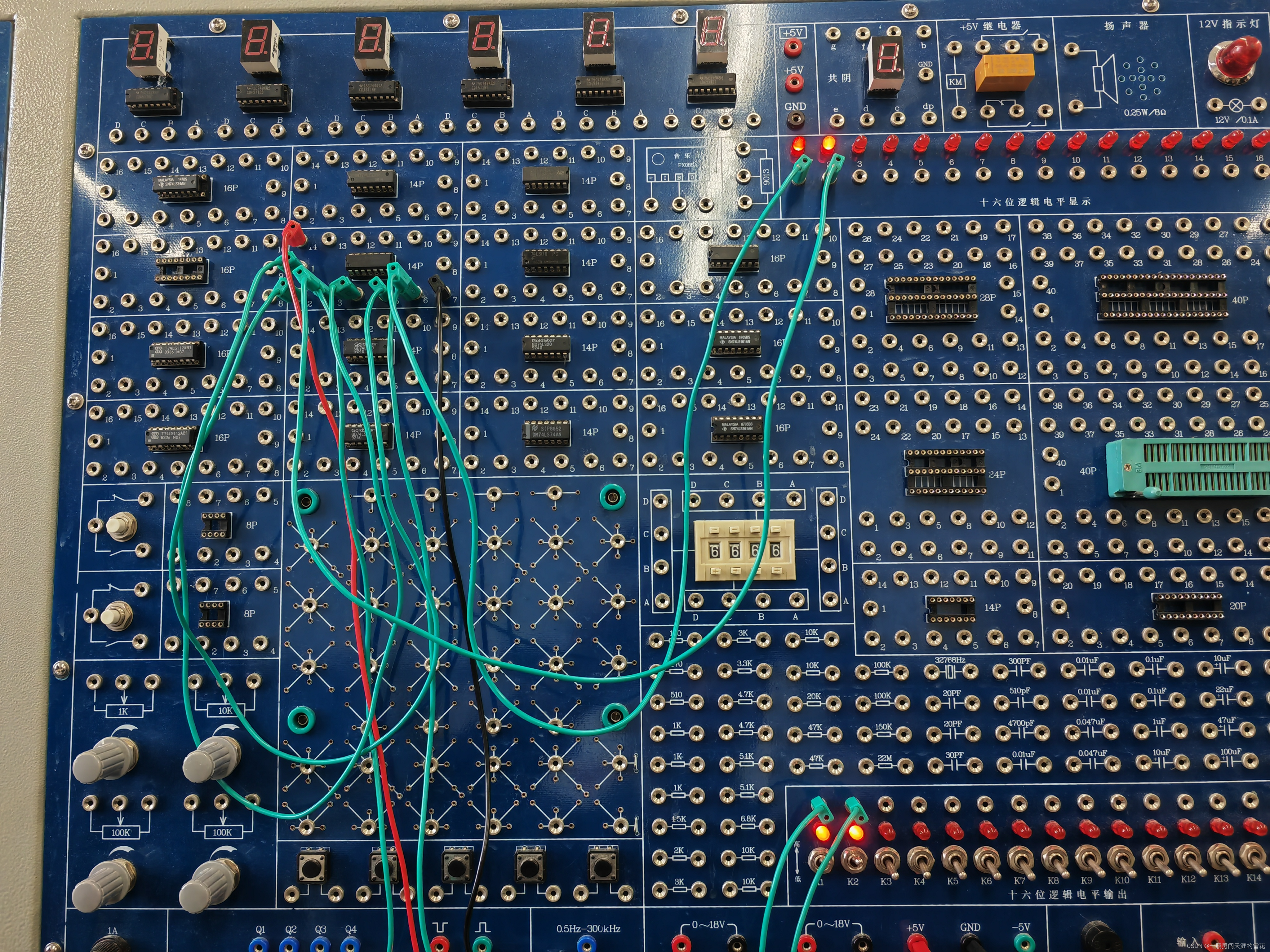

实验过程中实际图:

3686

3686

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?