FPGA用硬件实现的可编程灵活性,具有两面性。

既是一种祝福,也可以看作是梦魇。

能够灵活地做事,但代价是做事的速度太慢:应用编程难度大,开发周期长。

如今开源软件在FPGA上的应用,还只是相当于二十年前的GPU,甚至还有所不如。

什么是FPGA?

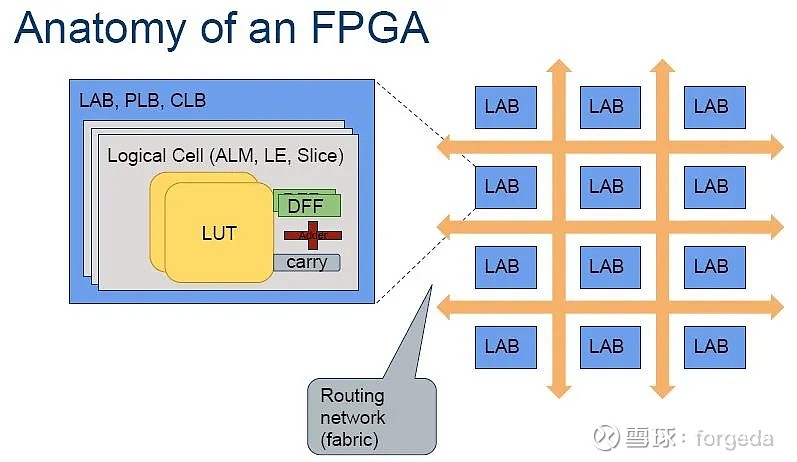

在芯片架构上,LUT+MUX+DFF的逻辑单元(Logic Cells)组合,拥有足够的灵活性,充分的自由度。

组合逻辑的灵魂是LUT,DFF则是时序逻辑的核心。

多路选择器MUX,是构建多级复杂逻辑的优选项,起到类似于“叠罗汉”的作用:

2个2输入的LUT,加上1个MUX,构成一个3输入的LUT;

两个3输入的LUT,加上1个MUX,构成一个4输入的LUT;

听起来就像绕口令。

再以Logic Cell作为基本的组成单元,就像生物体的细胞一样,相互连接,形成岛状结构,再组合成更大的任意模块。

LAB,PLB,CLB只是各个厂商的爱称不同,LAB姓阿尔特拉,CLB则是赛灵思的仔。

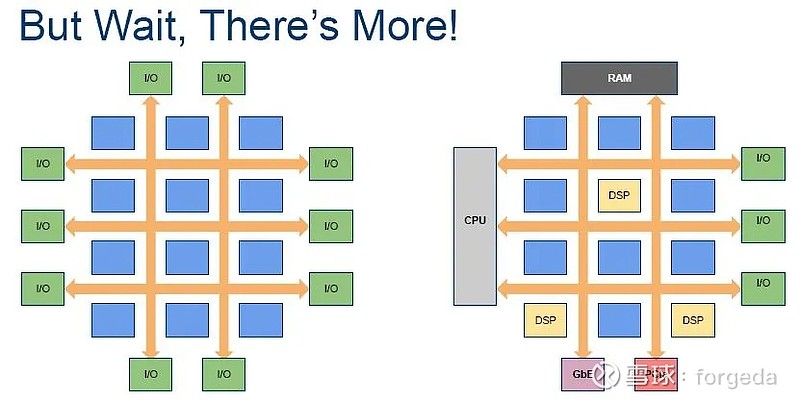

芯片结构还在持续进化过程中。根据不同的应用领域和特定需求,增加不同的异构模块。

比如,为信号处理添加DSP;

需要加大缓存数据量?那就是更多的BRAM;

如果是为了强化对复杂程序的控制,就直接上大杀器,内嵌CPU;

想要更快的数据交换能力,就增加PCIe,以太网接口等等。

现在的AI加速时代,那就再加上相应的模块,如赛灵思最新Versal架构里的AIE。包括Versal AI Edge Series的VE2302等系列。

号称万能芯片或特种芯片,绝非浪得虚名。

总是用来和CPU比性能,与ASIC比灵活。

田忌赛马,全看你咋比。

和GPU比,也好说,可以是功耗、单位效能“更优”,更常见于研究性质的“学术论文”。

硬件可编程逻辑器件,听起来像软件,但终究是芯片硬件。

生成位流并载入到FPGA,就化身成为硬件或固件使用了。

如果是反熔丝的FPGA类型,就只有一次编程(烧写)机会,用户自己仅有的一次“流片”而已。

不像GPU应用开发,有标准的软件编程模型,如大名鼎鼎的CUDA;

也与CPU不同,处理器指令集可以保持前后兼容。

FPGA的应用开发,是用硬件语言编写。不管是Verilog,还是VHDL,开发人员几乎都不会考虑“兼容性”和“可移植性”。

即便是同一厂商的“同款芯片”,也有“”差异性”。

仅从Kintex,Virtex、Artix、Spartan、Zynq这些风格各异的名字上看,就让人眼花缭乱,彼此不像是亲兄弟,更类似表亲关系。

同一个芯片型号,仅是管脚封装、速度等级等不同,也需要用户有不同的辨识度。

仅是7A35T这一款型号,包括车规级芯片在内,就多达39个品类。

想要对应用设计进行无缝移植?不存在的。

一言难尽的EDA工具

作为“价格亲民”的ASIC,对于用户将硬件电路编程为自己专属的类DSA芯片使用,FPGA用“位流配置”来实现硬件定制。

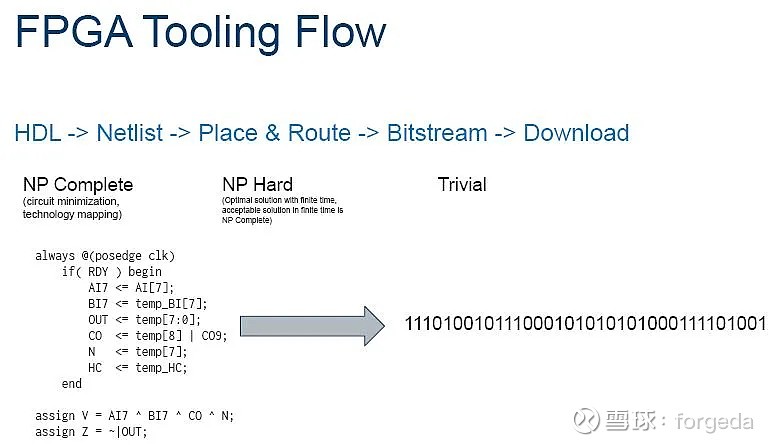

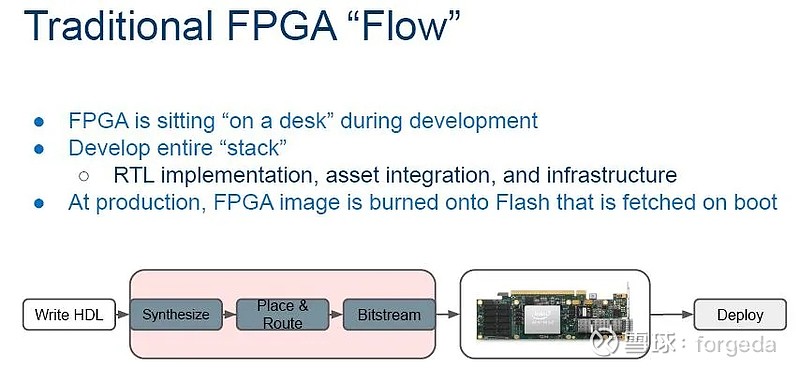

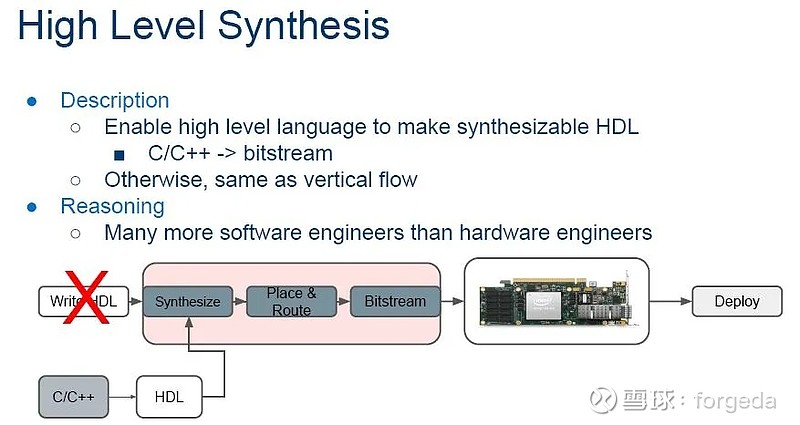

综合、仿真、布局布线、位流生成等前端设计环节,与ASIC芯片设计所需的开发流程,完全相同。

这也是用FPGA生产的专用设备,不管是硬件仿真平台(Emulation),还是IC物理原型验证系统(Prototyping)。

为CPU/DPU/GPU/AI等ASIC芯片设计,提供调试验证服务的基础。

FPGA厂商的专用EDA工具,居于统治地位。

不论是赛灵思的Vivado、阿尔特拉的Quartus、莱迪思(NASDAQ:LSCC)的Diamond,还是MicroSemi(NASDAQ:MCHP)公司的Libero,都是自成体系,只支持自家的器件。

提供Synthesis(综合), Timing(时序分析), Place and Route(布局布线), bitstreams(位流生成)等各个环节。

贯穿整个设计阶段的全部流程。

环环相扣,紧密衔接的“全流程”服务。

其中,赛灵思对开源工具的态度,更为友好,对第三方EDA软件,也相对开放。

可以有限度的融合使用。

在所有厂商的Synthesis、Timing级别,以及数字仿真器(Simulation)等方面,传统EDA三巨头,以及美国的Aldec公司在内,占有一席之地。

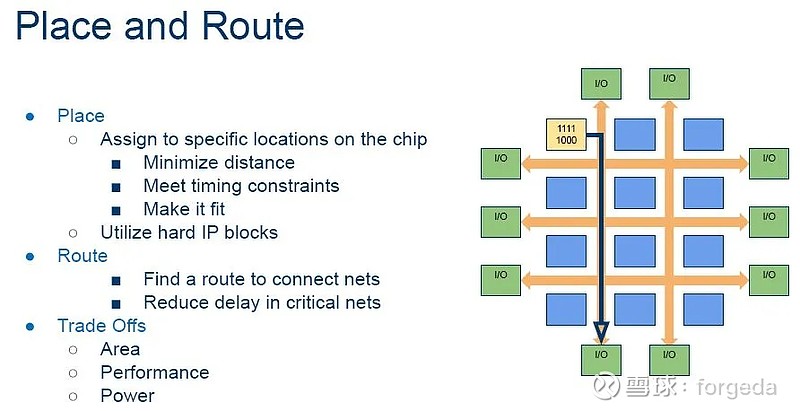

但进入到布局布线阶段,一定都是各个FPGA芯片厂商,自家专用EDA工具的独门绝技。

作为位流生成前的最后一个编译环节,因与芯片结构等核心技术紧密相关。

只能是芯片厂商自己的团队,独立研发。

最后以0/1二进制数据集合呈现的位流(bitstream),是用户应用开发的最后设计成果。也是从工程师能够理解、易于仿真验证的“数字逻辑世界”,进入到“芯片物理世界”的分界线。

包含了所有的设计信息:

代表设计在编译综合之后,已经由LUT正确地编程表示(Synthesis Results,represent the LUT programming );

并且布局到了合适的模块位置上(Place Results,in the right locations);

模块之间也建立了正确的连接关系(Route Results, with the right connections)。

作为用户最宝贵的核心资产。

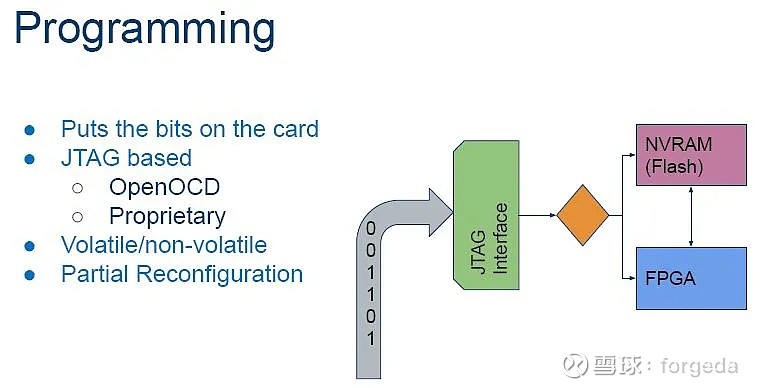

对位流数据进行压缩、加密、签名后,再载入到芯片,也就完成了“定制芯片”的设计过程。

可以通过JTAG下载,或者预先“烧写”在外部存储器中(比如Falsh),上电后直接完成芯片配置。

在运行过程中,还可以用部分重配置进行功能升级和更新。

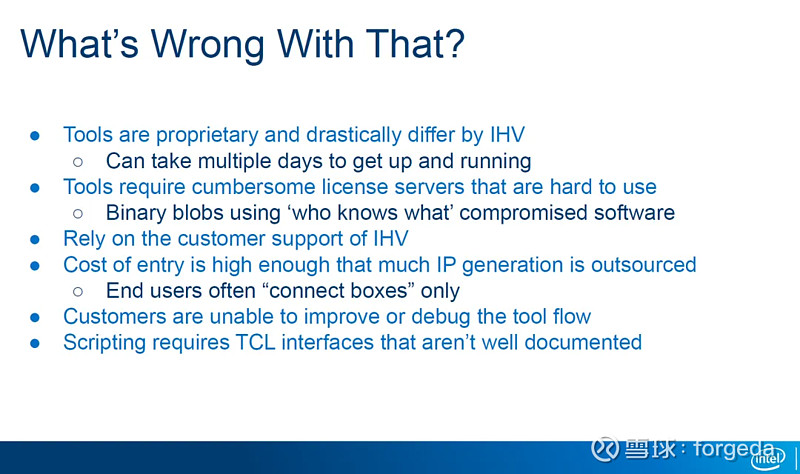

浏览一下网络,你会很容易发现一些关于供应商EDA开发工具“翻车”的故事。

FPGA芯片结构如此复杂,配套的专用EDA工具更是复杂度加倍。

当应用设计中的BUG,和供应商工具可能的BUG,都耦合在一起的时候。

调试验证工作,更是难上加难。

有传闻说,就算是行业标杆SpaceX公司,在调试基于赛灵思的FPGA设计时,就曾遇到了大麻烦。

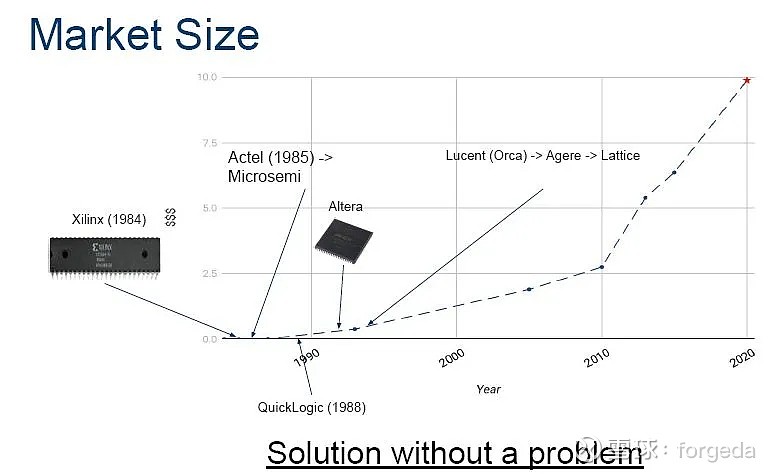

快速增长的FPGA应用市场

早期稳定增长。

相当平缓,波澜不惊。

从1984年赛灵思推出首款芯片XC2064开始,一直到90年代末,整个市场增长才开始有所起色。

2010年,有一个向上抬头的起势拐点,明显不同以往。

也就是人工智能萌芽阶段,刚开始得到发展的时候。

2011年,微软启动的Catapult项目,从最初的只是加速bing搜索,后来将其称之为AI黎明。

虽然晶体管密度的增加,帮助供应商创造了更高性能的FPGA,但增长加速的真正原因,主要是最终找到了擅长的加速应用。

从某种程度上说,有别于以往拿着锤子找钉子的意思。

纵观FPGA应用发展史,可划分为三个阶段:

传统的优势应用,FPGA is FPGA

一个常见的用途是对ASIC设计进行前端验证,用FPGA的硬件速度直接进行仿真,运行速度比软件数字仿真要快得多。

这也是FPGA最具垄断优势地位的仿真加速应用。

或者当一个标准/协议仍在演进过程中,比如媒体编解码器,通信协议等,可以对FPGA进行现场升级,以适应可能的更新升级。

总之,如果是小批量应用(300万片以内?),需要的芯片数量较少。

那么直接使用FPGA,而不是生产专用集成电路ASIC,可能是非常划算的。

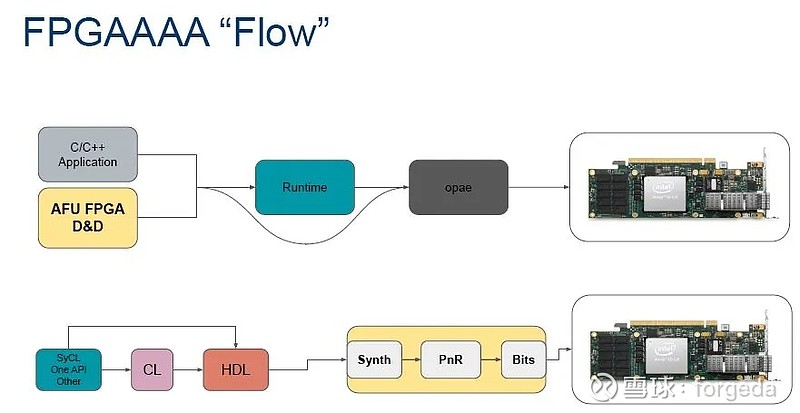

作为算力加速器

FPGA As An Accelerator,FPGAAAA!

近数据源加速,尽可能在靠近数据源的地方,利用FPGA的硬件性能,就地就近进行数据处理。

利用厂商的运行时支持库,允许应用程序访问FPGA加速器。

如英特尔的OpenVINO, OpenStack Cyborg或Kubernetes设备插件,将数据负载导入到FPGA的加速路径上。

可以尽可能减少数据迁移。

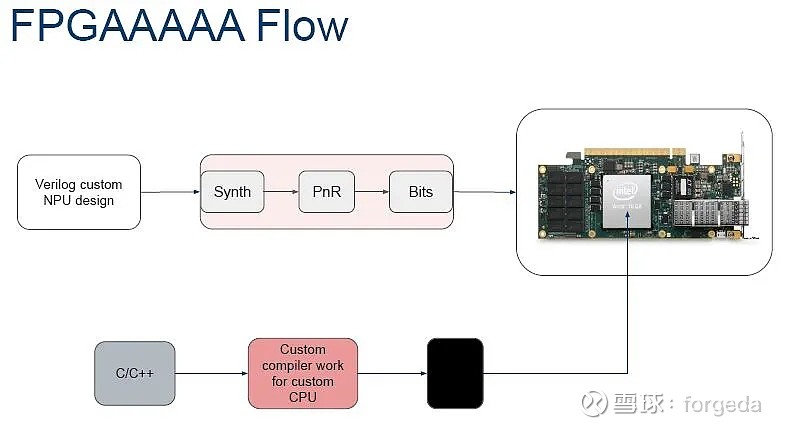

作为AI加速器

FPGA As An AI Accelerator,FPGAAAAA!!

其中最为有名的,无疑是微软(NSADAQ:MSFT)的脑波了。

Microsoft’s Project Brainwave claims win over Google TPU

用25万片FPGA,构造当时世界上最大的AI计算机。

FPGA还在进化中,性能越来越强大,设计变得更为复杂的趋势。

仍在继续。

但几乎所有论坛中,讨论大多数关于FPGA的问题,都是有关厂商专有工具,以及如何使用这些工具。

大家都只是试图用它们来精心打磨一个产品。

没有人试图改进流程或工具。

编者后记

FPGA早期的应用市场,主要是面向教育和仿真服务。

现在已深入到国民经济的各个角落。

四十年来,除了性能增长之外,其成本和能耗降低1000倍以上。

容量增长了1万倍以上。

一直走在异构计算、硬件加速最前沿的EDA辅助验证市场,更为明显。

硬件容量已经是初代XC2064,只有64个逻辑单元(LCs)的近30万倍。

时至今日,不管是传统的优势领域,还是当前火热的边缘AI加速应用,在芯片架构和生态上,尚未出现类似英伟达(NASDAQ:NVDA)公司的CUDA类似的重大突破。

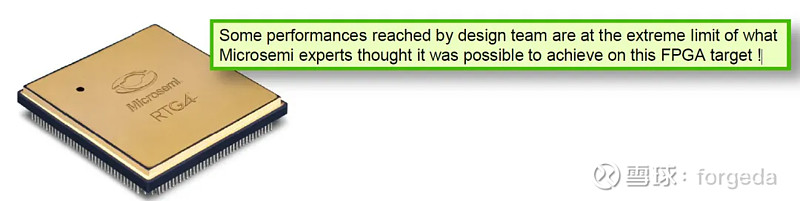

对于资深FPGA硬件工程师,即便对于时下火热的端侧AI加速应用,虽然也可以做到看上去没什么“堵”点,应用设计完全可以打磨实现。

但当用户介绍自己使用FPGA的设计开发,在产品卓越性能指标的旁白上,总是会加上这么一句:一些性能达到了原厂专家级的水平。

用欧洲巨头空客公司(PINK:EADSY)的航天与防务部门话说,如果是使用Microchip公司(NASDAQ:MCHP)的抗辐FPGA:

“设计团队在这款芯片上实现的性能,厂商专家认为已经是器件本身的极限!”

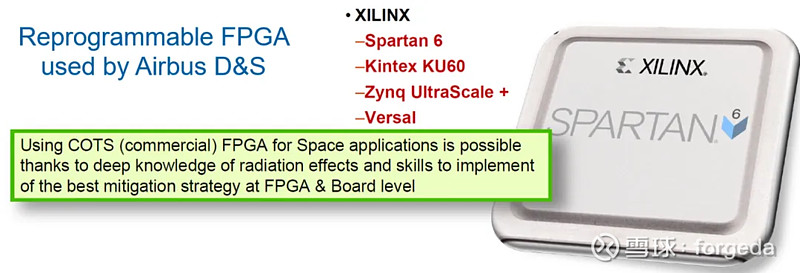

使用赛灵思公司FPGA的设计开发,画风类似。

“在航天应用中之所以能够使用商用级FPGA(Commercial COTS),得益于对辐射效应的理解,以及在FPGA设计、板卡级的最佳缓解策略实现”等等。

应用编程难度大,开发周期长,从业人员少。

几乎是行业的老生长谈了。

应用编程难度大,这是FPGA的特性,只能寄希望于芯片厂商的重大突破,短期无解。

开发周期长的这个行业长期难题,可能成为不一样的市场服务机会。

一些复杂设计的调试验证所需时间,按照EDA巨头西门子(PINK: SIEGY)的统计数据,已经占到开发时间的50%左右(摘自“FPGA的中场战事”)。

代表最先进调试技术的EDA硬件辅助验证,又主要服务于需要流片的超大规模IC设计,长期与FPGA应用市场距离遥远。

这些EDA供应商面向大量FPGA应用终端用户,推广使用的动力不足,快速扩张的能力受限。

打个比较辣眼睛也很刺耳的类比:

在软件行业已经进化到海量APIs的云原生时代,熟练驾驭FPGA的硬件工程师,就像是维多利亚工业时代的高手,还在沿用刀耕火种的白鹿原时代工具,在智能化时代精心打磨高科技产品。

虽然都是使用FPGA板卡,调试一直是IC设计行业用户的痛点,但对于遍布FPGA垂直细分领域的各个行业用户,好像从来不是问题。

最多是需要工程师多花些时间。

在设计阶段,大部分工程师使用的EDA工具,更像是芯片厂商的“恩赐”:

They are at the mercy of the vendor

昂贵工具烧钱,免费工具烧脑,比较费工程师发量。

全文完,感谢您的耐心阅读

628

628

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?