AI大模型的出现,是人工智能领域的一次重大飞跃,同时也为编程领域带来了变化。

以GPT、文心一言、通义千问等为代表的大模型,通过在海量互联网数据上的预训练,特别是大量GitHub代码的融入,让模型阅读和编写代码的能力。

本文以【智谱清言】为例。

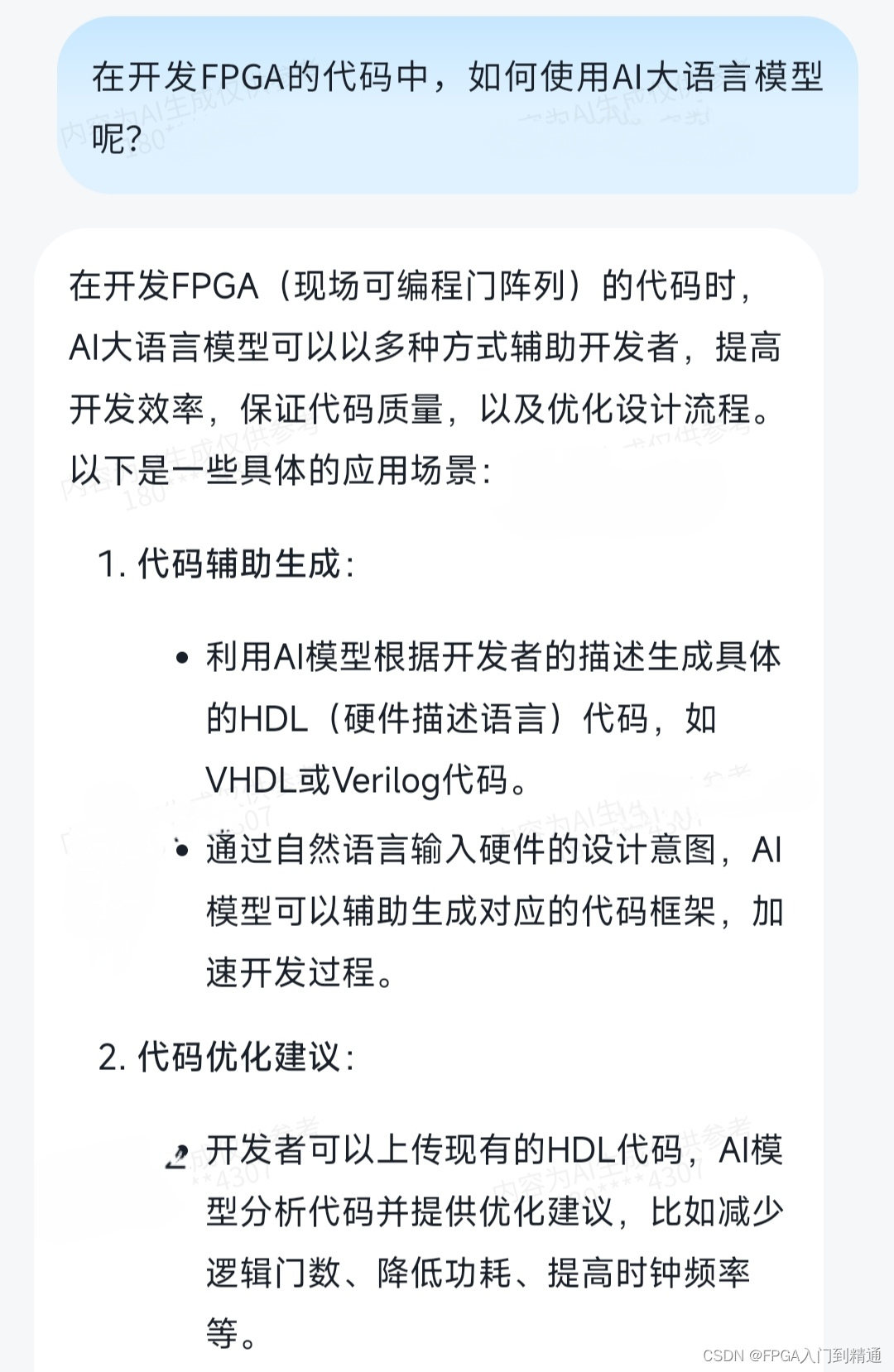

那么在我们FPGA开发中,如何使用AI呢?

这里我们直接问下“智谱清言AI”:

这里具体分享一下:

1、中英文翻译助手

在FPGA开发中,经常会需要阅读英文手册,写代码过程中,定义变量名、函数名,这些都可以直接调用AI的翻译功能专有智能体。

2、辅助代码生成

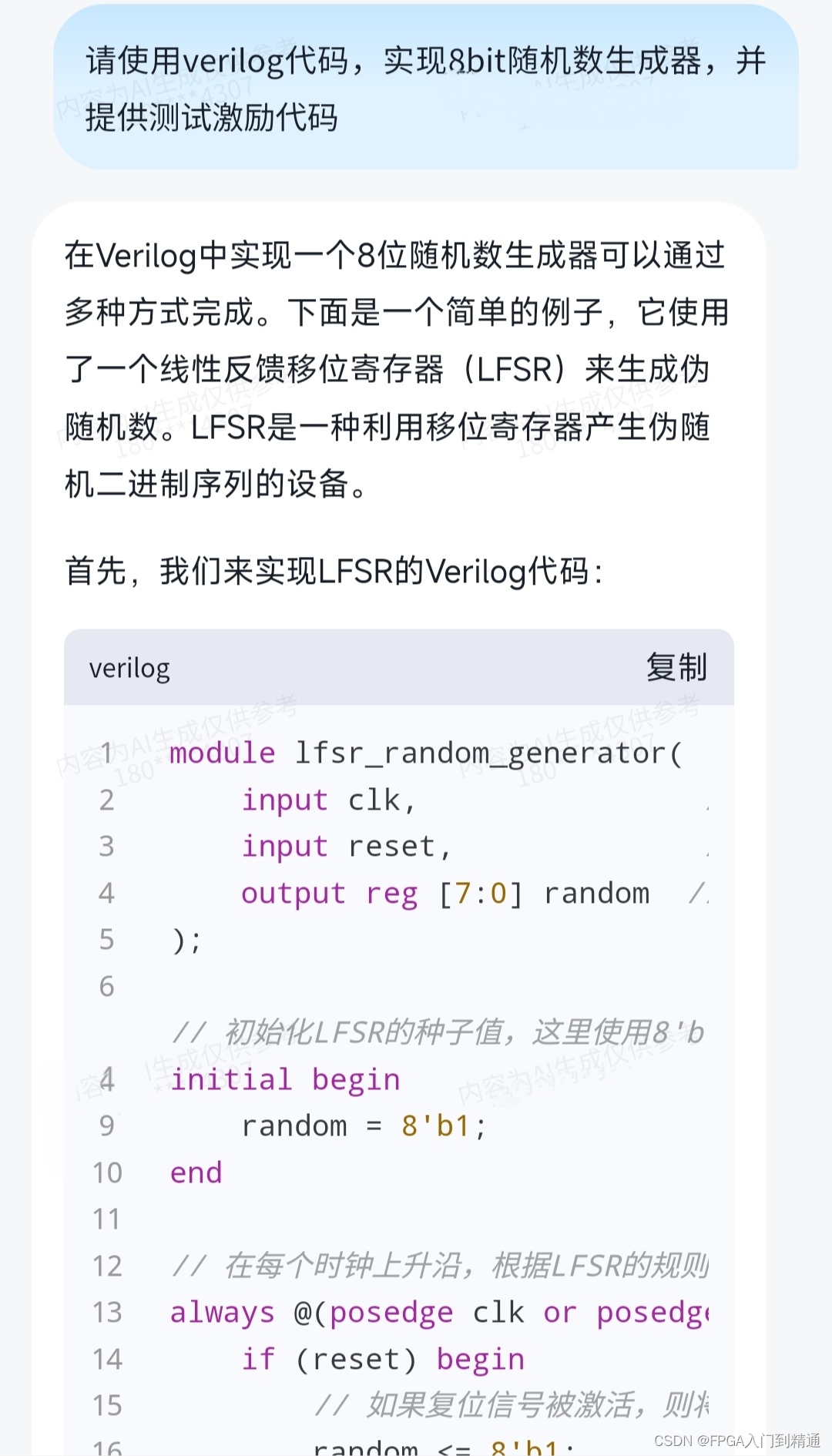

直接给大模型描述需要生成的功能描述,让AI使用verilog生成。

这里给大家演示一下:

给出提示词后,大模型直接回复了我们要求的内容,如果这个代码不符合要求,我们可以继续把要求发给AI大模型。

LFSR的verilog代码如下:

module lfsr_random_generator(

input clk, // 时钟信号

input reset, // 异步复位信号

output reg [7:0] random // 8位随机数输出

);

// 初始化LFSR的种子值,这里使用8'b1作为初始值

initial begin

random = 8'b1;

end

// 在每个时钟上升沿,根据LFSR的规则更新随机数

always @(posedge clk or posedge reset) begin

if (reset) begin

// 如果复位信号被激活,则将随机数重置为初始值

random <= 8'b1;

end else begin

// 使用XOR门和反馈模式来更新随机数

// 这里使用一个简单的反馈模式:x^8 + x^6 + x^5 + x^4 + 1

random <= {random[6:0], random[7] ^ random[5] ^ random[4] ^ random[3]};

end

end

endmodule

测试激励代码:

module testbench;

// 时钟信号和复位信号

reg clk;

reg reset;

// 8位随机数输出

wire [7:0] random;

// 实例化LFSR模块

lfsr_random_generator lfsr(

.clk(clk),

.reset(reset),

.random(random)

);

initial begin

// 初始化时钟和复位信号

clk = 1'b0;

reset = 1'b1;

// 在第10个时钟周期释放复位信号

#100 reset = 1'b0;

// 持续运行一段时间

#10000 $finish;

end

// 时钟生成器,每10个时间单位产生一个时钟周期

always #5 clk = ~clk;

// 监控随机数的变化

always @(posedge clk) begin

if (!reset) begin

$display("Random Number: %b", random);

end

end

endmodule

这里的提示词如下,大家可以试下:

请使用verilog代码,实现8bit随机数生成器,并提供测试激励代码

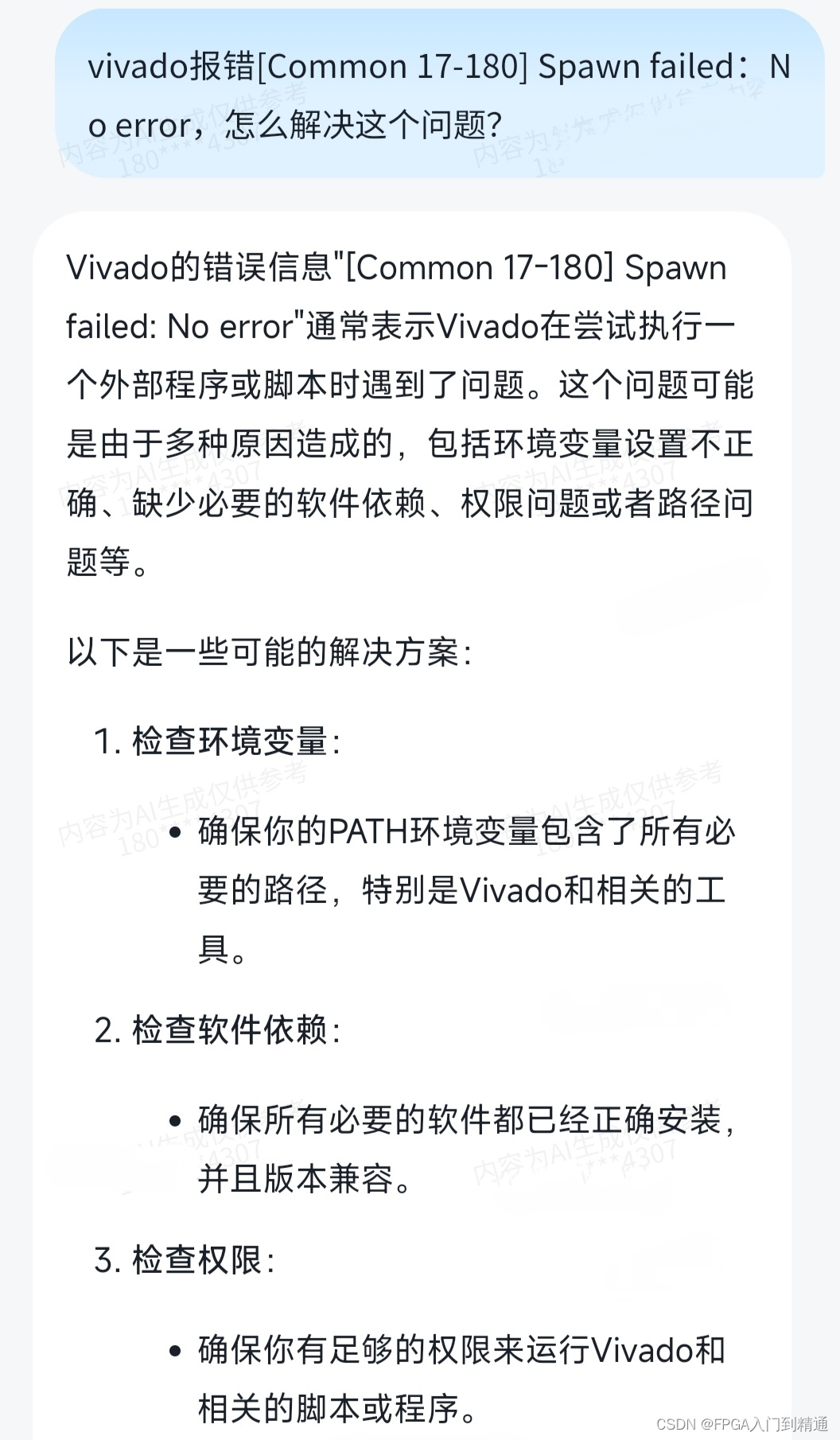

3、问题辅助分析

把我们开发中遇到的问题或报错,直接发给大模型,让他帮忙分析和提供建议。

当然了这些回答可能也解决不了问题,可以继续添加更详细的要求,继续提问。

今天分享到这里,大模型还有更多更丰富的功能,后续将继续分享,借助AI大模型可以在一定程度上提升我们的开发效率,大家可以玩起来。

如果需要更多学习资料和源码,想要学习FPGA实战入门,想要学习AI赋能FPGA开发,请阅读下面这篇文章:

2340

2340

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?