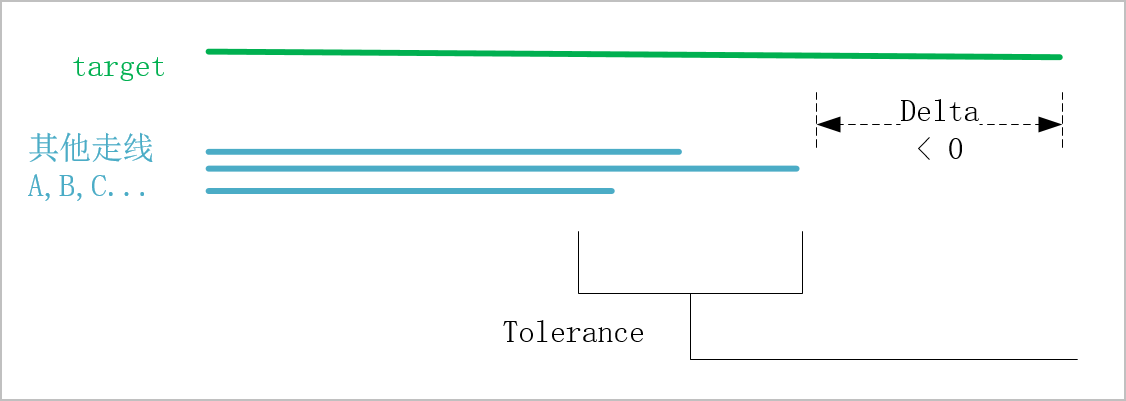

在包含clock信号线的功能模块组中,如LVDS,HDMI,DSI,并口LCD,HDMI功能模块中,均含有clock信号线,在这些功能模块中,其他走线均以clock为参考,且其长度通常均要短于clock。

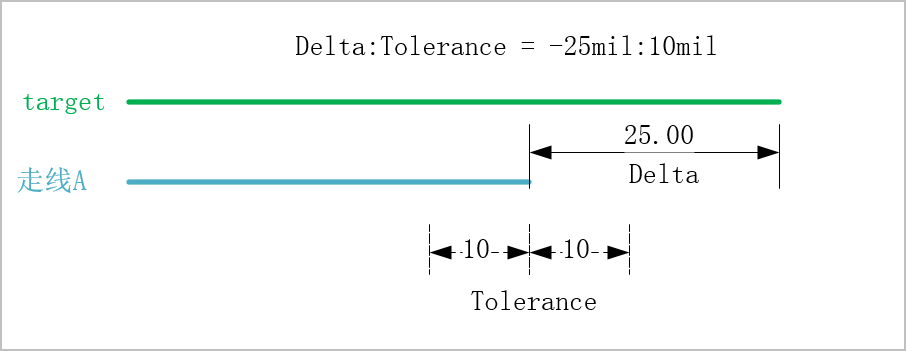

在allegro的constaintde Relative Delay设定中,这些功能模块的组内等长设置都是以clock为Relative Delay的target,且在Delta:Tolerance设定一栏中,Delta不像通常取值为0,而是负值。如Delta:Tolerance的值为-25mil:10mil,即Delta的值为-25mil。

比较Delta取值为0,如Delta:Tolerance的值为0mil:10mil,那么表示Relative Delay的取值为+-10mil,该走线的长度可能比target少10mil,也有可能比target多10mil,即该走线不一定比target短。

那么怎么表示比target"短"呢?

在allegro的constaintde Relative Delay 组中,为了约束某些走线比target短,Delta:Tolerance中的Delta就取负值。这里的负值,表达的是比target"短"的概念。 如上-25mil:10mil的示意图如下:

Delta:Tolerance代表的含义,其实也可以这样理解:

在以target length + Delta为原点,以Tolerance为半径的区间内取值。区间范围为:

(target length + Delta) - Tolerance < A长度 < (target length + Delta) + Tolerance

Delta是比target少25mil,10mil除了target(clock)其余走线的容差,可以把除了clock的走线看作一组,它们的容差则是+-10mil.

且由上面的分析可以看出,Delta为负值时,还代表"短"的含义。但要注意,此时Delta > Tolerance。

8056

8056

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?