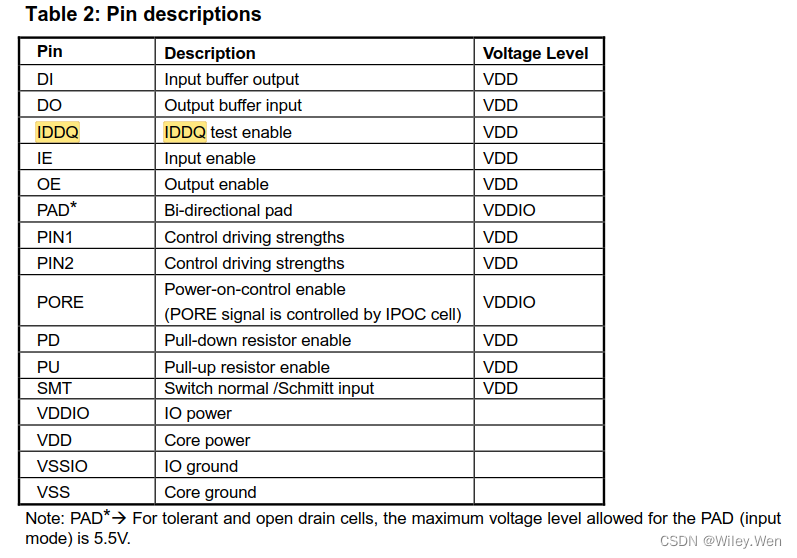

GPIO PIN

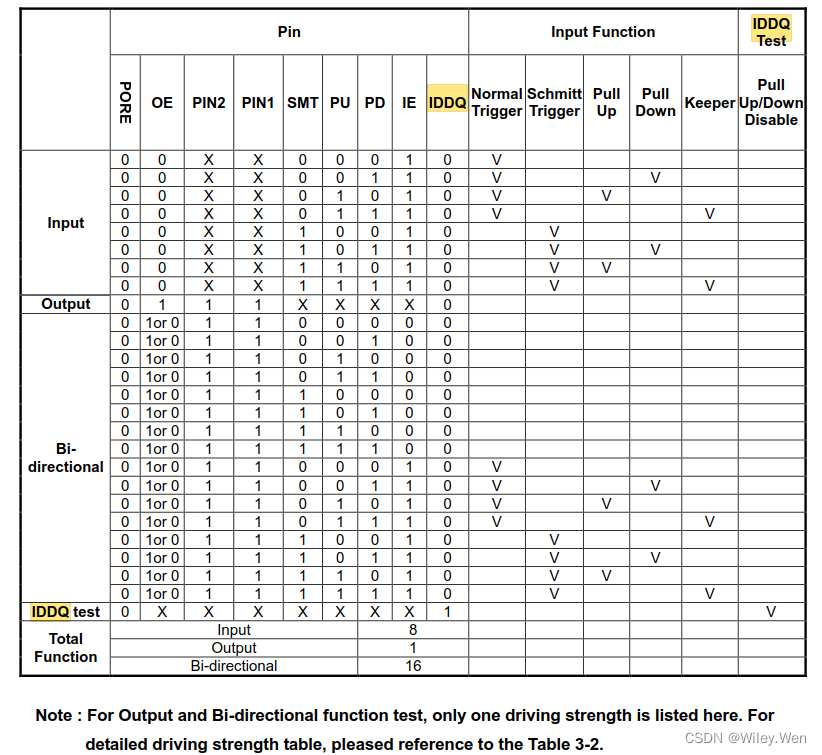

Function Table

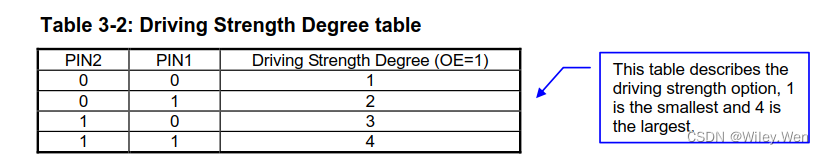

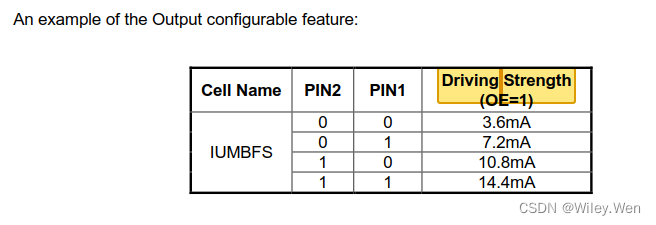

Driving Strength Degree table

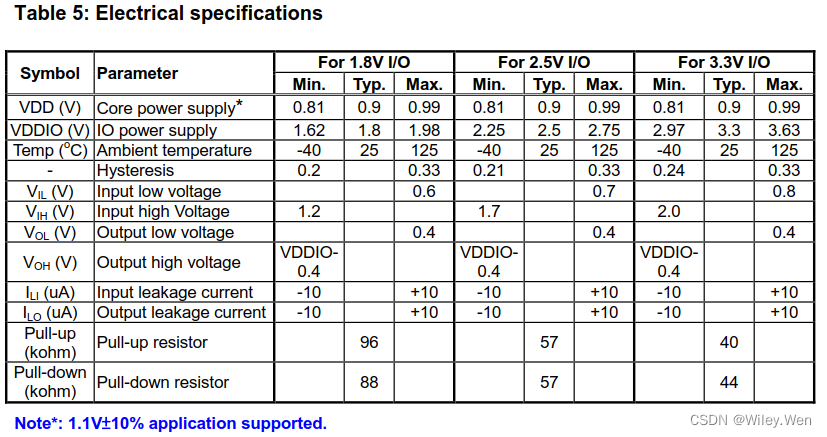

Electrical Specifications

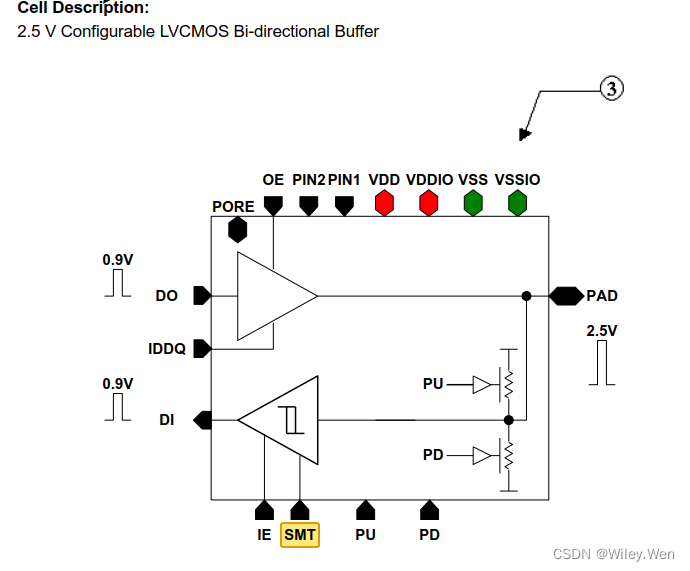

GPIO的结构

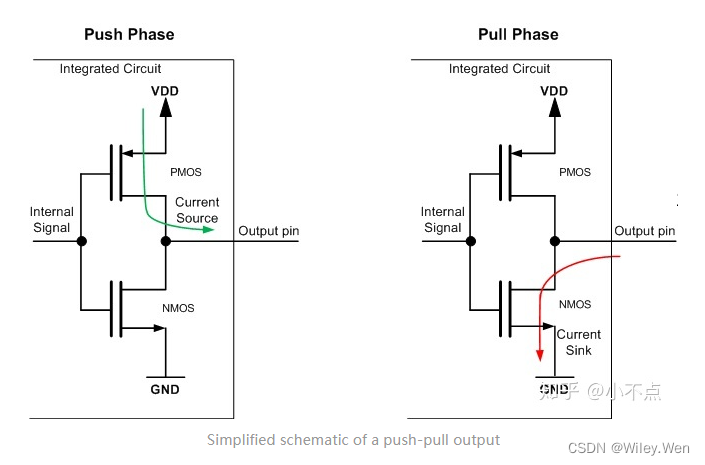

Push-Pull结构(推挽)

顾名思义,PUSH-PULL中所谓PUSH指的是把输出推到电路的VDD电压,所谓Pull指的是将输出拉到Ground电压。

如上图所示,可以看出是由一对PMOS和NMOS组成了一个简单的Push-Pull结构,具体的原理如下:

Push phase – 当连接在Mos管栅极的internal信号输入为低电平(Logic 0)的时候,PMOS管导通,电流从VDD流经PMOS管至输出端口。

Pull phase – 当连接在Mos管栅极的internal信号输入为高电平(Logic 1)的时候,NMOS管导通,电流从Output端流经PMOS管至GND。

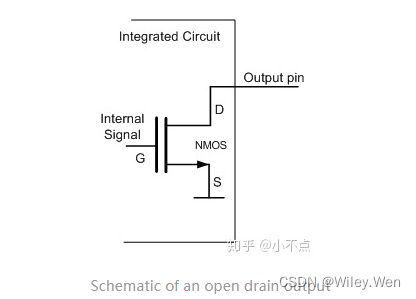

Open-Drain结构(开漏)

如图所示,可以看出开漏输出电路是由一个N沟道MOS管组成的,当NMO管导通时,电路通过NMOS管将输出拉低至GND;当NMOS管关闭时,电路输出管脚浮空。

开漏输出电路一般用于通信接口,该通信接口下同时挂着n多个devices(比如I2C结构),如上图所示,当Internal signal信号输入高电平的情况下,NMOS管导通,输出被拉低到低电平状态;当Internal signal信号输入低电平的情况下,NMOS管截至,输出高阻态(高阻态、三态、浮空都表示一个意思),此时电路对外没有展示出任何驱动能力,此时可以在外部接一个上拉电阻来实现输出高电平。

- 开漏输出的这一特性一个明显的优势就是可以很方便的调节输出的电平,因为输出电平完全由上拉电阻连接的电源电平决定。所以在需要进行电平转换的地方,非常适合使用开漏输出。

- 开漏输出的这一特性另一个好处在于可以实现"线与"功能,所谓的"线与"指的是多个信号线直接连接在一起,只有当所有信号全部为高电平时,合在一起的总线为高电平;只要有任意一个或者多个信号为低电平,则总线为低电平。而推挽输出就不行,如果高电平和低电平连在一起,会出现电流倒灌,损坏器件。

【open-drain和push-pull的总结】

对于GPIO的模式的设置,在不考虑是否需要额外的上拉电阻的情况下,是设置为open-drain还是push-pull,说到底,还是个权衡的问题:

如果你想要电平转换速度快的话,那么就选push-pull,但是缺点是功耗相对会大些。

如果你想要功耗低,且同时具有“线与”的功能,那么就用open-drain的模式。(同时注意GPIO硬件模块内部是否有上拉电阻,如果没有,需要硬件电路上添加额外的上拉电阻)[1]

IDDQ

IDDQ是指当CMOS集成电路中的所有管子都处于静止状态时的电源总电流。IDDQ测试目的是测量逻辑状态验证时的静止(稳定不变)的电流,并与标准静态电流相比较以提升测试覆盖率。

IDDQ测试运行一组静态IDD测试的功能序列,在功能序列内部的各个独立的断点,进行6-12次独立的电流测量。测试序列的目标是,在每个断点验证验证总的IDD电流时,尽可能多地将内部逻辑门进行开-关的切换。

IDDQ测试能直接发现器件电路核心是否存在其他方法无法检测出的较小的损伤。

SMT

施密特触发器(Schmitt trigger ):信号经过施密特触发器之后,模拟信号转换为数字信号0和1。

1176

1176

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?