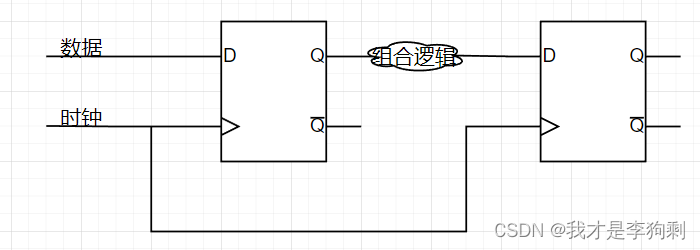

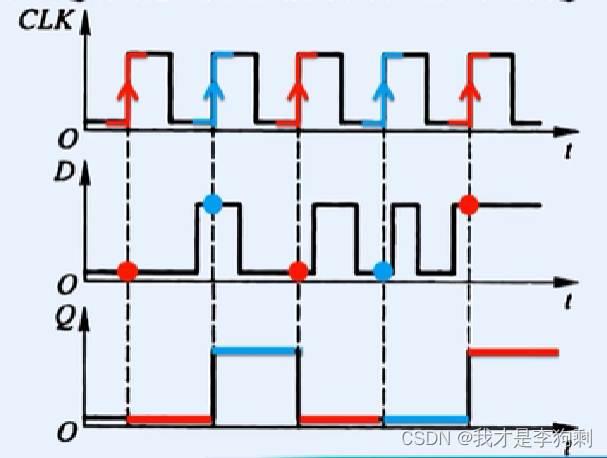

FPGA、芯片中所谓的时序电路,最核心的器件便是触发器。触发器的作用是,输出Q的值等于时钟上升沿时刻采样到的输入D的数据。

理想的沿触发器输入输出时序:

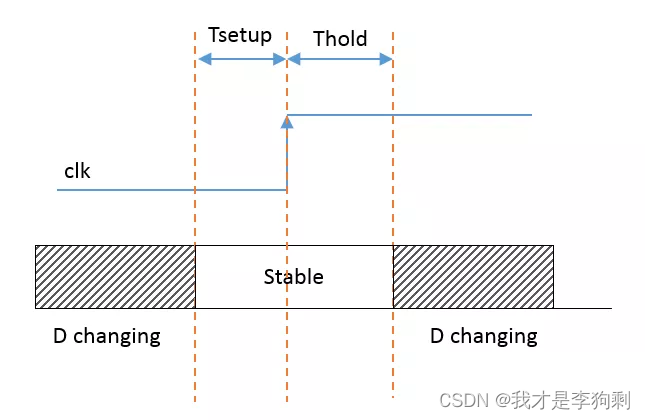

由于实际硬件电路并不是理想的,在时钟上升沿前后一段时间内,数据D必须保持稳定,才能保证触发器正确采集到D的数据。

建立时间: 时钟上升沿到来前数据需要保持稳定的时间;

保持时间: 时钟上升沿到来后数据需要保持稳定的时间。

这两个概念针触发器的,而所谓时序约束就是为了满足建立时间和保持时间。

不满足约束可能导致,某一触发器采样数据错误,继而后续触发器采样也出现错误,导致电路出错。

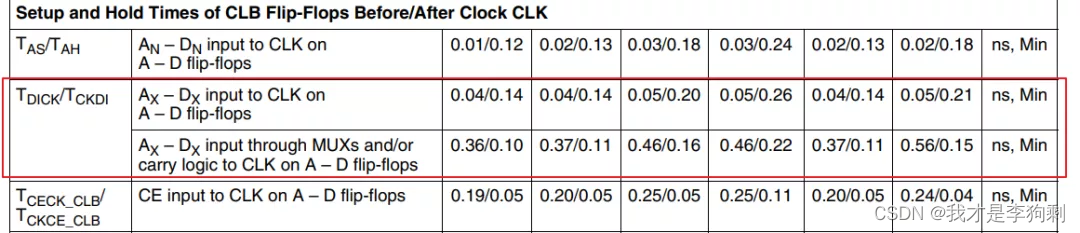

建立保持时间对于FPGA来说是由器件决定的,查看器件的《DC and AC Switching Characteristics》手册可以找到XILINX的K7系列FPGA的建立和保持时间。

文章详细阐述了FPGA和芯片设计中的关键概念——时序电路,重点介绍了触发器的作用及其对建立时间和保持时间的要求。不满足这些时序约束可能会导致数据采样错误,进而影响整个电路的正确运行。XILINXK7系列FPGA的建立和保持时间可在相关手册中查得。

文章详细阐述了FPGA和芯片设计中的关键概念——时序电路,重点介绍了触发器的作用及其对建立时间和保持时间的要求。不满足这些时序约束可能会导致数据采样错误,进而影响整个电路的正确运行。XILINXK7系列FPGA的建立和保持时间可在相关手册中查得。

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?