本文参考“何飞阳”大佬《S32K3定时器(STM&PIT)使用——基于MCAL》https://blog.csdn.net/HeFlyYoung/article/details/129069402

0、简介

相比于参考文章,本文基于S32K312 介绍PIT的使用,主要是记录开发流程,本文基于《基于MCAL的S32K3 MCU使用》的工程,环境如下:

MCU:NXP S32k312

RTD版本:SW32K3_S32M27x_RTD_R21-11_4.0.0_D2311

EB版本:tresos Studio 29.0

***本文目前主要是记录配置,后期不断完善配置内容的含义***

1、模块简介

STM system timer Module

PIT periodic interrupt timer

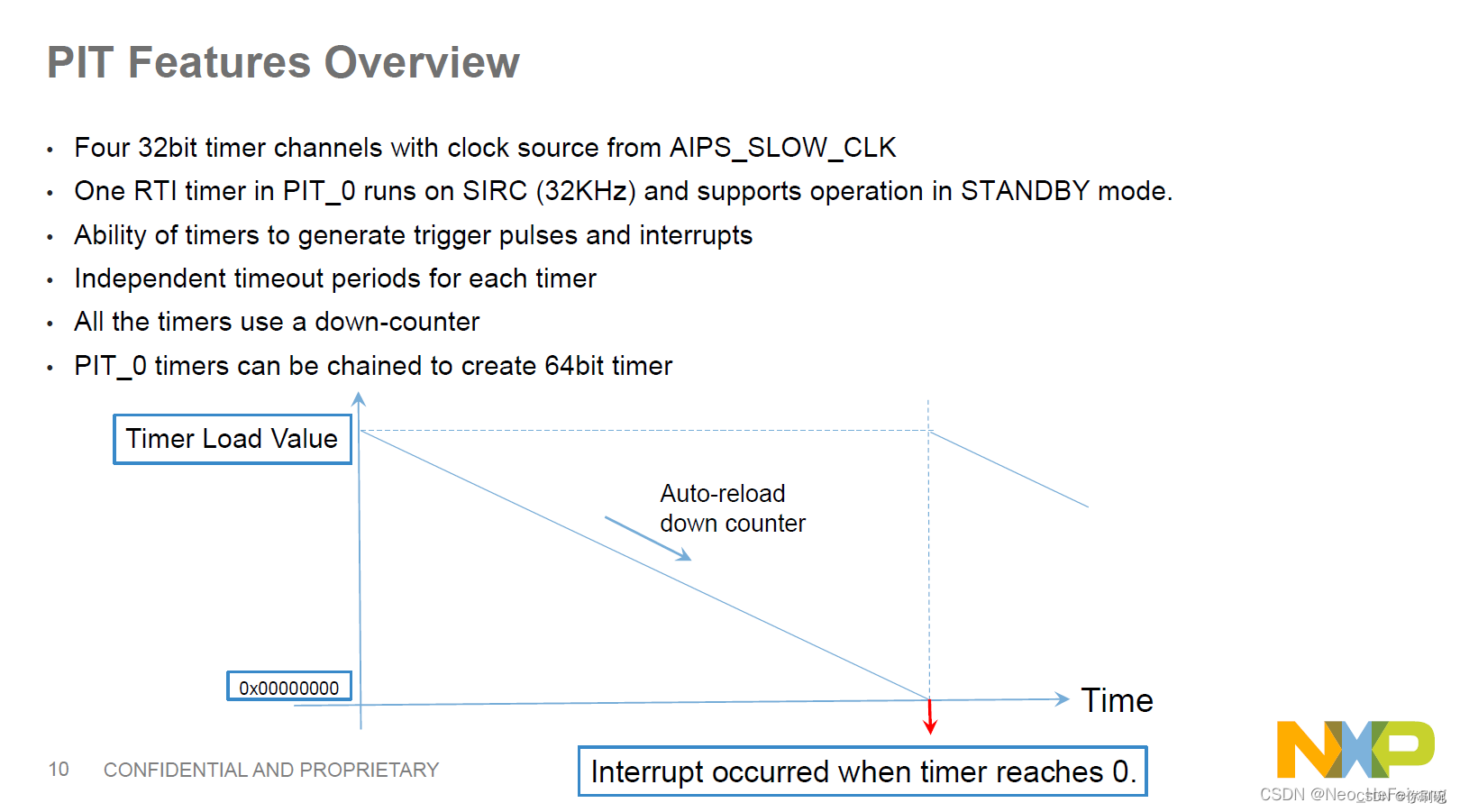

1.1 PIT

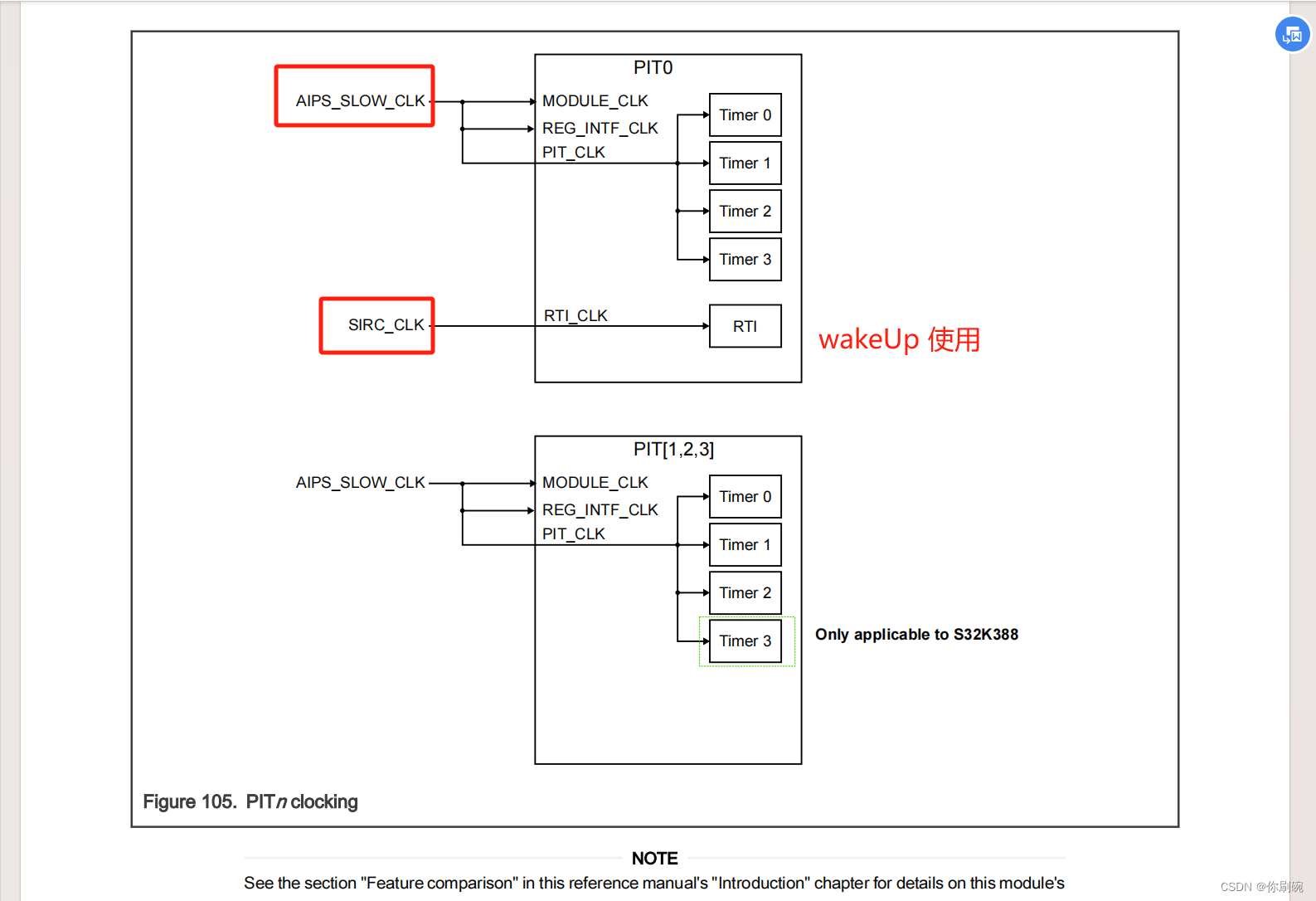

PIT时钟源为AIPS_SLOW_CLK,其中RTI时钟为SIRC_CLK,用于在standby模式下唤醒CPU。

PIT共有3个instance,每个instance又有4个channel。其中PIT_0可以被链接成为一个64bit的定时器(正常为32bit的定时器)

PIT定时器为向下计数器,counter值写在LDVAL registers中。

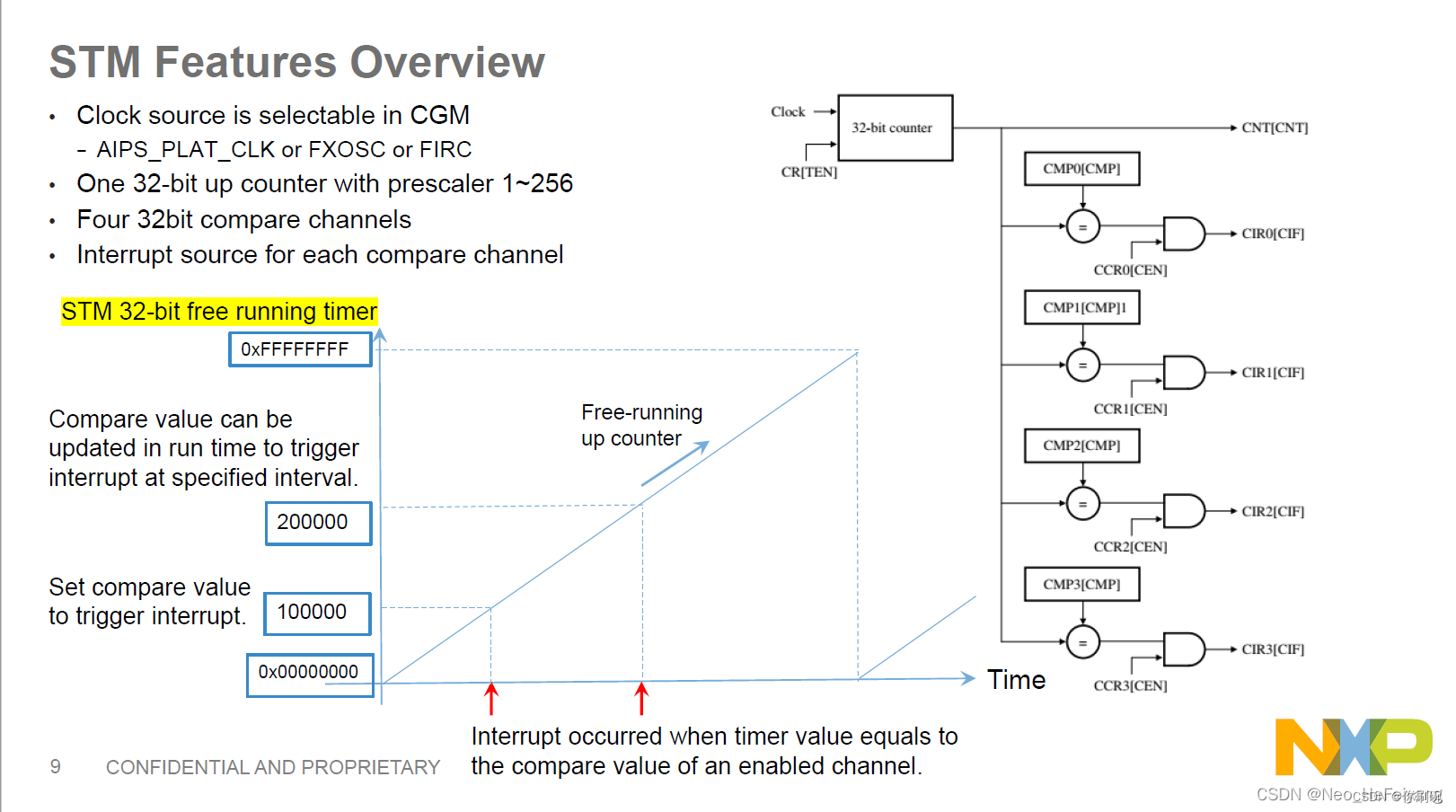

1.2 STM

STM时钟来源于AIPS_PLAT_CLK or FXOSC or FIRC,可以在CGM中选择

3个stm instance,每个instance有4个32bit的compare channel,每个channel都有独立的中断。

1个32-bit的向上计数器,具有自己独立的8位预分频器,可进行0–256级分频。

TIPS:(本文只配置PIT)

2、新建工程

2.1 新建工程

本文基于《基于MCAL的S32K3 MCU使用》的工程。

2.2 添加相关模块

GPT模块,对Mcl有依赖(主要是emios的依赖,若只使用STM和PIT只需加入此模块而无需配置此模块)。Platform用来配置定时器相关的中断。Mcu主要用来配置定时器的时钟频率。Port和Dio用来点灯方便观察实验现象。

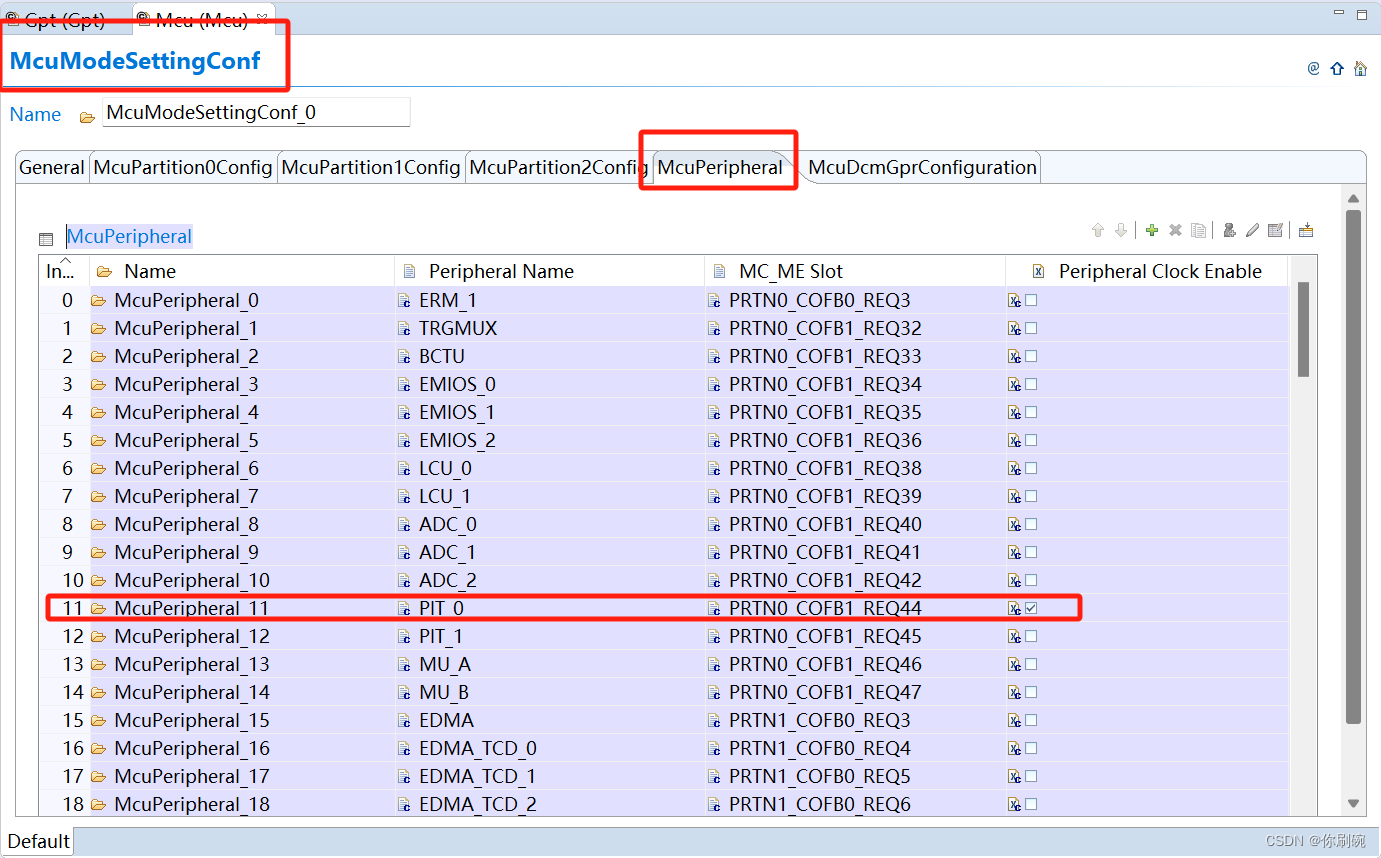

1.3 Mcu配置

Mcu中主要是打开外设时钟以及时钟源选择和提供时钟reference。

1.3.1 外设时钟

1.3.2 外设时钟

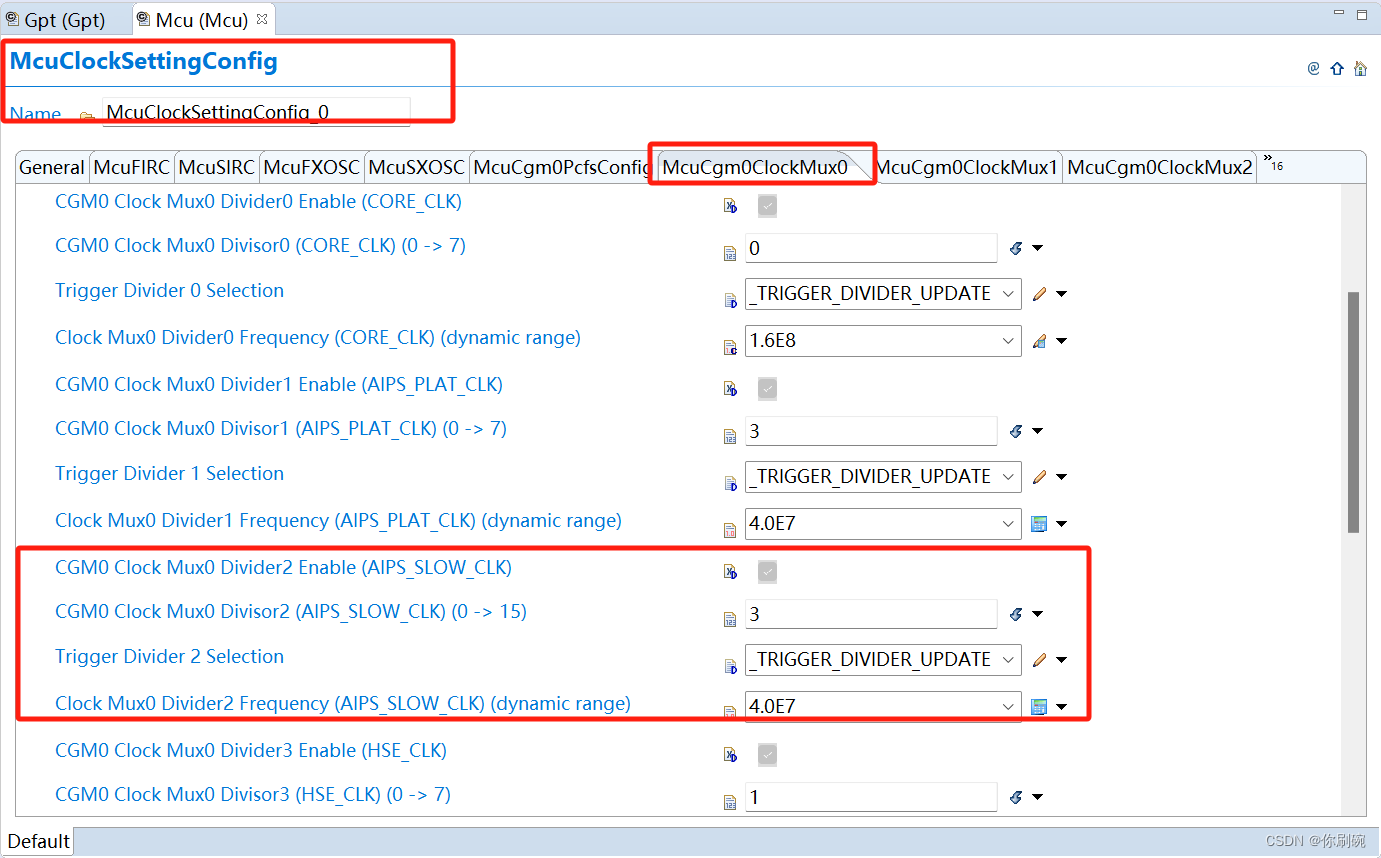

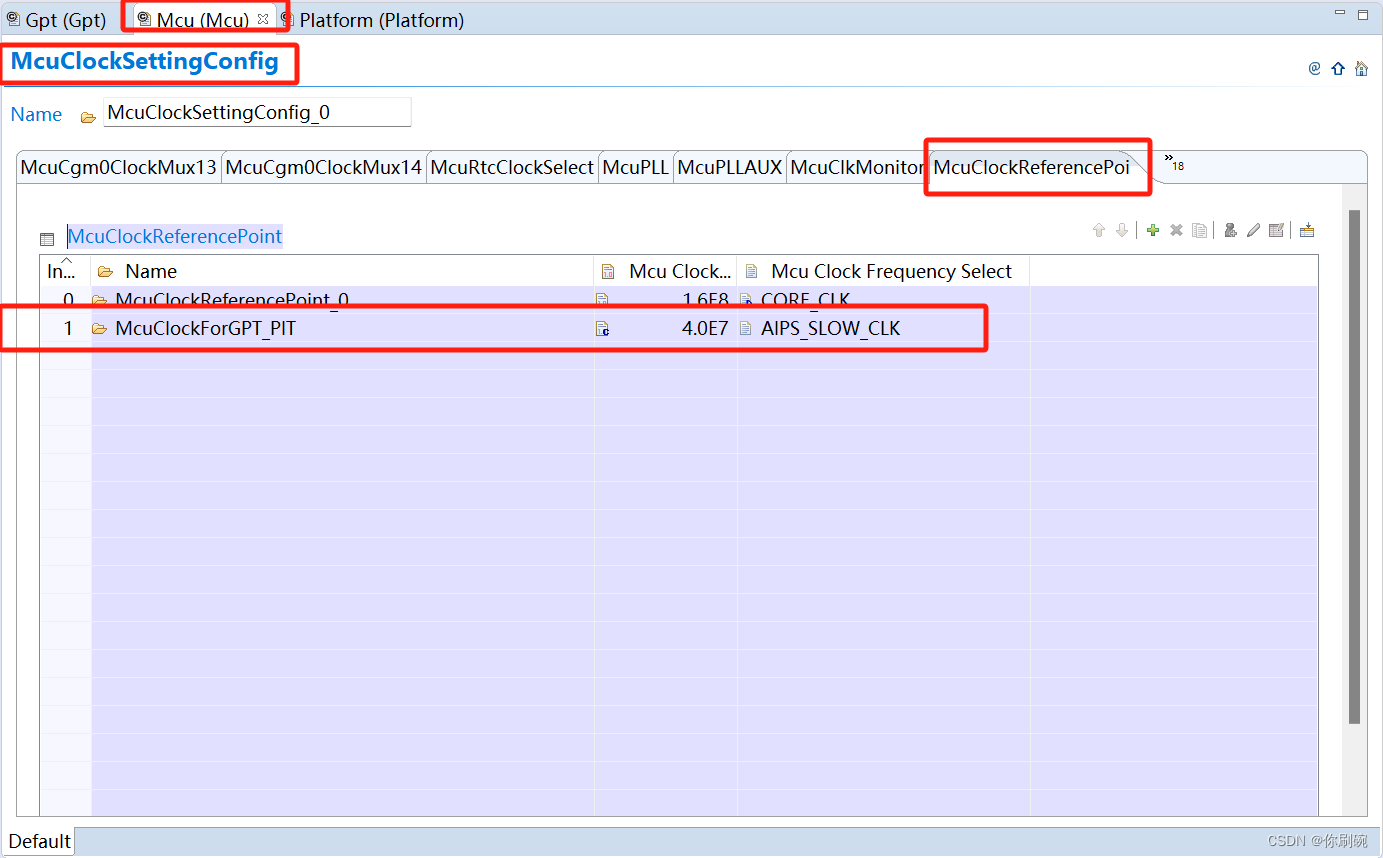

根据手册,可以看到PIT0的时钟源有:AIPS_SLOW_CLK、SIRC_CLK

PIT0选择AIPS_SLOW_CLK,在MCU中可以看到AIPS_SLOW_CLK的时钟为80MHz,分频系数需要+1作为最终的分频系数,即填2表示分频系数为3,填0表示分频系数为1.因此可以看到AIPS_PLAT_CLK的最终时钟为40MHz。

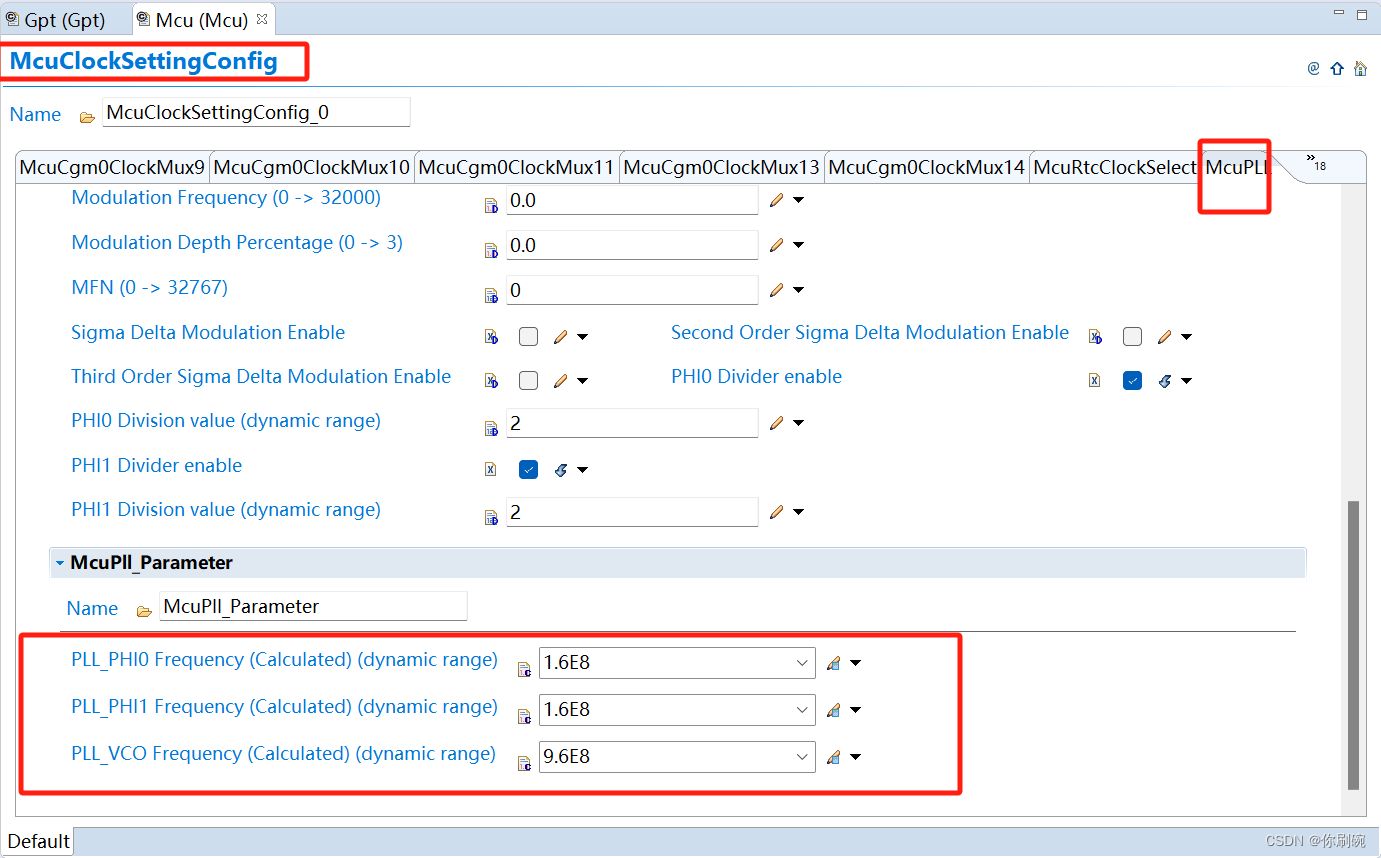

当然更上一级的时钟如PLL_PHI0、PLL_PHI1、PLL_VCO等只在MCUPLL中配置,相关信息已在MCU文章中配置好,此处不做赘述。如下图所示:

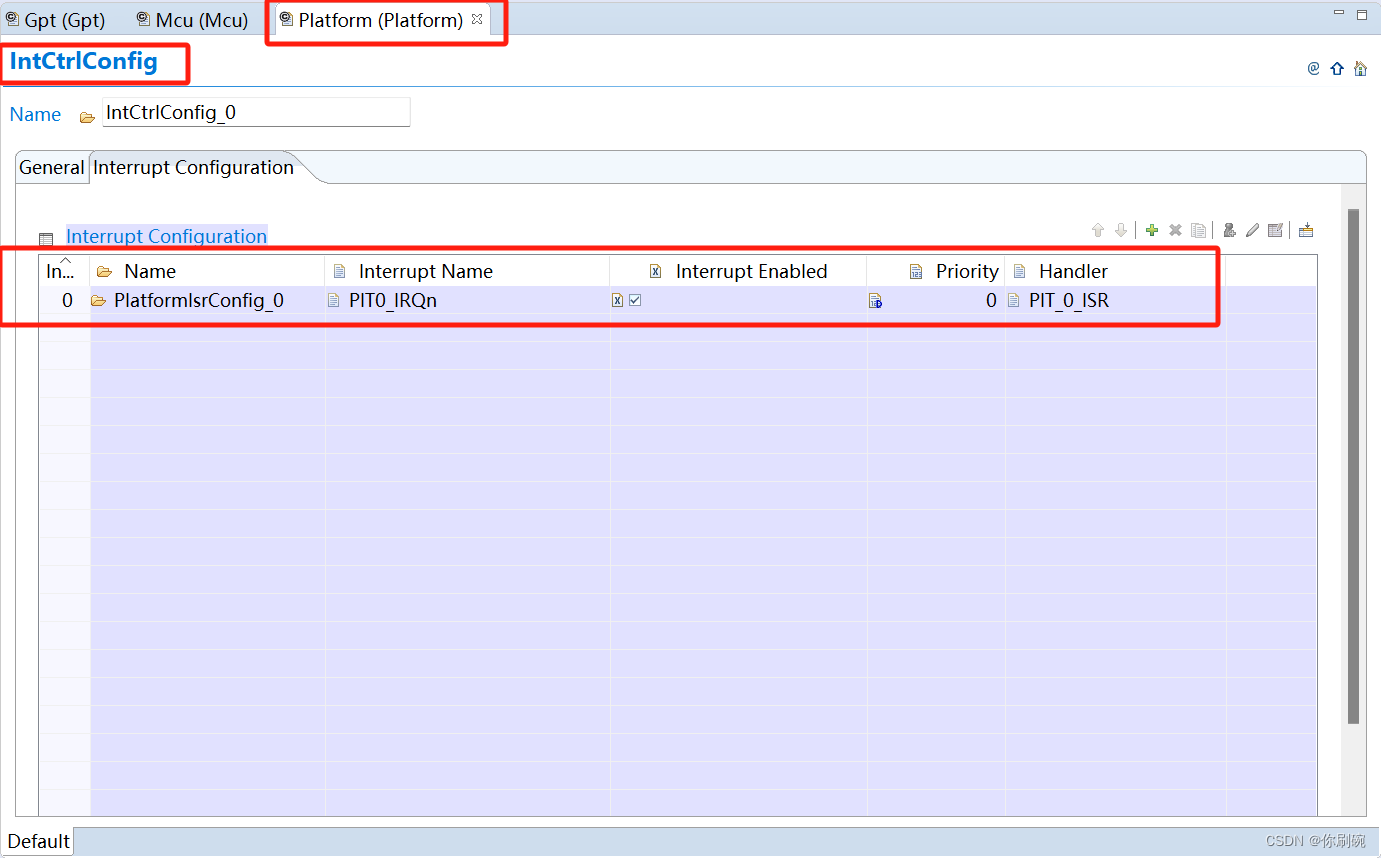

1.4 Platform配置

使能pit0的中断,添加相应的中断处理函数:

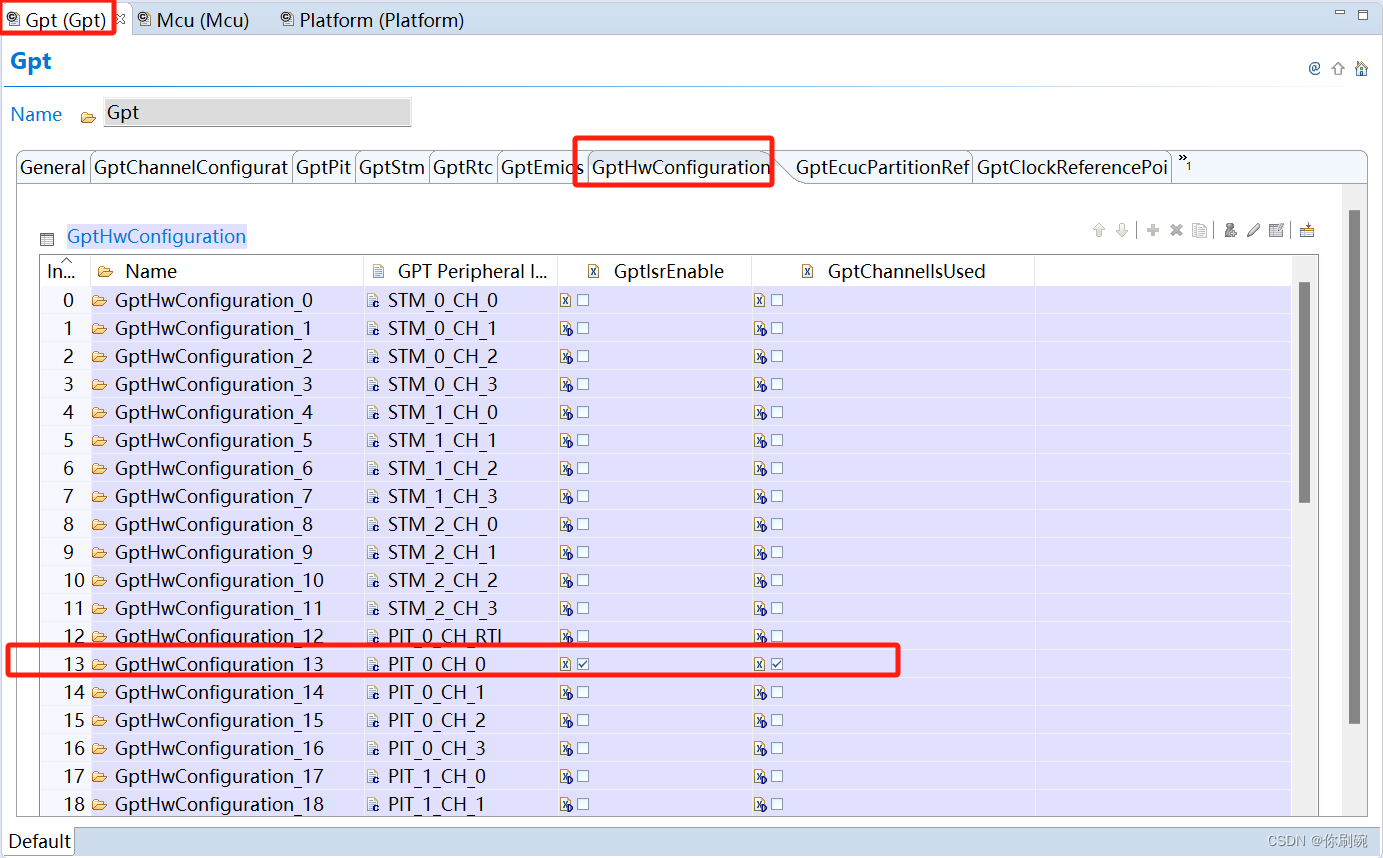

1.5 GPT配置

1.5.1 使能定时器通道和中断

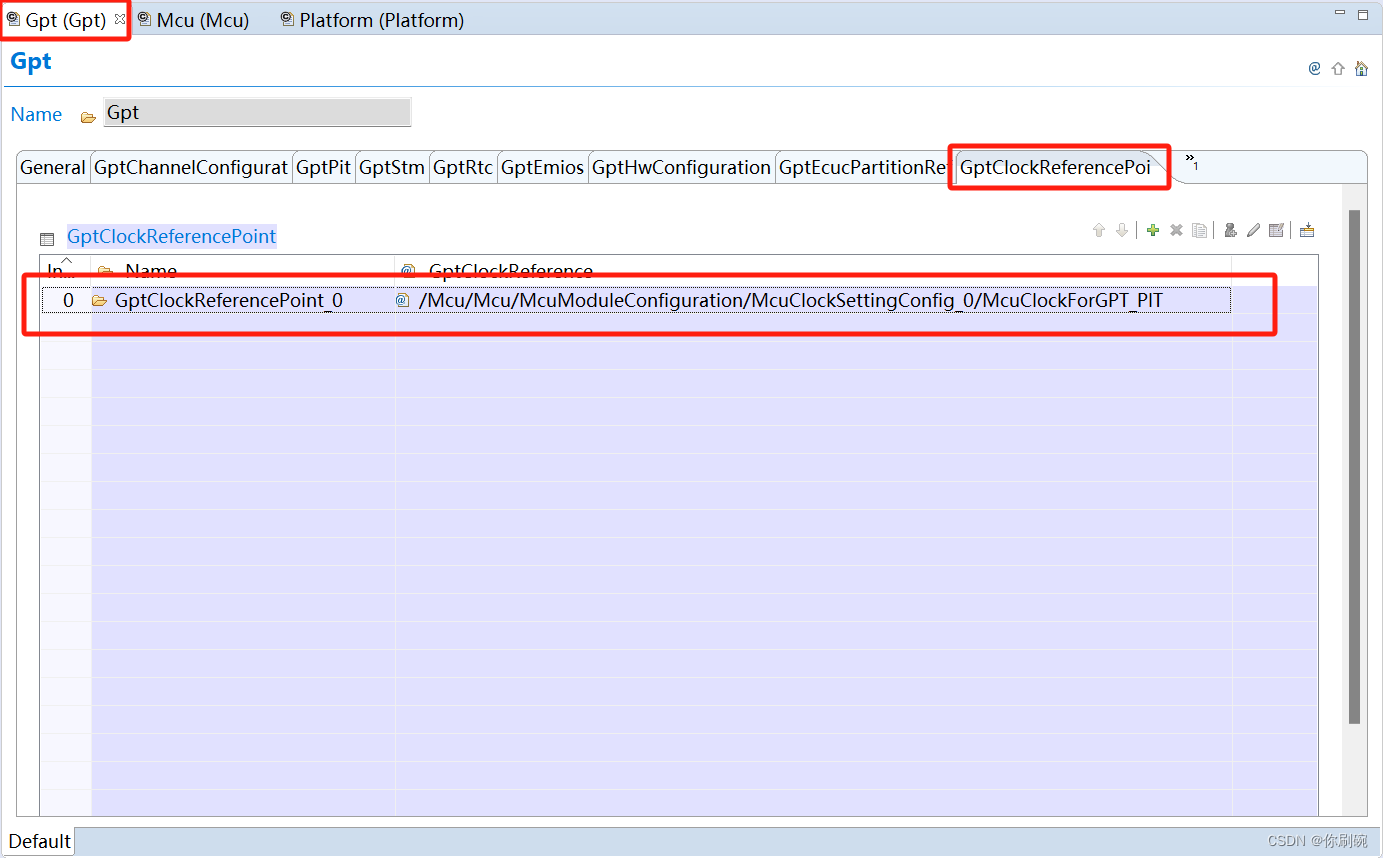

1.5.2 配置Gpt参考时钟

参考时钟来源是MCU时钟配置的Reference:

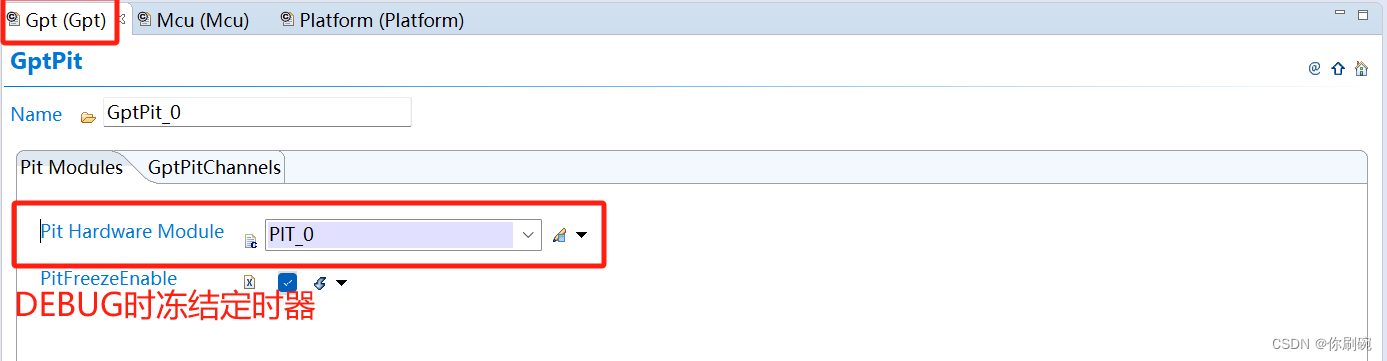

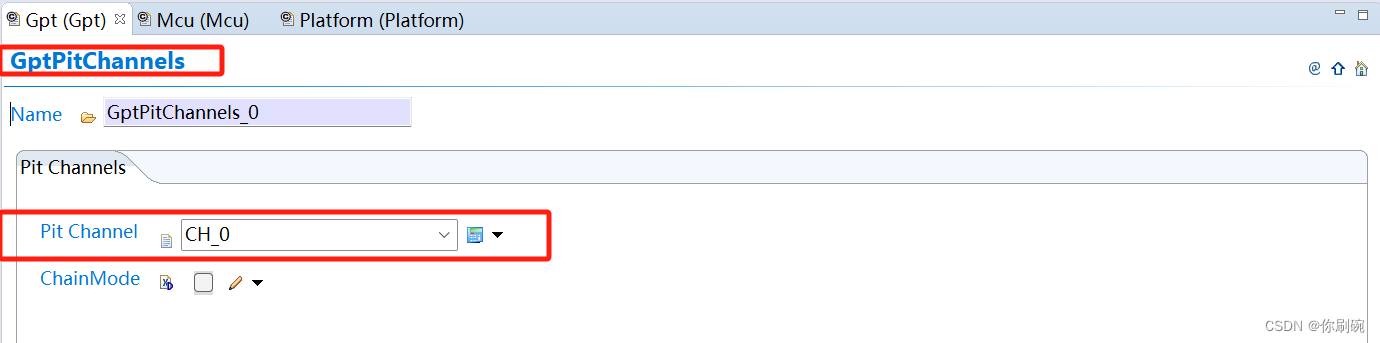

1.5.3 配置GptPIT

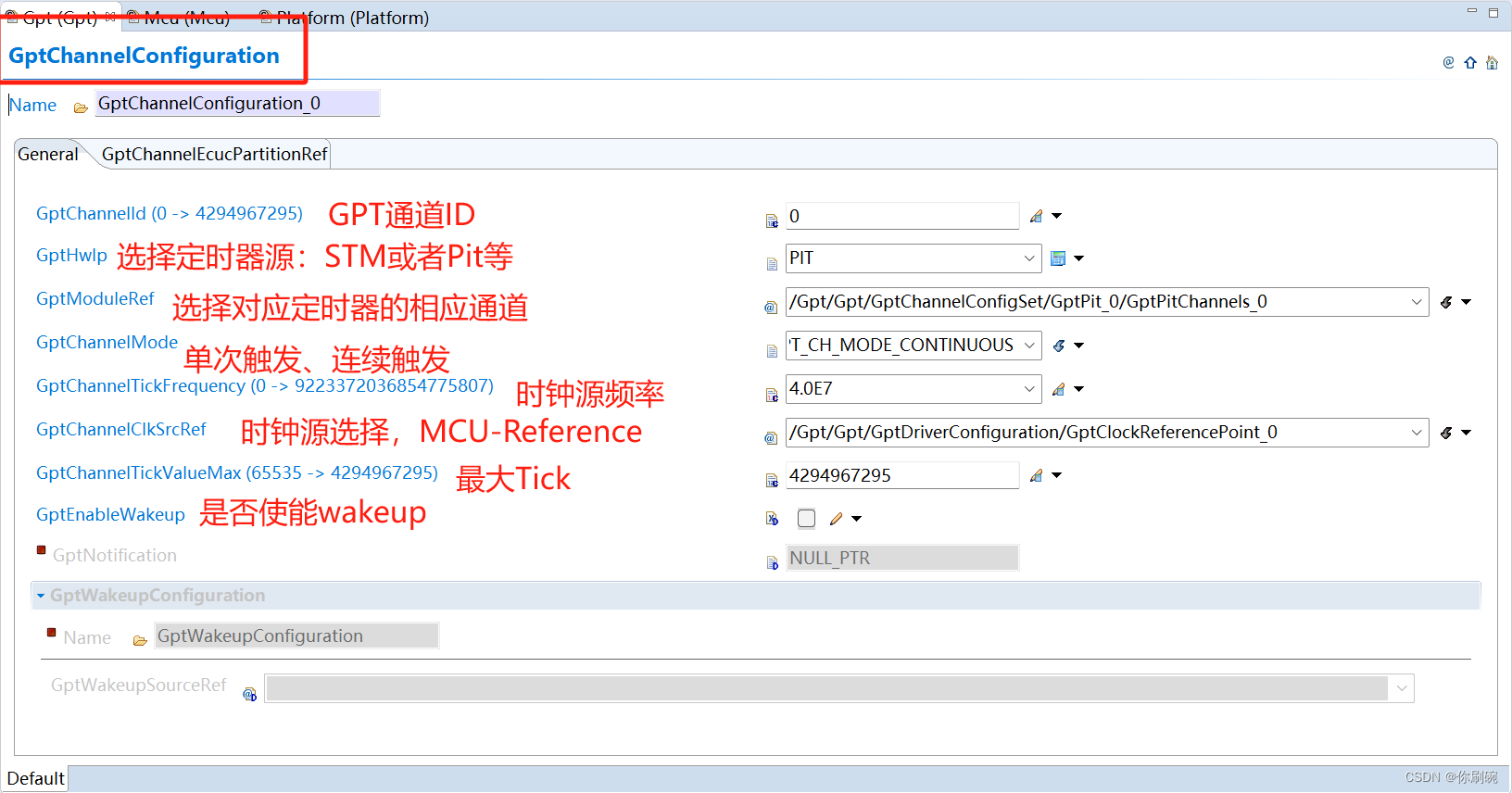

1.5.4 GptChannelConfiguration配置

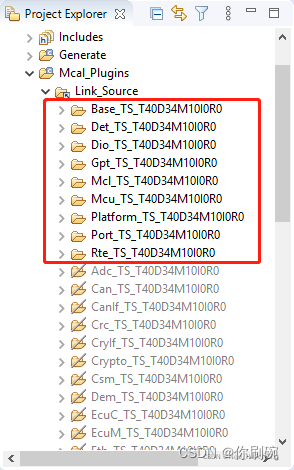

2.1 s32ds配置

tips:这部分工作我并未做,借鉴何飞阳。

添加相应的驱动模块:

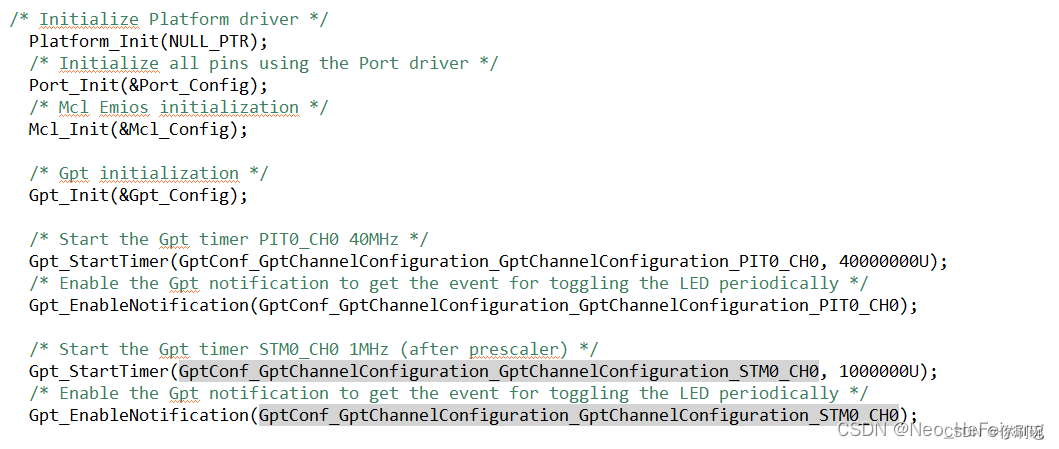

Main函数中进行相关模块初始化,开启对应通达的定时器,使能相关回调函数。

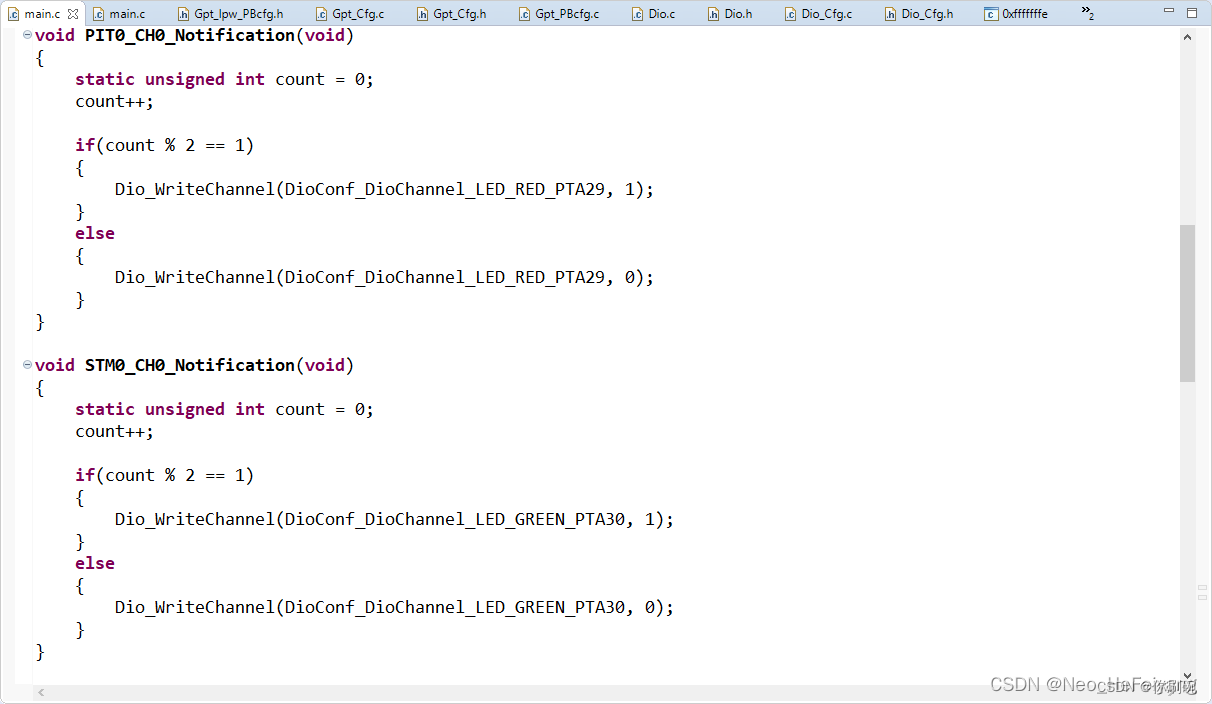

根据EB的配置,编写相应的回调函数:

408

408

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?